Fターム[5F048BD10]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 複数MOS間のチャネル長(幅) (608)

Fターム[5F048BD10]に分類される特許

61 - 80 / 608

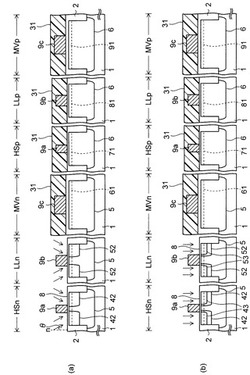

半導体装置の製造方法

【課題】相互に特性が異なる複数種類のMOSトランジスタを有する半導体装置の製造方法において、工程数を削減でき、製品コストの増加を抑制する。

【解決手段】高速トランジスタ形成領域HSn、低リークトランジスタ形成領域LLn及び中電圧トランジスタ形成領域MVnにゲート電極9a,9b,9cを形成する。その後、トランジスタ形成領域MVnを覆うフォトレジスト膜31を形成する。そして、フォトレジスト膜31及びゲート電極9a,9bをマスクとして半導体基板1に不純物をイオン注入し、p型ポケット領域42,52、エクステンション領域43及び不純物領域53を形成する。次いで、トランジスタ形成領域HSnを覆うフォトレジスト膜を形成する。そして、このフォトレジスト膜、ゲート電極9b,9cをマスクとして半導体基板1に不純物をイオン注入し、不純物領域及びエクステンション領域を形成する。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いて、トランジスタのしきい値電圧を変化させる。

【解決手段】第1のチャネル形成領域を有する第1の半導体層と、第2のチャネル形成領域を有する第2の半導体層に対して、それらの上に形成された薄膜の応力を用いて、トランジスタのしきい値電圧を異ならせることができる。これらを電気的に接続することで、E/D MOS回路を提供できる。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率の絶縁膜を有するnチャネル型トランジスタやpチャネル型トランジスタを有する半導体装置の製造方法において、nチャネル型トランジスタのゲート絶縁膜の側面への異物の付着を抑制する。

【解決手段】半導体基板の主表面上の、p型不純物領域PWLに機能用nチャネル型トランジスタが、n型不純物領域NWLに機能用pチャネル型トランジスタが形成される。p型不純物領域PWLの、平面視における機能用nチャネル型トランジスタ以外の領域に形成される複数の第1の周辺用トランジスタは、周辺用n型ゲート構造体と周辺用p型ゲート構造体とが混在するように形成される。

(もっと読む)

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数やコストを増加させることなく、信頼性の高い高耐圧pチャネル型トランジスタが形成された半導体装置を提供する。

【解決手段】主表面を有し、かつ内部にp型領域を有する半導体基板SUBと、p型領域PSR上であって主表面に配置された、ドレイン電極DRを取り出すための第1のp型不純物領域PRを有するp型ウェル領域PLDと、主表面に沿う方向に関してp型ウェル領域PLDと接するように配置された、ソース電極SOを取り出すための第2のp型不純物領域PRを有するn型ウェル領域NWRと、主表面に沿う方向に関して、第1のp型不純物領域PRと第2のp型不純物領域PRとの間に配置されたゲート電極GEと、n型ウェル領域NWRの上に配置された、主表面に沿って延びるp型埋め込みチャネルPPRとを含んでいる。上記n型ウェル領域NWRとp型ウェル領域PLDとの境界部は、ゲート電極GEの、第1のp型不純物領域PRに近い側の端部よりも、第1のp型不純物領域PRに近い位置に配置される。

(もっと読む)

半導体装置

【課題】複数の有機EL素子への供給電流ばらつきを低減する。

【解決手段】有機EL素子50と電源ラインVLとの間に、電源ラインVLから供給する電流量を制御する素子駆動用TFT20を備え、TFT20のチャネル長方向を、画素の長手方向、又はTFT20を制御するスイッチング用TFT10にデータ信号を供給するデータラインDLの延在方向、又はTFT20の能動層16を多結晶化するためのレーザアニールの走査方向に平行な方向に配置する。さらに電源ラインVLとTFT20の間にTFT20と逆特性の補償用TFT30を備えていても良い。

(もっと読む)

金属ゲート電極を有する半導体素子の製造方法

【課題】 収率が低下することなくCMOS集積回路の特性を最適可能な半導体素子の製造方法を提供する。

【解決手段】 半導体基板1の上の第1領域A内及び第2領域B内に各々形成された第1グルーブ15a及び第2グルーブ15bを有する層間絶縁膜15を形成する。次に、半導体基板1上に積層金属膜22を形成し、積層金属膜22上に非感光性を有する平坦化膜23を第1グルーブ15a及び第2グルーブ15bを充填するように形成する。第1領域A内の平坦化膜23を乾式エッチングによって選択的に除去し、第1領域A内の積層金属膜22を露出させ、第2領域B内の積層金属膜22を覆う平坦化膜パターン23pを形成する。これにより、第1領域A内の最上部金属膜を容易に除去することができるので、収率が低下することなく異なる仕事関数を有する第1金属ゲート電極及び第2金属ゲート電極を形成できる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】同一基板上にゲート絶縁膜が厚いMOSトランジスタと薄いMOSトランジスタとを有する半導体装置の新規な製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の第1活性領域上に第1ゲート絶縁膜を、第2活性領域上にそれより薄い第2の膜厚の第2ゲート絶縁膜を酸化シリコンを含む材料で形成する工程と、第1及び第2ゲート絶縁膜を覆うポリシリコン膜をパターニングして第1及び第2ゲート絶縁膜上それぞれに第1及び第2ゲート電極を形成する工程と、第1及び第2ゲート電極を覆う絶縁膜を異方性エッチングして第1及び第2ゲート電極の側面にサイドウォール絶縁膜を残す工程と、第1ゲート電極側面上のサイドウォール絶縁膜を除去する工程と、第1ゲート電極の側面上のサイドウォール絶縁膜が除去された半導体基板を酸化雰囲気中で熱処理する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板上の所定の領域内の窒化膜を、当該領域へのダメージを抑制しつつ選択的に除去することにより、信頼性の高い半導体装置を実現する。

【解決手段】半導体装置の製造方法は、半導体基板上の第1領域の全域を覆い、第2領域内の所定領域を覆う窒化膜を形成する工程と、窒化膜の全表面に酸化皮膜を形成する酸化皮膜形成工程と、この後、第1領域上を被覆し、第2領域上の所定の酸化膜形成対象領域を被覆しないパターンのレジスト膜を前記窒化膜上に形成する工程と、ふっ酸液によるウェットエッチングによって、酸化膜形成対象領域の窒化膜の表面に形成された酸化皮膜を選択的に除去して前記窒化膜を露出させるふっ酸エッチング工程と、レジスト膜を剥離する工程と、高温のリン酸液によって露出した窒化膜を除去する工程と、窒化膜が除去された酸化膜形成対象領域の基板表面に熱酸化による酸化膜を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細構造を有する半導体装置において、ゲート長の最適化が可能な半導体装置を提供する。

【解決手段】基体上に形成された高誘電率材料からなるゲート絶縁膜15と、ゲート絶縁膜15上に形成されたメタルゲート電極と、メタルゲート電極の側壁に形成されたサイドウォールスペーサ21とを備える半導体装置10を構成する。そして、第1導電型のトランジスタ及び第2導電型のトランジスタのいずれか一方にメタルゲート電極側壁とサイドウォールスペーサ21内壁との間に形成されたオフセットスペーサ19が形成される。或いは、第1導電型のトランジスタと第2導電型のトランジスタとに、厚さの異なるオフセットスペーサ19が形成される。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

電子装置及び電子装置の作製方法

【課題】信頼性及び色再現性の高い電子装置を提供する。

【解決手段】単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離領域のエッチングを生じさせることなく、基板上にサイドウォール幅が異なる複数のトランジスタを精度良く形成できるようにする。

【解決手段】

半導体装置の製造方法において、まず第1のゲート電極134及び第2のゲート電極144を覆うように、第1の絶縁膜151及び第2の絶縁膜152を順次形成する。この後、第2の絶縁膜152における第1の領域103の上に形成された部分を除去する。この後、基板101の上に第3の絶縁膜153を形成する。この後、第2の絶縁膜152及び第3の絶縁膜153を選択的に除去することにより、第1のゲート電極134の側面上に第3の絶縁膜153からなる第1の外側サイドウォール136を形成し、第2のゲート電極144の側面上に第2の絶縁膜152及び第3の絶縁膜153からなる第2の外側サイドウォール146を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2の不純物層及び第1のエピタキシャル半導体層よりも薄い第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル不純物の拡散を抑制し、高性能・高信頼性を実現しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板第1及び第2の領域に非晶質化のためのイオン注入を行い、第1の領域及び第2の領域に第1の不純物及び第2の不純物をそれぞれイオン注入し、注入した不純物を活性化して第1の不純物層及び第2の不純物層を形成し、不純物層を形成した半導体基板上に半導体層をエピタキシャル成長し、第1及び第2の領域上にゲート絶縁膜を成長し、第1及び第2のゲート絶縁膜上に第1及び第2のゲート電極をそれぞれ形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1,第2のゲート電極の実効ゲート長が短くなることを防止する。

【解決手段】第1のMISトランジスタnTr1は、第1のゲート電極18aにおけるゲート幅方向の側面上に形成された第1のオフセットサイドウォール22aと、第1のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第1のオフセットサイドウォールを介して形成された第2のオフセットサイドウォール24aと、第1のエクステンション領域26aとを備えている。第2のMISトランジスタnTr2は、第2のゲート電極18bにおけるゲート長方向の側面及びゲート幅方向の側面上に形成された第3のオフセットサイドウォール22bと、第2のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第3のオフセットサイドウォールを介して形成された第4のオフセットサイドウォール24bと、第2のエクステンション領域23bとを備えている。

(もっと読む)

61 - 80 / 608

[ Back to top ]