Fターム[5F048BD10]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 複数MOS間のチャネル長(幅) (608)

Fターム[5F048BD10]に分類される特許

101 - 120 / 608

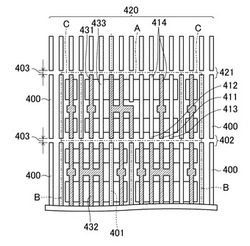

半導体装置及びそのレイアウト作成方法

【課題】半導体装置及びその製造方法において、ゲート電極部の幅及びゲート電極部からの突き出し長のばらつきを低減する。

【解決手段】半導体装置は、ゲート電極部及び突き出し部を有する実パターン431と、実パターン431に並んで配置されるダミーパターン433とを含む複数のラインパターンを備える。2つのダミーパターン433と、これらに挟まれ且つ実パターン432を含むラインパターンとにより、同一間隔を空けて並走するラインパターン並走部が構成される。ラインパターン並走部の各ラインパターンは、同一の幅を有すると共に、互いに実質的に面一なライン終端部414を有する。各ライン終端部414の延長線上に、同一の終端部間距離403を空けて、ライン終端部均一化ダミーパターン420が形成される。ライン終端部均一化ダミーパターン420は、ラインパターンと同一幅で且つ同一間隔に形成された複数のライン状のパターンを含む。

(もっと読む)

半導体集積回路の設計方法

【課題】フォトリソグラフィ工程で生じる光近接効果に起因するゲート長のばらつきとゲートの寄生容量のばらつきを抑制し、標準セルの実際の特性を反映させたライブラリを設計可能とし、これにより設計マージンを小さくして高性能な半導体集積回路を提供する。

【解決手段】標準セルSc1を配列して半導体集積回路を設計する方法において、標準セルSc1を構成するゲートパターン5の端部に、該ゲートパターン5と垂直な方向にダミーパターン3を配置し、該ダミーパターン3の配置により、ゲートパターン5の端部での該ゲートパターンの占有密度の低下を補う。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

シリコン・オン・インシュレータ構造において電界効果トランジスタを備える半導体デバイス

【課題】シリコン・オン・インシュレータ構造において複数電界効果トランジスタを備える新規な半導体デバイスを提供する。

【解決手段】基板200と、基板上の酸化物層190と、酸化物層上の半導体層230を備えるSOI構造の電解効果トランジスタと、半導体・オン・インシュレータ構造(SeOI構造)のFETであって、基板内にチャンネル領域200を備え、前記FET構造のBOX構造酸化物層190の少なくとも一部である誘電体をゲート誘電体とし、基板200をチヤネルとする半導体デバイス。

(もっと読む)

半導体装置の設計方法及び製造方法

【課題】トランジスタ等の電気的特性のばらつきを低減し得る半導体装置の設計方法及び半導体装置の製造方法を提供する。

【解決手段】素子領域の実パターンである複数の第1の実パターンと、ゲート配線の実パターンである複数の第2の実パターンとを配置するステップと、レイアウト領域を複数の分割領域に分割するステップと、レイアウト領域内に、ダミーの素子領域のパターンである複数の第1のダミーパターンと、ダミーのゲート配線のパターンである複数の第2のダミーパターンとを配置するステップであって、分割領域内における第1の実パターン、第2の実パターン、第1のダミーパターン及び第2のダミーパターンの周囲長の総和の、分割領域間におけるばらつきが、所定の範囲内となるように、第1のダミーパターン及び第2のダミーパターンを配置する。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、製造歩留まりを向上できる技術を提供する。

【解決手段】給電領域に位置するCGシャント部の選択ゲート電極CGの半導体基板1の主面からの第2高さd2が、メモリセル形成領域の選択ゲート電極CGの半導体基板1の主面からの第1高さd1よりも低くなるように、CGシャント部の選択ゲート電極CGを形成する。

(もっと読む)

半導体装置

【課題】高さの異なる複数の素子形成面に形成された半導体素子の電気特性を均一化する。

【解決手段】半導体装置Sは、高さの異なる複数の素子形成面50が段差状に形成された半導体層1と、素子形成面50を含む各領域にそれぞれ形成された半導体素子51,52と、半導体層1に対し、半導体素子51,52を覆うと共に素子形成面50に沿った段差状の表面を有する段差補償絶縁膜28とを備えている。そして、各素子形成面50における半導体層1は、互いに同じ厚みに形成されている。

(もっと読む)

カーボンナノチューブ電界効果トランジスタを含む集積回路、およびその製造方法

【課題】カーボンナノチューブ電界効果トランジスタを含む集積回路であって、その製造プロセスにプラズマ環境下での工程が含まれていても、優れた特性のカーボンナノチューブ電界効果トランジスタを維持する手段を提供する。

【解決手段】1の半導体基板上に配置された、電界効果トランジスタと、MOSトランジスタと、前記電界効果トランジスタと前記MOSトランジスタとを接続するメタル配線と、を含む集積回路であって:前記電界効果トランジスタは、ゲート絶縁膜と、前記ゲート絶縁膜上に形成されたカーボンナノチューブを含むチャネルと、前記カーボンナノチューブを被覆する絶縁保護膜と、前記絶縁保護膜上であって前記チャネルを覆う領域に配置された金属膜と、前記チャネルに接続されたソース電極およびドレイン電極と、前記チャネルを制御可能なゲート電極とを有し、ここで前記メタル配線は、プラズマエッチング法により形成された配線である、集積回路。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数の増加を回避し得る半導体装置及びその製造方法を提供する。

【解決手段】低濃度ドレイン領域28hを形成するためのドーパント不純物が導入される所定領域を除く領域に、所定領域から離間するようにチャネルドープ層22dを形成する工程と、半導体基板10上にゲート絶縁膜24を介してゲート電極26dを形成する工程と、ゲート電極の一方の側の半導体基板内に低濃度ソース領域28gを形成し、ゲート電極の他方の側の半導体基板の所定領域に低濃度ドレイン領域28hを形成する工程とを有している。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】ドレイン耐圧を向上させる半導体装置及びその製造方法を提供すること。

【解決手段】基板100表面内に第1、第2拡散層206を形成する工程と、前記基板上に第1トランジスタを形成する工程と、前記ゲート電極の第1側壁及び第2側壁にそれぞれ第1、第2絶縁膜202を形成することにより、前記第1、第2拡散層の表面の一部の領域を被覆する工程と、この第2拡散層上に第3絶縁膜203を形成する工程と、前記第1〜第3絶縁膜、ゲート電極201、及び前記基板表面をそれぞれ第4絶縁膜204で被覆する工程と、前記ゲート電極の表面、及び第3絶縁膜に対して前記第2絶縁膜と前記第3絶縁膜との間の第1領域と相対する第2領域における前記第2拡散層の表面を露出しつつ、前記第1領域における前記第2拡散層の表面が露出しないよう前記第4絶縁膜を除去する工程とを具備する。

(もっと読む)

半導体装置

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便な製造方法によって製造された良好なTFT特性を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、絶縁基板11と、絶縁基板11に支持されたチャネル領域33A、ソース領域34Aおよびドレイン領域35Aを含む半導体層30Aと、チャネル領域33Aの導電性を制御するゲート電極51とを有する。半導体層30Aは、チャネル領域33Aとソース領域34Aとの間に形成された第1低濃度領域31A、および、チャネル領域33Aとドレイン領域35Aとの間に形成された第2低濃度領域32Aとを有する。チャネル領域33A、第1および第2低濃度領域31Aおよび32Aは、ソースおよびドレイン領域34Aおよび35Aの不純物濃度より低い第1不純物濃度を有する。ゲート電極51は、第1および第2低濃度領域31Aおよび32Aの全部を覆うように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】質量数が比較的小さいドーパント不純物を導入することにより第1のトランジスタ34a及び第2のトランジスタ34bのチャネルドープ層18を形成する工程と、質量数が比較的大きいドーパント不純物を導入することにより第3のトランジスタ34cのチャネルドープ層20を形成する工程と、質量数の比較的小さいドーパント不純物を導入することにより第1のトランジスタのポケット領域26を形成する工程と、質量数の比較的大きいドーパント不純物を導入することにより第2のトランジスタ及び第3のトランジスタのポケット領域36を形成する工程とを有している。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOSトランジスタにおいて、オン抵抗とのトレードオフ関係で最適化されたオフ耐圧を低下させることなく、チャネル長を短くすることによって飽和電流を増加させる。

【解決手段】 チャネルとなる低濃度ボディ領域10と素子分離膜4の間かつゲート酸化膜8の直下に選択的に低濃度ボディ領域10と逆の極性で濃度が高いショートチャネル領域12を設け、ボディ領域10のゲート酸化膜8直下部分のみを高濃度ソース領域7側に後退させた形状を実現する。

(もっと読む)

半導体装置

【課題】異なる電源系統から電源電圧を供給される出力回路と入力回路とを含む半導体装置において、ESDサージ電圧が出力回路を介して入力回路にそのまま印加されることによって入力回路が破壊されることを有効に抑制する。

【解決手段】半導体装置が、第1電源パッド11と、第1接地パッド12と、第1電源線13と、第1接地線14と、出力回路15と、第2電源パッド21と、第2接地パッド22と、第2電源線23と、第2接地線24と、入力回路25と、信号線20と、メインESD保護素子16と、保護ダイオード対D1と、PMOSトランジスタP2とを備えている。出力回路15がPMOSトランジスタP3を含み、入力回路25がNMOSトランジスタN1を含む。PMOSトランジスタP2は、ソースが信号線20に接続され、ドレインが第2接地線24に接続され、ゲートとバックゲートが第2電源線23に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コスト削減、サイズ縮小ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法であって、P型Si基板21の主面にトレンチ22を形成することによって、エンハンスメント型FET形成用の幅狭部分とでプレション型FET形成用の幅広部分とを含むアクティブ領域25を形成する工程と、主面の法線に対して30度〜45度の範囲内の注入角で、且つ、注入方向が法線を中心に相対的に回転するように、Si基板21に対してP型不純物を注入して、幅広部分にP型のチャンネルストッパー領域25aを形成すると共に、幅狭部分にP型チャンネル拡散領域25bを形成する工程と、トレンチ22をトレンチ素子分離絶縁層26で埋める工程と、ゲート絶縁膜27を形成する工程と、Si基板21上にN型不純物を注入して第2の部分にN型チャンネル拡散領域28を形成する工程と、ゲート電極29を形成する工程とを有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

101 - 120 / 608

[ Back to top ]