Fターム[5F048BF06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 材料 (4,535) | シリサイド (1,808)

Fターム[5F048BF06]に分類される特許

1,661 - 1,680 / 1,808

CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成するための方法

【課題】 位置ずれの問題を克服する新規のデュアルFUSIゲート形成プロセスを提供する。

【解決手段】 1つのリソグラフィ段階しか必要としない、CMOSデバイスにおいて自己整合デュアル・フルシリサイド・ゲートを形成する方法であり、本方法は、半導体基板(252)の中の第1のウェル領域(253)、第1のウェル領域(253)の中の第1のソース/ドレイン・シリサイド・エリア(266)、及び第1のソース/ドレイン・シリサイド・エリア(266)から分離された第1のタイプのゲート(263)を有する第1のタイプの半導体デバイス(270)を形成するステップと、半導体基板(252)の中の第2のウェル領域(254)、第2のウェル領域(254)の中の第2のソース/ドレイン・シリサイド・エリア(256)、及び第2のソース/ドレイン・シリサイド・エリア(256)から分離された第2のタイプのゲート(258)を有する第2のタイプの半導体デバイス(280)を形成するステップと、第2のタイプの半導体デバイス(280)の上に第1の金属層(218)を選択的に形成するステップと、第2のタイプのゲート(258)のみの上で第1のフルシリサイド(FUSI)ゲート形成を行うステップと、第1及び第2のタイプの半導体デバイス(270、280)の上に第2の金属層(275)を堆積させるステップと、第1のタイプのゲート(263)のみの上で第2のFUSIゲート形成を行うステップとを含む。

(もっと読む)

半導体装置

【課題】半導体装置の放熱性を向上させ、素子で生じた熱が特定の回路に伝達され難くする。

【解決手段】半導体装置は、第1素子分離絶縁膜41と、それにより熱伝導率の低い第2素子分離絶縁膜42とを備えている。熱の伝達を抑制したいMOSトランジスタT1とMOSトランジスタT2との間には、熱伝導率の低い第2素子分離絶縁膜42を配設し、それ以外の素子間には第1素子分離絶縁膜41を配設する。

(もっと読む)

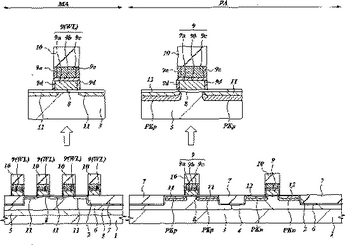

半導体装置およびその製造方法

【課題】 信頼性の高いフルシリサイドMOSFETおよびシリサイドMOSFETを従来よりも簡単に同一基板上に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に第1のゲート電極40および第2のゲート電極42を形成し、第1のゲート電極および第2のゲート電極上にマスク材料90を堆積し、第2のゲート電極を被覆したまま第1のゲート電極の上面を露出させるようにマスク材料をパターニングし、マスク材料を利用して第1のゲート電極の上部をエッチングし、マスク材料を除去し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の上部をシリサイド化することを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】 様々なパターンを有するゲート電極をフルシリサイド化することができる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に、第1のゲート電極40および第1のゲート電極よりもゲート長またはゲート幅が大きい第2のゲート電極40を形成し、第2のゲート電極の厚みが第1のゲート電極の厚みよりも薄くなるように第2のゲート電極の上部を選択的にエッチングまたは研磨し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の全部をシリサイド化することを具備している。

(もっと読む)

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

スケーラブル集積論理および不揮発性メモリ

スケーラブル論理トランジスタはドレインおよびソースのための一組のドープされた領域を有する。ゲート絶縁層は基板上でドレイン領域とソース領域の間に形成される。ゲートスタックは、ポリシリコンや金属のようなゲート層を、二つの窒化金属層の間に置くことで形成される。また、埋め込まれた金属ナノドット層を有する高K誘電率膜を、トンネル絶縁層とゲートスタックとの間に設けるようにして付加することによって、この基本的構成から互換性のある不揮発性メモリトランジスタを形成することもできる。 (もっと読む)

半導体のための引張り及び圧縮応力をもたせた物質

応力をもたせた膜が基板上に形成される。基板が処理ゾーンに置かれ、処理ゾーンに与えられたシリコン含有ガス及び窒素含有ガスを有する処理ガスのプラズマが形成される。窒素の如き希釈ガスを加えることもできる。堆積直後のままの応力をもたせた物質を、紫外線又は電子ビームに対して露出させることにより、その堆積物質の応力値を増大させることができる。それに加えて、又はそれとは別に、堆積中にその物質の応力値を増大させるために、窒素プラズマ処理を使用することができる。応力をもたせた物質を堆積させるためのパルス化方法も開示する。 (もっと読む)

半導体構造およびそれを形成する方法(金属酸化物の付着を介して形成されたしきい電圧制御層を含む窒素含有電界効果トランジスタ・ゲート・スタック)

【課題】 ゲート誘電体とゲート電極との間にVt安定化層を含む半導体構造を提供することにある。

【解決手段】 Vt安定化層は、構造のしきい電圧およびフラットバンド電圧を目標値に安定化することができ、窒化金属酸化物または窒素なし金属酸化物を含み、Vt安定化層が窒素なし金属酸化物を含む条件で半導体基板またはゲート誘電体のうちの少なくとも一方が窒素を含む。また、本発明は、このような構造を形成する方法も提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、ゲート電極の空乏化を抑制すると共に、シリサイドの高抵抗化を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】 ゲート絶縁膜上に、所定の半導体材料とゲルマニウムとを含む膜を形成するステップと、膜を酸化することにより、ゲート絶縁膜上に、当該膜よりもゲルマニウム濃度が高くかつ膜厚が薄い第1の膜を形成すると共に、第1の膜上に酸化膜を形成するステップと、酸化膜を除去するステップと、第1の膜上に、半導体材料を含み、第1の膜よりもゲルマニウム濃度が低い第2の膜を形成するステップと、第2の膜及び第1の膜にエッチングを行うことにより、ゲート電極を形成するステップとを備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 スパイラルインダクタが設けられた半導体装置の製造安定性を向上させる。

【解決手段】 半導体装置100は、シリコン基板101、シリコン基板101中に埋設された素子分離酸化膜、シリコン基板101上に設けられた第一層間絶縁膜、第一層間絶縁膜上に設けられたスパイラルインダクタ120、およびスパイラルインダクタ120とシリコン基板101との間に設けられ、基板面内方向に延在してスパイラルインダクタ120とシリコン基板101との間を遮蔽するシールド層を有する。そして、平面視において、素子分離酸化膜中にシリコン基板101が島状に残存してなる基板残存領域131が、スパイラルインダクタ120の形成領域においてはポリシリコン105の直下に選択的に複数設けられている。

(もっと読む)

半導体装置

【課題】浅い高濃度のソース・ドレイン層を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコンからなる表面領域を持つ基板、表面領域上に形成されたゲート絶縁膜、ゲート絶縁膜上に形成されたゲート電極、ゲート電極の両側に設けられた側壁絶縁膜、側壁絶縁膜下からその外側に向かった部分の基板表面に形成された溝内に不純物を含むシリコン膜を堆積して形成された埋め込み形成型のソースおよびドレイン層を具備し、溝の底部のシリコン膜の不純物濃度は1×1019〜1×1022cm-3、かつ、溝の深さ方向に沿ったシリコン膜の不純物濃度は一定であり、かつ、埋め込み型形成型のソースおよびドレイン層は、側壁絶縁膜下に形成された第1の埋め込み形成型のソースおよびドレイン層、側壁絶縁膜外側に形成され、第1の埋め込み形成型のソースおよびドレイン層よりも厚い第2の埋め込み型形成型のソースおよびドレイン層を含む。

(もっと読む)

半導体装置の製造方法

【課題】 素子分離膜形成のエッチング処理において、エッチング液として燐酸を使用せずに、低コストで半導体装置の製造方法を提供する。

を提供する。

【解決手段】 半導体装置の製造方法は、基板30上に第1絶縁層34を形成する第1絶縁層形成工程と、第1絶縁層上に第2絶縁層38を形成する第2絶縁層形成工程と、基板、第1絶縁層34及び第2絶縁層38の一部を除去して凹部H1を形成する凹部形成工程と、凹部H1を含む第2絶縁層38上に撥液性を有する第3絶縁層36を形成する第3絶縁層形成工程と、第3絶縁層36の一部を除去して第2絶縁層38を露出させ、第2絶縁層38及び第3絶縁層36上を平坦化する平坦化工程と、ウェットエッチング処理により、第2絶縁層38を除去する第2絶縁層除去工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 未反応の高融点金属膜等を確実にエッチング除去することが可能な半導体装置の製造方法を提供する。

【解決手段】 ソース/ドレイン用の拡散層34n、34pを有する被処理基板を用意する工程と、被処理基板上に高融点金属膜を形成する工程と、拡散層と高融点金属膜との反応によってシリサイド膜52n、52pを形成する工程と、シリサイド膜を形成する工程において拡散層と反応せずに残った未反応の高融点金属膜51aを除去する工程とを備え、未反応の高融点金属膜を除去する工程は、硫酸液中にバブリングによってオゾンが導入されたエッチング液を用いて行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置が微細化しても細線効果による性能低下を抑制できる、高集積化に適した新たな3次元半導体装置及びその製造方法を提供することである。

【解決手段】 上記課題を解決した半導体装置は、半導体層中にこの半導体層表面に垂直に形成されたトレンチと、前記トレンチの側面及び底面の前記半導体層中に形成され、前記トレンチの深さ方向に形成された複数の素子分離と、前記トレンチの側面に沿って形成され、絶縁膜と電極とを備えた複数の機能素子と、前記電極に接続し、前記複数の機能素子を第1の方向に接続する第1の配線と、前記トレンチの側面及び底面の前記半導体層中に形成され、前記素子分離により分離され、前記機能素子を前記第1の方向は異なる第2の方向に電気的に接続する第2の配線とを具備する。

(もっと読む)

ゲート及びチャネル内に歪を誘起させてCMOSトランジスタの性能を向上させる方法

【課題】 ゲート内の応力を調節することによってトランジスタ・チャネル内に歪を誘起させること。

【解決手段】 相補型金属酸化物半導体トランジスタを製造する方法は、異なる型のトランジスタ、例えばN型金属酸化物半導体(NMOS)トランジスタ及びP型金属酸化物半導体(PMOS)トランジスタ(第1及び第2型トランジスタ)を基板(12)上に形成する。この方法は、これらのNMOSトランジスタ及びPMOSトランジスタ上に任意の酸化物層を形成し、次いでNMOSトランジスタ及びPMOSトランジスタを硬い材料(50)、例えば窒化ケイ素層で覆う。この後、この方法は、この硬い材料層(50)の一部をパターン形成し、硬い材料層がNMOSトランジスタ上にのみ残るようにする。次に、この方法は、NMOSトランジスタを加熱し(178、204)、次いで硬い材料層(50)の残存部分を除去する。PMOSトランジスタ(PFET)のゲート(20)又はチャネル領域内に応力を生じさせることなく、NMOSトランジスタ(NFET)のゲート(22)内に圧縮応力、チャネル領域内に引張応力(70)を生じさせることによって、この方法は、PFETの性能を低下させることなく、NFETの性能を改善する。

(もっと読む)

半導体装置とその製造方法

【課題】 周辺回路領域に形成されるロジック回路等に不具合が発生するのを防ぐことができるフラッシュメモリセルを備えた半導体装置とその製造方法を提供すること。

【解決手段】 第1導電体25aのコンタクト領域CR上の第2絶縁膜26を除去する工程と、第2絶縁膜26の上に第2導電膜30を形成する工程と、第1導電体25aのコンタクト領域CR上の第2導電膜30を除去し、該第2導電膜30を第2導電体30aとする工程と、第2導電体30aを覆う層間絶縁膜(第3絶縁膜)44を形成する工程と、コンタクト領域CR上の層間絶縁膜44に第1ホール44aを形成する工程と、コンタクト領域CRと電気的に接続される導電性プラグ45aを第1ホール44a内に形成する工程と、を有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートの空乏化問題の解消と共に、仕事関数の調整が容易な金属シリサイドのみからなるゲート電極を備え、既存プロセスとのインテグレーション性が高い、コスト的にも優位性がある電界効果トランジスタからなる半導体装置の製造方法を提供することを課題とする。

【解決手段】半導体基板1と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極19と、前記ゲート電極19を挟んでエレベーテッド構造を有するソース・ドレイン8とからなる半導体装置の製造方法であって、前記ゲート電極19を金属シリサイド化する工程を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体製造装置

【課題】 n型不純物が導入されたレジスト膜を除去する工程において、異常生成物の発生を抑制することができる技術を提供する。

【解決手段】 ポリシリコン膜15上にレジスト膜16を形成した後、このレジスト膜16に対して露光・現像することにより、レジスト膜16をパターニングする。パターニングは、ポリシリコン膜15のゲート電極形成領域に開口部17が形成されるように行う。次に、パターニングしたレジスト膜16をマスクにして、開口部17から露出したポリシリコン膜15内にリンを注入する。このとき、マスクであるレジスト膜16にもリンが注入されて硬化層16aが形成される。次に、酸素ガスおよびフォーミングガスを導入して硬化層16aおよびレジスト膜16を除去する。ここで、酸素ガスとフォーミングガスとの混合ガスに対するフォーミングガスの体積比率を5%以上30%以下にする。

(もっと読む)

CMOSトランジスタにおけるドーパントプロフィールの改善のためのシステム及び方法

【課題】CMOSトランジスタにおけるドーパントプロフィールの改善のためのシステム及び方法を提供する。

【解決手段】本発明の一実施形態によると、半導体装置を形成する方法は、半導体本体(14)の外面上にゲートスタック(22)を形成する段階を含む。第1及び第2の側壁本体(34)が、ゲートスタックの対向する側に形成される。ゲートスタックのゲート導電体(24)の外面に第1の凹部(36a)が形成され、この第1の凹部が形成された後にゲートスタックの中に第1のドーパント(40)が注入される。第1のドーパントは、第1の凹部を形成するゲートスタックの外面から内向きに拡散する。第1のドーパントは、ゲートスタックと半導体本体の間のインタフェースに向って拡散する。第1の凹部は、インタフェースにおいて第1のドーパントの濃度を増加させる。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接するゲート電極間の間隔が狭い場合においても、特性の劣化を抑制しつつ、サイドウォール絶縁膜を確実に形成しうる半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板32上にゲート絶縁膜48を介して形成されたゲート電極50と、ゲート電極50の両側のシリコン基板32内に形成されたソース/ドレイン拡散層66n、55pと、ゲート電極50の側壁の下側部分及びゲート絶縁膜48の側端部に形成された裾状絶縁膜58と、裾状絶縁膜58に覆われていないゲート電極50の側壁の露出部分及び裾状絶縁膜58の側面に形成されたサイドウォール絶縁膜60とを有する。

(もっと読む)

1,661 - 1,680 / 1,808

[ Back to top ]