Fターム[5F048CB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 3次元MOSIC(BiMOSを含む) (767) | 積層型MOSIC(2層) (366)

Fターム[5F048CB01]の下位に属するFターム

Fターム[5F048CB01]に分類される特許

41 - 60 / 132

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さ(RMS)が1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、または絶縁層表面の一部とドレイン電極表面との高低差は、5nm未満の半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

半導体装置

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

グラフェン・ベースの三次元集積回路デバイス

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

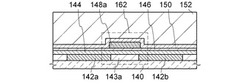

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置、三次元集積回路およびその製造方法

【課題】回路動作時の基板での損失を低減し、表面および裏面の両面において多層配線を形成することで配線の自由度を向上させ、なおかつ貫通配線の配線長を短縮して信号の伝達を高速化する。

【解決手段】薄膜半導体素子2はSOIウェーハを用いて形成し、そのシリコン基板から取り外されているため、素子厚さは埋め込み酸化膜を含めても、例えば2μm以下である。また、貫通配線6は、装置の表面と裏面を貫通するのではなく、薄膜半導体素子に隣接して、コンタクトビア形成時に一括で形成するため、その直径が薄膜半導体素子のコンタクトビアと同程度で、長さが薄膜半導体素子の厚さと同程度である。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置を低消費電力化又は長寿命化すること。

【解決手段】当該半導体装置は、電力供給源となる電池と、特定の回路とがチャネル形成領域が酸化物半導体によって構成されるトランジスタを介して電気的に接続することによって解決することができる。当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該半導体装置の待機時の消費電力を低減することができる。また、これにより当該半導体装置を長寿命化することができる。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】回路構成の簡素化を図り、経年変化の影響を受けることなく、スイッチング素子のジャンクション又はチャネルを熱的破壊から保護することが可能な半導体装置を提供する。

【解決手段】縦型のMOSFETからなる保護トランジスタ20は、半導体基板2の一面にゲート電極23及びソース電極22を、他面にドレイン電極21を形成してある。出力トランジスタ10が形成された半導体基板1の一面に存するソース電極12と、半導体基板2の一面とを導電性の接着剤6で接着して、ソース電極12にソース電極22及びゲート電極23を電気的に接続し、熱的に密結合させる。出力トランジスタ10のゲート電極13は、リード線32で保護トランジスタ20のドレイン電極21と接続する。高温の場合、保護トランジスタ20は閾値が0V以下に低下してオンし、出力トランジスタ10が遮断される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及び電子機器

【課題】回路面積が小さい、またはトランジスタの劣化を防止するよう形成された、有機トランジスタと無機トランジスタとを備えた半導体装置を提供する。

【解決手段】本発明の一形態の半導体装置としてのCMOS回路は、(a)基板100と、(b)有機半導体層106aを含むp型有機トランジスタPTと、(c)p型有機トランジスタPTの上層に設けられた無機半導体層126aを含むn型無機トランジスタNTと、を備える。さらに、n型無機トランジスタNTのチャネル領域126は、p型有機トランジスタPTのチャネル領域106と、平面視において少なくとも部分的に重なっている。

(もっと読む)

半導体装置の作製方法

【課題】分離層と配線を分離させ、半導体素子全体を基板から分離させることを課題とする。

【解決手段】第1の基板上に互いに密着性の弱い第1の層と第2の層を形成し、第2の層上に第1の半導体素子層及び第1の絶縁層を形成し、第1の絶縁層中に第1の層に達するスルーホールを形成し、スルーホール底部に露出した第1の層を酸化させ、第1の絶縁層上及びスルーホール内部に第1の半導体素子層と電気的に接続される配線を形成し、第1の層と第2の層を分離することにより第1の基板から第1の半導体素子層及び配線を分離して配線を露出させる半導体装置の作製方法と、さらに、同様の作製工程により、分離された第2の半導体素子層と配線との間に、異方性導電接着材を設け、第1の半導体素子層と第2の半導体素子層は、異方性導電接着材及び配線によって電気的に接続されている半導体装置の作製方法に関する。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

半導体およびその製造方法

【課題】SOI構造を有するCMOSトランジスタにおいて、CMOSトランジスタのチャネル領域に応力を印加する構造の製造方法の提供。

【解決手段】単結晶のシリコン基板11の表面に素子分離領域13Iにより画成されたnチャネルMOSトランジスタ10Aが形成された第1の素子領域13AとpチャネルMOSトランジスタ10Bが形成された第2の素子領域13Bとを含む単結晶シリコンの活性層13を形成し、シリコン基板と活性層との間に形成されたシリコン酸化膜を有し、シリコン酸化膜は第1の素子領域の下および第2の素子領域の下に連続して延在し、nチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最大の膜厚を有し、ゲート長方向に向かって膜厚を減少させ、pチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最小またはゼロの膜厚を有し、チャネル領域から、ゲート長方向に向かって膜厚を増大させることを特徴とする。

(もっと読む)

冷却機構を含む接合型半導体構造体とその形成方法

【課題】 冷却機構を有する接合型半導体基板を形成するための構造体、設計構造体、及びその形成方法を提供すること。

【解決手段】 2つの半導体基板を備える接合型基板が提供される。各々の半導体基板は、半導体デバイスを含む。少なくとも1つの基板貫通ビアが2つの半導体基板の間に設けられ、それらの間に単一の経路を提供する。2つの半導体基板の底側は、冷却機構を含む少なくとも1つの接合材料層によって接合される。1つの実施形態において、冷却機構は冷却チャネルであり、その中を通って冷却流体が流動し、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。別の実施形態において、冷却機構は、2つの端部とそれらの間の連続した経路を備えた導電性冷却フィンである。冷却フィンはヒートシンクに接続され、接合型基板内の半導体デバイスの動作中に接合型半導体基板を冷却する。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置の作製方法

【課題】複数の半導体集積回路を接続する配線の位置を容易に決定することを課題にする。

【解決手段】第1の基板上に第1の分離層と第1の半導体素子層を形成し、第1の半導体素子層に第1のレーザビームを照射することにより第1の開口部を形成し、第1の開口部に第1の半導体素子層と接続する第1の配線を形成し、第1の半導体素子層上に第1の保護材を形成し、第1の保護材に第1の配線に接続する第1の電極を形成し、第1の分離層に沿って第1の基板と第1の半導体素子層を分離し、上述の作製工程により第2の基板上に、第2の分離層、第2の半導体素子層、第2の配線、第2の保護材、第2の電極を作製し、第2の電極と第1の配線を接続するように第2の保護材上に第1の半導体素子層を貼り合わせ、第2の分離層に沿って第2の基板と第2の半導体素子層を含む積層構造を分離する半導体装置の作製方法に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧のばらつきが小さい記憶素子部と、低消費電力で高速な論理素子部を有する半導体装置を可能にする。

【解決手段】記憶素子部12と論理素子部13とに素子分離領域14で分離された半導体層11の記憶素子部12の第1面S1側に第1ゲート電極23を有する第1電界効果トランジスタ21と、記憶素子部12の第2面S2側に第2ゲート電極33を有し、第1電界効果トランジスタ21とソース・ドレイン領域を共通とする第2電界効果トランジスタ31と、論理素子部13の第1面S1側に第3ゲート電極43を有する第3電界効果トランジスタ41と、第1面S1側に形成された第1絶縁膜51と、第2面S2側に形成された第2絶縁膜61を有し、第1、第2電界効果トランジスタ21、31は完全空乏型の電界効果トランジスタであり、第1、第2ゲート電極23、33は電気的に接続されている。

(もっと読む)

41 - 60 / 132

[ Back to top ]