Fターム[5F048CB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 3次元MOSIC(BiMOSを含む) (767) | 積層型MOSIC(2層) (366)

Fターム[5F048CB01]の下位に属するFターム

Fターム[5F048CB01]に分類される特許

61 - 80 / 132

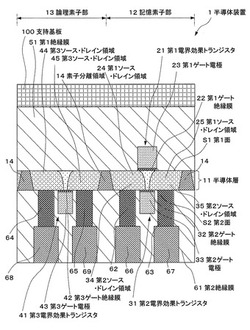

半導体装置およびその製造方法

【課題】しきい値電圧のばらつきが小さい記憶素子部と、低消費電力で高速な論理素子部を有する半導体装置を可能にする。

【解決手段】記憶素子部12と論理素子部13とに素子分離領域14で分離された半導体層11の記憶素子部12の第1面S1側に第1ゲート電極23を有する第1電界効果トランジスタ21と、記憶素子部12の第2面S2側に第2ゲート電極33を有し、第1電界効果トランジスタ21とソース・ドレイン領域を共通とする第2電界効果トランジスタ31と、論理素子部13の第1面S1側に第3ゲート電極43を有する第3電界効果トランジスタ41と、第1面S1側に形成された第1絶縁膜51と、第2面S2側に形成された第2絶縁膜61を有し、第1、第2電界効果トランジスタ21、31は完全空乏型の電界効果トランジスタであり、第1、第2ゲート電極23、33は電気的に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】結晶欠陥が少なく結晶性の高い単結晶シリコン層が絶縁膜上に形成されてなる半導体装置の製造方法及び半導体装置を得るという課題があった。

【解決手段】基板1の一面1aに絶縁膜2を形成する工程と、絶縁膜2を開口して基板1を露出させる穴2cを形成する工程と、穴2cの内壁面を覆うように結晶成長補助膜3を形成する工程と、穴2cを充填するとともに、絶縁膜2の前記基板と反対側の面2aを覆うように非結晶シリコン層を形成する工程と、前記非結晶シリコン層を、レーザーアニール法により単結晶シリコン層5とする工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

積層半導体装置及び積層半導体装置の製造方法

【課題】動作の安定した積層半導体装置を提供する。

【解決手段】単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成され絶縁層に達する分離溝構造と、分離溝構造で囲まれた単結晶シリコン層のボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する貫通結合部とを有する第1半導体装置と、貫通結合部に接する外部接続部を有する第2半導体装置と、を備え、第2半導体装置は、貫通結合部を介して第1半導体装置のボディ領域の電位を制御する。

(もっと読む)

同軸のトランジスタ構造

【課題】 本発明は基板上での同軸トランジスタを開示する。

【解決手段】同軸構造のMOSFETであって、チップ或いは基板(Wafer Bonding)を積層し、軸心貫通孔により貫通し接続してより高い集積度及びラッチ効果のない同軸全対称のCMOSFETの集積回路を形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体部材が単結晶の半導体材料からなり、特性が良好な半導体装置及びその製造方法を提供する。

【解決手段】単結晶のシリコンからなるシリコン基板11上に絶縁膜12を形成し、絶縁膜12に開口部12aを形成し、絶縁膜12上に開口部12aを介してシリコン基板11と接触するようにアモルファスシリコン膜を形成し、このアモルファスシリコン膜をシリコン基板11を起点として固相エピタキシャル成長させて、その後パターニングする。これにより、開口部12aの直上域から外れた領域の一部に、単結晶のシリコンからなるシード層を形成する。次に、このシード層を覆うようにアモルファスシリコン膜を堆積させ、このアモルファスシリコン膜をシード層を起点として固相エピタキシャル成長させて、単結晶シリコン膜を形成する。そして、この単結晶シリコン膜をパターニングすることにより、シリコンピラー33を形成する。

(もっと読む)

半導体装置

【課題】抵抗素子及び容量素子の三次元化によりこれらの面積を縮小する。

【解決手段】本発明の例に係る半導体装置は、半導体基板21と、半導体基板21上に積層され、導電性ポリシリコンから構成される複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>と、複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>上に配置される金属層M1とを備える。複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>の両端は、階段状にレイアウトされ、複数の導電層R<00>〜R<04>, R<10>〜R<14>, R<20>〜R<24>, R<30>〜R<34>は、その両端部において金属層M1を介して互いに直列接続され、抵抗素子を構成する。

(もっと読む)

基板上に積層され自己整合された部品の製造方法

【課題】基板上に積層され自己整合された部品の製造方法を提供する。

【解決手段】基板の一表面に層の積層体を形成する段階であって、積層体が第1犠牲層、第2犠牲層及び表面層を備える段階と、第1犠牲層の一領域をエッチングする段階と、第1犠牲層のエッチングされた領域内及び表面層上に樹脂を堆積する段階と、犠牲層上の樹脂の少なくとも1つの領域に位置合わせされる樹脂の少なくとも1つの領域を第1犠牲層のエッチングされた領域に残すために樹脂をリソグラフィする段階と、第1犠牲層のエッチングされた領域内及び犠牲層上の除去された樹脂を残っている樹脂を制限するための材料で置換する段階と、第1犠牲層のエッチングされた領域内及び表面層上の残っている樹脂の領域を除去して部品の製造に対する専用の領域を提供する段階と、専用の領域内に部品の要素を形成する段階と、第2犠牲層の一領域を選択的にエッチングする段階と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

分子素子およびその製造方法ならびに集積回路装置およびその製造方法ならびに三次元集積回路装置およびその製造方法

【課題】一つの分子素子を印加電界の制御によってダイオード、トランジスタまたはメモリとして使うことができ、必要な機能を有する素子を安価に得ることができる分子素子を提供する。

【解決手段】ソース電極13およびドレイン電極14の間の間隙15に機能性分子16を架橋して分子素子10を構成する。機能性分子16は、誘電率異方性および/または双極子モーメントを有し、かつ電界により配向変化が起きるペンダント分子からなる側鎖が、そのペンダント分子の配向変化によって構造変化が起きて電気的特性が変化する共役系分子からなる主鎖に共有結合したものである。ゲート電極17、18により機能性分子16のペンダント分子に印加する電界によって分子素子10をダイオード、トランジスタまたはメモリとして働かせる。

(もっと読む)

3−D積層型デバイスのESD保護を可能にするシステム及び方法

【解決手段】静電気放電(ESD)保護デバイスが、積層型半導体ダイのアクティブレイヤ間の縦型の空間に形成され、これにより、そうでなければ通信目的のためにしか使用されないであろう空間を利用する。シリコン貫通ビア(TSV:through silicon via)の縦型の表面領域は、ESDイベントに起因する大電圧を緩和するために使用される。一実施形態では、ESDダイオードは、積層型デバイスの半導体ダイのアクティブレイヤ間の縦型TSV内に形成される。このESDダイオードは、積層の半導体ダイの両方の上の回路によって共有され、これによって空間を節約し、そしてESD保護回路によって必要とされるダイ面積を低減し得る。 (もっと読む)

半導体装置およびその製造方法

【課題】より基板サイズの小型化を図ることができる半導体装置およびその製造方法を提供する。

【解決手段】2つのチップ1、21それぞれに縦型パワーMOSFETを作り込んでおき、2つのチップ1、21を互いに裏面同士が接続されるように貼り合せることで、一体化する。具体的には、Pチャネル型のパワーMOSFETとNチャネル型のパワーMOSFETとが互いのドレイン同士を電気的に接続した構造とする。このような構成とすれば、各半導体素子の間にリードフレームを配置した構造ではないため、その分、半導体装置の小型化を図ることができる。

(もっと読む)

半導体装置の製造方法、半導体装置、電気光学装置、および電子機器

【課題】三次元半導体装置における特性を向上させることができる製造方法および装置構成を提供する。

【解決手段】第1半導体膜(9)上にカーボンナノチューブを備えるプラグ電極(15)を形成する工程、形成されたプラグ電極(15)の周囲に層間絶縁膜(16,18)を形成する工程、層間絶縁膜の表面を平滑化してプラグ電極(15)の頂部を露出させる工程、層間絶縁膜およびプラグ電極の頂部上に非晶質の第2半導体膜を形成する工程、非晶質の第2半導体膜にエネルギーを供給して露出したプラグ電極(15)を触媒として機能させて非晶質の第2半導体膜を結晶化させ結晶化した第2半導体膜(23)とする工程を備える。

(もっと読む)

マルチ機能テープ

【課題】物理的に異なる低次元構造体から構成される装置を受取基板上に製造する方法を提供する。

【解決手段】複数の細長い構造体(7)の各々の物質組成がその長さ方向に沿って変化することにより、細長い構造体内において物理的に異なる第1および第2の部分が形成されるように、第1の基板(3)上に、細長い構造体(5)を形成する工程を含む。物理的に異なる第1および第2の装置(1,2)が細長い構造体中において形成される。物理的に異なる第1および第2の部分は、それらが製造された後に、細長い構造体の中において形成されてもよい。細長い構造体は被覆され、第2の基板(7)に移動されてもよい。物理的に異なる第1および第2の装置(1,2)を共通の基板上に設けることが必要とされる回路基板の形成方法を改善することができる。特に、移動工程は1回だけしか必要とされない。

(もっと読む)

半導体装置

【課題】集積回路の高集積化を妨げることなく、静電気放電(ESD)による集積回路の破壊を防止するための保護回路を設ける。

【解決手段】高電源電位が印加される端子に電気的に接続される配線、および低電源電位が印加される端子に電気的に接続される配線を、それぞれ、誘電体を介して隣接させ、かつ集積回路を取り囲むように形成する。このことにより、端子と集積回路の間に配線抵抗が付加され、かつ2本の配線間に容量を付加することができる。ESDなどにより端子に過電圧が印加されても、そのエネルギーが配線抵抗および付加容量により消費されるため、集積回路の破壊を抑えることができる。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】薄膜トランジスタを有する半導体装置を安価に大量生産することを可能にする、半導体装置の製造方法を提供する。

【解決手段】プラスチック基板11等の基板上にアモルファスシリコン層13を形成する工程と、アモルファスシリコン層13をパターニングして、薄膜トランジスタとなる所定のパターンを形成する工程と、その後、パターニングされたアモルファスシリコン層13を結晶化する工程とを有して、薄膜トランジスタを有する半導体装置を製造する。

(もっと読む)

半導体装置

【課題】良好な特性を得ながら、小型化、高耐圧化および低消費電力化が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、シリコンよりも大きいバンドギャップを有し、パワートランジスタ2が形成されたSiC層11と、SiC層11の主表面11aよりも上側の所定領域に形成されるとともに、制御回路用のNMOSトランジスタ3およびPMOSトランジスタ4が形成され、SiC層11とは別の層からなるシリコン層21と、SiC層11のパワートランジスタ2とシリコン層21のNMOSトランジスタ3およびPMOSトランジスタ4とを接続するAl配線5とを備える。

(もっと読む)

半導体装置の作製方法

【課題】より高集積化され、薄型化及び小型化された半導体装置を作製することを目的の一とする。また、半導体装置において、高性能化、低消費電力化を目的の一とする。

【解決手段】剥離層を用いて基板から剥離された半導体素子層を、他基板に形成され、平坦化された無機絶縁層に覆われた半導体素子層上に積層する。上層の半導体素子層を基板より剥離後、剥離層を除去し半導体素子層下に形成される無機絶縁膜を露出する。平坦化された無機絶縁層及び無機絶縁膜を密着させて接合する。

(もっと読む)

半導体装置およびその製造方法

【課題】高密度に搭載可能な構造を有する電界効果トランジスタを備えた半導体装置を提供する。

【解決手段】基板と、この基板上に設けられた第1の絶縁層と、第1の絶縁層に埋め込まれた導電層と、この導電層に電気的に接続し直上に配置された下部拡散層、この下部拡散層上の半導体層、及びこの半導体層上の上部拡散層を有する柱状半導体部と、前記半導体層の周囲側面に設けられたゲート絶縁膜と、このゲート絶縁膜上に設けられたゲート電極と、このゲート電極および前記柱状半導体部を埋め込むように設けられた第2の絶縁層を有する半導体装置。

(もっと読む)

同軸のトランジスタ構造

【課題】基板上での同軸トランジスタの提供。

【解決手段】pドーピング環状ドレイン半導体領域およびソース半導体領域と、同一の基板で環状ソース及びドレイン半導体領域の間に形成される環状チャネル領域及びこの環状チャネル領域上端で酸化物層により隔離される環状多結晶シリコン或いは導体ゲートとソースを接続し自身の基板或いはウェルを参考電圧とする基層と、基層及び環状ソースを接続するための同軸環状の給電導体層と、半導体内の軸心導体に接続するドレイン等の素子から構成され、この同軸PチャネルMOSFET構造の内の各環状素子と環状各極が同軸構造形態により構成され、その環状ゲートの電圧によりトランジスタの電流の流動方向を制御して、各半径方向に環状導体層から軸心導体への半径方向に流動し集中式により構成する同軸トランジスタ。

(もっと読む)

表示装置

【課題】表示装置の画素を構成する電界効果トランジスタの高性能化を実現し、且つ電界効果トランジスタの微細加工技術に依拠することなく、画素内の電界効果トランジスタ数を増やしても電界効果トランジスタ数の増加に伴い低下した画素の開口率を向上及び画素に占める電界効果トランジスタの面積の削減を図ることのできる表示装置を提供することを目的の一とする。

【解決手段】半導体基板より分離され、絶縁表面を有する支持基板に接合された半導体層を有する電界効果トランジスタが、平坦化層を層間に設けて複数積層された画素を複数具備する表示装置とする。

(もっと読む)

61 - 80 / 132

[ Back to top ]