Fターム[5F049PA04]の内容

受光素子−フォトダイオード・Tr (21,418) | 製造方法(工程) (2,065) | 結晶成長 (455) | 気相エピタキシャル法(VPE) (377) | MOCVD法 (221)

Fターム[5F049PA04]に分類される特許

81 - 100 / 221

アバランシェタイプのフォトダイオード

入射光のための開口部(16)を備え、倍増層(7)、電界制御層(8)、吸収層(10)を含む、多数の種々の半導体層を前記開口部から下方に備え、前記吸収層が光を吸収するようになっている表面光入射型アバランシュフォトダイオード(APD)であって、前記開口部から前記吸収層(10)を通過したフォトンを反射し、前記吸収層に戻すように配置されている少なくとも1つのブラッグミラー(14)が前記吸収層(10)の下に存在することを特徴とする、表面光入射型アバランシュフォトダイオード(APD)。  (もっと読む)

(もっと読む)

受光素子及びエピタキシャルウェハ

【課題】III−V族半導体から成り暗電流の低減された受光素子及びエピタキシャルウェハを提供すること。

【解決手段】III−V族半導体からなる基板3と、基板3上に設けられた受光層7と、受光層7に接して設けられ、III−V族半導体からなる拡散濃度分布調整層9と、拡散濃度分布調整層9に接して設けられ、拡散濃度分布調整層9よりも大きいバンドギャップエネルギーを有し、III−V族半導体からなり、P元素を含有する窓層11と、を備え、窓層11と拡散濃度分布調整層9との接合面から窓層11内に延びる所定領域内のn型のキャリア濃度は、5×1015cm−3以上1×1019cm−3以下の範囲内にある。

(もっと読む)

半導体素子の製造方法

【課題】III−V族半導体から成る暗電流の低減された半導体素子の製造方法を提供すること。

【解決手段】III−V族半導体からなる基板3a上にSb元素を含むIII−V族半導体からなる第1の半導体層2aを形成する工程と、第1の半導体層2aを形成した後に、III−V族半導体からなる第2の半導体層10aを第1の半導体層2a上に形成する工程とを備え、第1の半導体層2aを形成する工程は、第1の半導体層2aに含まれており基板3aとの界面から所定の厚みを有する第1の層の形成を第1の温度のもとで行った後に、第1の半導体層2aのうち第1の層を除いた第2の層の形成を第1の温度よりも高い第2の温度のもとで行い、第2の半導体層10aを形成する工程は、第2の半導体層10aに含まれており第1の半導体層2aとの界面から所定の厚みを有する第3の層の形成を第2の温度のもとで行う。

(もっと読む)

III−V族化合物半導体受光素子、及びIII−V族化合物半導体受光素子を作製する方法

【課題】V族構成元素としてSbを含むIII−V化合物半導体層を有する受光層とn型InP窓層とを有しており暗電流を低減可能なIII−V族化合物半導体受光素子を提供する。

【解決手段】受光層21のGaAsSb層の成長の際に供給されたアンチモンのメモリ効果により、受光層23上に成長されるInP層23に、不純物としてアンチモンが含まれる。III−V族化合物半導体受光素子11では、InP層23は不純物としてアンチモンを含むと共に、InP層23にはn型ドーパントとしてシリコンが添加されている。InP層23中のアンチモン不純物は正孔を生成するように作用するけれども、この生成キャリアをInP層23中に添加されたシリコンが補償して、InP層23の第2の部分23dは十分なn導電性を示す。

(もっと読む)

半導体素子およびその製造方法

【課題】 多くのペア数を有する多重量子井戸構造を、良好な結晶品質を確保しながら能率よく成長することができる、半導体素子の製造方法および当該半導体素子を得る。

【解決手段】 本発明の半導体素子の製造方法は、III−V族化合物半導体の量子井戸を50ペア以上有する多重量子井戸構造3を形成する工程を備え、その多重量子井戸構造3の形成工程では、全有機金属気相成長法(全有機MOVPE法)により、多重量子井戸構造を形成することを特徴とする。

(もっと読む)

化合物半導体膜の製造方法、化合物半導体膜及び半導体デバイス

【課題】化合物半導体結晶中への亜鉛の取り込み量を増やすことができる化合物半導体膜の製造方法、化合物半導体膜及び当該化合物半導体膜を用いた半導体デバイスを提供することを目的とする。

【解決手段】亜鉛をドープするp型化合物半導体膜のエピタキシャル成長時に、亜鉛含有原料(例えば、ジエチル亜鉛;DEZn)と共に所定範囲の供給量のSb含有原料(例えば、トリスジメチルアミノアンチモン;TDMASb)を供給することにより、化合物半導体膜(例えば、InGaAs膜)中への亜鉛の取り込み量を増やす。

(もっと読む)

半導体受光素子の製造方法

【課題】暗電流および劣化を抑制可能な半導体受光素子の製造方法を提供する。

【解決手段】本発明に係る半導体受光素子の製造方法では、第1導電型半導体基板を用意する工程と、第1導電型半導体基板上に、第1導電型層、光吸収層、拡散バッファ層、および第2導電型層をこの順に含んだ半導体層を形成する工程と、前記拡散バッファ層および前記第2導電型層において、外周の一部または全部を除去することにより内周を受光部として残す第2導電型層除去工程と、前記第1導電型層の形成後かつ前記光吸収層の形成前に、アバランシェ増倍層を形成する工程とを備える。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

半導体受光装置及びその製造方法

【課題】 十分な受光感度を保ちつつ、受光部の容量を低減し、且つキャリアの走行時間も短縮した半導体受光素子及びその製造方法を提供する。

【解決手段】 半導体基板と、該半導体基板上に形成された第1導電型の第1の半導体層と、該第1の半導体層上に形成された高抵抗の第2の半導体層と、該第2の半導体層上に形成された第1導電型の第3の半導体層と、前記第2の半導体層中に埋め込まれた第2導電型の第4の半導体層からなり、前記第4の半導体層は、前記半導体基板の表面に水平方向に一定間隔で分離されていることを特徴とする半導体受光装置。

(もっと読む)

半導体受光素子

【課題】優れた信頼性を具備し、かつ簡易に製造できる半導体受光素子を提供すること。

【解決手段】本発明は、n型の半導体基板201上に、半導体メサ120と、少なくとも半導体メサ120の側壁を覆う半導体層107aが少なくとも形成されている。半導体メサ120は、光吸収層104と、p型のコンタクト層106を少なくとも有する。半導体基板101の主面は、<01−1>方向を軸として、(100)面に対して回転角θだけ回転した結晶面であり、その回転角θは0.1°≦|θ|≦10°である。

(もっと読む)

メサ型フォトダイオード及びその製造方法

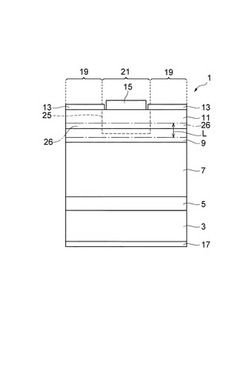

【課題】メサ型フォトダイオードの安定なデバイス特性及び長期信頼性を得る。

【解決手段】メサ(受光領域メサ19)の側面23と、メサの上面24における少なくとも当該メサの肩の部分(肩部25)とは、それらの上に成長された第1導電型、第2導電型、半絶縁型、ないしノンドープの半導体層(例えば、ノンドープInP層17)により連続的に被覆されている。半導体層においてメサの側面23を覆う部分の層厚D1が850nm以上である。

(もっと読む)

光デバイス、半導体基板、光デバイスの製造方法、および半導体基板の製造方法

【課題】高品質な光デバイスをシリコン基板上にモノリシックに形成する。

【解決手段】シリコンを含むベース基板と、ベース基板上に設けられた複数のシード結晶と、複数のシード結晶に格子整合または擬格子整合する複数の3−5族化合物半導体とを備え、複数の3−5族化合物半導体のうちの少なくとも1つに、供給される駆動電流に応じて光を出力する発光半導体、または光の照射を受けて光電流を発生する受光半導体を含む光電半導体が形成されており、複数の3−5族化合物半導体のうち、光電半導体を有する3−5族化合物半導体以外の少なくとも1つの3−5族化合物半導体にヘテロ接合トランジスタが形成されている光デバイスを提供する。

(もっと読む)

窒化物半導体層の剥離方法、半導体装置の製造方法、及び半導体装置

【課題】第1基板から窒化物半導体層を容易に剥離する。

【解決手段】SiC基板101の表面で単層又は複数層のグラフェン層111が成長する工程と、グラフェン層との界面で、共有結合性を有することなく、原子レベルのポテンシャルの規則性のみを用いた結合力を伴って窒化物半導体層114が形成される工程と、窒化物半導体層114とグラフェン層111aとの間、あるいはグラフェン層相互間111a,111b,111cのポテンシャルによる接合力以上の力で、窒化物半導体層がSiC基板から剥離される工程とを備える。また、剥離された窒化物半導体層が第2基板130の表面に接合される。

(もっと読む)

半導体アバランシェ増幅による低レベル信号検出

単一の独立した個別増幅器を用いることによる、又は入力信号を個別に増幅される個別成分に分散させることによる、光又は電気入力信号の検出のためのシステム及び方法を提供する。入力信号は、950nmより長い波長における光吸収プロセスの結果又は低レベル電気信号とすることができる。個別増幅器は、非ゲートモードで降伏領域内又はそれを越えたバイアス電圧を受けながら動作可能なアバランシェ増幅器であり、入力信号検出及び増幅半導体層にモノリシックに統合された複合誘電体フィードバック層を含む。 (もっと読む)

メサ型フォトダイオード及びその製造方法

【課題】メサ上に再成長される半導体層によるメサの被覆性を、工程の追加を行わずに向上させることができるようにする。

【解決手段】メサ(受光領域メサ19)の側壁は、当該メサの裾が広がる方向に傾斜する斜面である。メサの少なくとも側壁112は、その上に成長された、第1導電型、第2導電型、半絶縁型、ないしノンドープの半導体層(例えば、ノンドープInP層17)により被覆されている。メサの下端部における斜面の傾斜角度θ1よりも、メサの上端部における斜面の傾斜角度θ3の方が小さい。

(もっと読む)

アバランシェホトダイオード及びこれを用いた光受信モジュール

【課題】増倍率が低い状態においても、光吸収層内で発生した電子の、光吸収層と電界調整層の界面への蓄積が抑制され、素子破壊に至る光信号強度を増加させることが可能な光吸収層を有するアバランシェホトダイオード及びこれを用いた光受信モジュールの提供。

【解決手段】電気調整層のうち、積層方向の少なくとも一部における伝導帯端のエネルギー準位が、光吸収層における伝導帯端のエネルギー準位より高く、増倍層の伝導帯端のエネルギー準位より低いことを特徴とする。

(もっと読む)

多結晶ウルツ鉱型半導体素子及びその製造方法

【課題】低コストで、かつ、高効率の光学デバイスを製造する。

【解決手段】多結晶ウルツ鉱型半導体素子200の製造方法であって、層状物質であり、かつ、六回対称結晶構造を有するグラファイト基板201の主面に、表面処理を行うことにより表面を荒らす表面処理ステップと、表面処理ステップで表面処理された主面に、複数の結晶粒104を有する多結晶ウルツ鉱型半導体103を主面の垂直方向に成長させる成膜ステップとを含む。

(もっと読む)

アバランシェフォトダイオードおよびその製造方法

【課題】簡単な工程でガードリング構造を作り込むことのできるアバランシェフォトダイオードの製造方法を提供する。

【解決手段】拡散によりpn接合を形成する工程で、拡散マスク26の開口部28の一部に、拡散制御層24を設ける。拡散マスクを経てZnを窓層20に拡散し、受光部とガードリングとを同時に形成する。拡散制御層と窓層とで拡散係数がほぼ等しい場合、単純に拡散制御層の厚さに相当する厚みが拡散フロントでの深さの差となる。

(もっと読む)

半導体集積光デバイス及びその作製方法

【課題】作製時の歩留まりが高く、且つ光導波路と半導体光素子との結合効率を高めることができる半導体集積光デバイス及びその作製方法を提供する。

【解決手段】半導体集積光デバイス1Aは、n型InP基板3と、n型InP基板3上に設けられ、III−V族化合物半導体を含む光導波路110を有する半導体レーザ領域10と、半導体レーザ領域10と並んでn型InP基板3上に設けられ、光導波路110と光学的に結合されn型InP基板3の主面に沿って延びる光導波路21a〜21eを有する光導波領域20とを備える。光導波領域20は、n型InP基板3と光導波路21a〜21eとの間に設けられた下部クラッドとしての酸化シリコン層23を更に有し、光導波路21a〜21eは、III−V族化合物とは異なる半導体からなる。

(もっと読む)

光電変換素子、イメージセンサー及び光電変換素子の製造方法

【課題】PIN構造を有する光電変換素子を、CVD法を用いて形成する場合、P層やN層の不純物の混入を避けるために、各々の層毎にチャンバーを分けて形成することが必要となる。この場合にはチャンバーが3つ必要となり、設備投資が大きくなるという課題がある。また、I層と半導体以外の領域が接触することで、界面欠陥起因の電荷発生により、黒浮きが生じる課題がある。

【解決手段】I型半導体層208を、CVD法により得られたN+層210と、イオン注入法で形成されたP+層207で包んだ。I型半導体層208は半導体以外の領域と接触しない。そのため、界面欠陥起因の電荷発生を抑制することができる。また、P+層207をイオン注入法で形成することで、2つのチャンバーを備えたCVD装置を用いることが可能となり、設備投資を抑えることが可能となった。

(もっと読む)

81 - 100 / 221

[ Back to top ]