Fターム[5F058BF25]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜の形成法 (10,542) | 気相堆積 (7,977) | 堆積物形成反応ガス (3,745) | 主構成元素の化合物 (2,014) | TEOS (210)

Fターム[5F058BF25]に分類される特許

81 - 100 / 210

フラッシュメモリ及びその製造方法

【課題】30nm以下の微細化に適応できるフラッシュメモリ及びその製造方法を提供する。

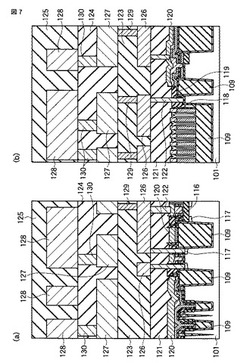

【解決手段】基板101に接続された上部にスペーサ絶縁膜116を有するフィン構造のビットラインから形成されたメモリセル部の最小加工寸法をFとするとき、独立に書き込み/消去可能なビットライン2本が対になって4F周期に配置されてメモリセル部が形成され、一対のフィンの上部を覆うように記憶絶縁膜が形成されている。

(もっと読む)

半導体素子を作製する方法

【課題】第1半導体部および第2半導体部を含む半導体素子を作製する際に半導体の曲がりを小さくする。

【解決手段】絶縁体マスク17を用いて、LDエリア1bに第1半導体部19を形成し、EAエリア1cに第2半導体部37を形成する。絶縁体マスク17内では、キャップ層15に近い下部では線膨張率が高く、キャップ層15から遠い上部では線膨張率が低い。EAエリア1cに第2半導体部37を形成する前に、エッチング端面19a側から第1半導体部19の最上層であるキャップ層15を部分的にエッチングする。これで、境界1d近傍で、絶縁体マスク17とキャップ層15との間にギャップGを生じさせると、このギャップG部分の絶縁体マスク17において、キャップ層15に近い下部17eは多く膨張し、キャップ層15から遠い上部17fは少なく膨張する。その結果、境界1d近傍の絶縁体マスクが上に曲がる。

(もっと読む)

ゲート絶縁膜の形成方法

【課題】ゲート絶縁膜に用いる高誘電体金属酸化膜又は高誘電体金属シリケート膜におけるリーク電流を低減できるようにする。

【解決手段】高誘電体金属シリケートからなるゲート絶縁膜の形成において、金属等を含む前駆体の暴露時間には、表面吸着反応により成膜レートが飽和する時間を用い、酸化剤の暴露時間には、金属酸化膜の組成が化学量論値の97%以上となる時間を用いてALD堆積を行う。

(もっと読む)

半導体メモリ素子の素子分離膜形成方法

【課題】 本発明は、トレンチの底面に流動性の第1の絶縁膜を満たし、第2の絶縁膜を形成した後に乾式エッチング工程及び湿式エッチング工程を行ってトレンチの上部の幅を広げながら第2の絶縁膜に含まれるフッ素(F;fluorine;フローリン)の量を減少させることができる半導体メモリ素子の素子分離膜形成方法を提供することを可能にすることを目的としている。

【解決手段】 トレンチが形成された半導体基板が提供される段階と、トレンチを含む半導体基板上に第1の絶縁膜を形成する段階と、第1の絶縁膜の一部を除去する第1のエッチング工程を行ってトレンチの開口部の幅を広げる段階と、第2のエッチング工程を行って第1の絶縁膜内に含まれた不純物を除去する段階と、第1の絶縁膜を含む半導体基板上に第2の絶縁膜を形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体光素子を作製する方法

【課題】埋め込み層の成長に際して異常成長を低減可能な、半導体光素子を作製する方法を提供する。

【解決手段】誘導結合型プラズマCVD装置を用いて、そのバイアス電力PBIASを制御することによって膜応力を調整して、複数のIII−V化合物半導体層を含む半導体積層上に、厚さ2マイクロメートル以上のシリコン酸化膜を成長する。シリコン酸化膜のマスクを半導体積層上にエッチングにより形成する。このマスクを用いて半導体積層をドライエッチングして光導波路構造のための半導体メサを形成する。マスクを用いて半導体メサの埋め込み成長を行う。マスクのシリコン酸化膜の室温における膜応力は、−250MPa〜−150MPaである。膜応力は、摂氏500度〜摂氏700度の温度範囲で−200MPa〜ゼロMPaである。

(もっと読む)

Si及び金属ナノ結晶核形成のためのプラズマ表面処理

【課題】 不揮発性メモリデバイスのようなデバイス、及び統合プロセスツールにおいてデバイスを形成する方法の提供。

【解決手段】 トンネル酸化物層を基板上に堆積させるステップと、トンネル酸化物層をプラズマに曝し、その結果、プラズマがトンネル酸化物の表面と近傍表面の形態を変化させ、プラズマ変化した近傍表面を形成するステップと、を含む。その後、トンネル酸化物の変化した近傍表面上にナノ結晶を堆積させる

(もっと読む)

プラズマ処理装置と基板処理システムおよびプラズマ処理方法

【課題】処理容器内の真空状態を維持したまま、載置台の上面の周辺部に対してカバー部材を載置・除去できるようにする。

【解決手段】処理容器30内に供給された処理ガスをプラズマ化させることにより、相対的に小型の基板W2と相対的に大型の基板W1を処理容器30内において選択的に処理可能なプラズマ処理装置5であって、処理容器30内には、基板W1、W2を選択的に上面に載置させる載置台31が設けられ、載置台31の上面の中央部31’には、載置台31の上面の中央部31’に載置される小型の基板W2の裏面を支持可能な位置に配置された中央昇降部材70が設けられ、載置台31の上面の周辺部31”には、載置台31の上面の中央部に載置された小型の基板W2の外側において昇降自在な周辺昇降部材75が設けられ、周辺昇降部材75は、載置台31の上面に載置される大型の基板W1の裏面を支持可能な位置に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】低吸湿性かつ低誘電率のF添加SiO2 膜を形成すること。

【解決手段】導電領域間を電気的に分離し、Si、O、Fを含み、SiO2 の網目構造を有する絶縁膜をプラズマCVD法により形成する際に、原料ガスとして、SiF(OCH2 CF3 )3 、SiF(OCH2 C(OR)3 )3 (Rは官能基)、SiF(OCH2 CF2 R)3 (Rは官能基)、SiF(OCH2 C(OR)2 R′)3 (R,R′は官能基)、SiF(OCH2 C(NR2 )3 )3 (Rは官能基)、SiF(OCH2 C(NR2 )2 R′)3 (R,R′は官能基)、SiF(OCH2 CRO)3 (Rは官能基)、SiF(OCH2 CN)3 、SiF(OCH2 NO2 )3 、SiF(OCH2 COOR)3 (Rは官能基)またはSiFn (OCH2 CF2 R)4-n (n=1〜3、Rは官能基)のガスを用いたときに、前記Siに結合した元素がFと置換する反応確率が、前記SiにFが結合している場合のほうが、前記SiにFが結合していない場合よりも小さくなる成膜温度で、前記絶縁膜を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】微小なコンタクトを形成する場合でも、コンタクト抵抗の上昇を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に狭い間隔で配置された複数のゲート電極12と、当該ゲート電極12を被覆する層間絶縁膜20とを備える。層間絶縁膜20は、互いに隣接するゲート電極12間を充填するとともに、ゲート電極12上での膜厚が、半導体基板10の平坦面上での膜厚よりも薄い吸湿性絶縁膜15と、吸湿性絶縁膜15上に形成された非吸湿性絶縁膜16とを備える。この構造によれば、ゲート電極12間に微小なコンタクトを形成する場合でも、吸湿性絶縁膜15から放出されるH2Oに起因するコンタクト抵抗の増大を抑制することができる。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】高品位な膜質を有するシリコン酸化膜を基板上に成膜可能な成膜方法等を提供する。

【解決手段】

オゾンガス発生源から発生した100%のオゾンガスをオゾンガス供給路62に通流させ、このオゾンガス供給路62から分岐した希釈ガス供給路63に希釈ガスを通流させて、予め設定したオゾンガスの濃度となるように100%のオゾンガスを希釈し、希釈されたオゾンガスを当該オゾンガス流路62から処理容器2、21内に供給する。そしてシリコン有機化合物からなる成膜ガスを前記処理容器2、21内に供給しオゾンとシリコン有機化合物とを反応させて基板上にシリコン酸化膜を成膜する。

(もっと読む)

化合物半導体光デバイスを作製する方法

【課題】誘電体マスクの除去において残渣を低減可能な、化合物半導体光デバイスを作製する方法を提供する。

【解決手段】化合物半導体光デバイスを作製する方法は、(a)有機シラン系原料および酸素原料を含む成膜ガスを供給して誘導結合プラズマ−化学的気相成長法で、ヒータを用いて基板11を加熱しながら、シリコン化合物からなる誘電体マスク膜17を化合物半導体領域10上に堆積する工程と、(b)誘電体マスク膜17にパターンを形成して誘電体マスク17aを形成する工程と、(c)誘電体マスク17aを用いて、化合物半導体領域10のドライエッチングを行ってメサ形状の化合物半導体領域10cを形成する工程とを備える。誘電体マスク膜17の堆積は摂氏200度以上の基板温度において行われる。誘電体マスク膜17の堆積は摂氏300度以下の温度において行われる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート酸化膜へのプラズマダメージを抑制することができ、ゲート酸化膜の劣化が抑制されるとともにスループットが向上した半導体装置の製造方法を提供する。

【解決手段】本発明にかかる半導体装置の製造方法において、プラズマ絶縁膜を形成する工程は、成膜装置内において、成膜ガスを供給しながら、高周波電界および低周波電界を印加してFET形成領域を覆う前記プラズマ絶縁膜を成膜する工程と、前記プラズマ絶縁膜を成膜した後、前記高周波電界の印加を継続しながら、前記低周波電界の印加を停止した後または同時に前記成膜ガスの流量を経時的に漸次減少させる工程と、を含む。

(もっと読む)

プラズマCVD装置

【課題】内側の電極に汚れが付くのを確実に防止し、かつ成膜領域を広くする。

【解決手段】1組の電極12,13と、もう1組の電極23,22間でそれぞれ常圧でプラズマ空間Pを発生させる。供給源71,72から各プラズマ空間Pに反応ガスを供給する。2つのプラズマ空間P,Pを通過した反応ガスが吹き出される2つの吹出口1b,1bの間に供給源80から金属含有ガスを供給する。ガス整流板31で、吹き出された後の反応ガスと金属含有ガスとの合流ガスの流路を被処理面に沿うよう形成する。ガス整流板31を2組の電極すべての被処理面を向く面に被せ、かつ2組の電極のうち両外側の電極より外側へ突出させ、更に外側に排気機構91,92を設ける。

(もっと読む)

薄膜トランジスタ、表示装置、及び薄膜トランジスタの製造方法

【課題】ゲート絶縁耐性を向上させる半導体装置を提供する。

【解決手段】本発明に係る半導体装置30は、基板31と、基板31上に形成された絶縁膜(32、33)と、絶縁膜(32、33)上に形成された島状の多結晶半導体層(ポリシリコン層35)と、多結晶半導体層(ポリシリコン層35)上に形成され、純水に対する接触角が10°以下であり、且つ膜厚が0.5nm以下の第1酸化膜36と、第1酸化膜36上に形成されたゲート絶縁膜38と、ゲート絶縁膜38上に形成されたゲート電極39と、を有するものである。

(もっと読む)

半導体素子及びその製造方法

【課題】コンタクトプラグの形成のための平坦化工程で障壁層が損傷することを防止することができる半導体素子及びその製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、半導体基板上に複数の導電性構造物間の空間を埋め立てて上面が平坦化された絶縁膜を形成し、絶縁膜を部分的に除去して基板の一部を露出する開口を形成する。その後、開口の下部側壁及び底面に沿って形成された残留金属膜と開口の上部側壁及び残留金属膜の表面に沿って形成された金属窒化膜とを含む障壁層を形成する。障壁層を含む開口を埋め立てて金属プラグを形成する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁層の過剰な研磨を抑制できる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、オリエンテーションフラット部111が形成された半導体基板11上に、配線層13および導体膜14を形成する工程と、前記配線層13および前記導体膜14上に、前記配線層13および前記導体膜14を被覆する絶縁層15を形成する工程と、前記絶縁層15を研磨する工程とを備える。

前記配線層13および前記導体膜14を形成する前記工程では、オリエンテーションフラット部111に近傍領域のみにオリエンテーションフラット部111に略直交する方向に延在する導体膜14を形成する

(もっと読む)

シリコン酸化膜及びその製造方法並びにそれを用いたゲート絶縁膜を有する半導体装置

【課題】ゲート絶縁膜として高性能なシリコン酸化膜を提供し、電気特性に優れた半導体装置を提供する。

【解決手段】本発明に係るシリコン酸化膜は、赤外吸収スペクトルの(ピーク半値幅)×(ピーク高)で表されるピーク面積強度において、波数2340cm-1付近に現れるCO2帰属ピークの面積強度が、波数1060cm-1付近に現れるSiO2帰属ピークの面積強度に対して、8E−4倍以上であることを特徴とする。

(もっと読む)

NORフラッシュデバイス及びその製造方法

【課題】本発明は、NORフラッシュデバイス及びその製造方法を提供する。

【解決手段】バックエンドオブライン(BEOL)構造を有するNORフラッシュデバイスにおいて、BEOL構造は導電領域を有する基板と、基板上に形成された第1層間絶縁膜と、導電領域に形成される第1金属ラインと、該第1金属ラインと第1層間絶縁膜を覆う第2層間絶縁膜と、第2層間絶縁膜を貫通する第1コンタクト及び第1コンタクトを通じて第1金属ラインと連結される第2金属ラインを具備して、第1コンタクト、第1及び第2金属ラインのうちで少なくとも一つは銅であり、第1及び第2層間絶縁膜のうちで少なくとも一つは、低誘電物質を含む。

(もっと読む)

基板ギャップ内に犠牲酸化物ライナを形成する酸素SACVD

【課題】 犠牲酸化物層を形成し除去する方法を提供する。

【解決手段】 この方法は、最上部と側壁を持つ段差部を基板上に形成するステップであって、段差部が、前記ステップを含む。この方法は、また、分子酸素とTEOSの化学気相堆積によって段差部の周りに犠牲酸化物層を形成するステップであって、酸化物層が段差部の最上部と側壁上に形成される、前記ステップを含んでもよい。この方法は、また、酸化物層と段差部の最上部分を除去するステップと、段差部の除去によって暴露される基板の一部を除去して、エッチングされた基板を形成するステップと、エッチングされた基板から犠牲酸化物層全体を除去するステップとを含んでもよい。

(もっと読む)

パターンローディング用途向けの低温SACVDプロセス

酸化シリコン膜の堆積におけるパターンローディングを改良するための方法が説明されている。上記方法は、堆積基板を堆積チャンバに提供するステップと、上記堆積基板の温度を約250℃〜約325℃の温度に調整するステップとを含んでもよい。オゾン含有ガスが、約1.5slm〜約3slmの第1の流量で上記堆積チャンバに導入されてもよく、この場合、上記ガスにおけるオゾン濃度は約6重量%〜約12重量%である。TEOSもまた、約2500mgm〜約4500mgmの第2の流量で上記堆積チャンバに導入されてもよい。上記酸化シリコン膜の堆積レートは、上記基板の堆積表面での上記オゾンおよびTEOSの反応の反応レートによってコントロールされる。 (もっと読む)

81 - 100 / 210

[ Back to top ]