Fターム[5F058BF25]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜の形成法 (10,542) | 気相堆積 (7,977) | 堆積物形成反応ガス (3,745) | 主構成元素の化合物 (2,014) | TEOS (210)

Fターム[5F058BF25]に分類される特許

21 - 40 / 210

半導体製造方法及び基板処理装置

【課題】形成される薄膜中に残留する副生成物や中間体の濃度を制御して基板処理することができる半導体製造方法や基板処理装置を提供する。

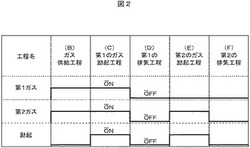

【解決手段】基板を処理室内へ搬入する搬入工程と、前記基板が搬入された処理室内へ、メチル基を含む有機シリコンガス及び酸素含有ガスを供給するガス供給工程と、前記ガス供給工程に続けて、前記基板が搬入された処理室内へ、メチル基を含む有機シリコンガス及び酸素含有ガスを供給しつつ、前記供給されたガスに紫外光を照射して励起する第1のガス励起工程とから、半導体製造方法を構成する。

(もっと読む)

基板処理方法

【課題】基板に吸着したガスに含まれる不純物を効果的に除去しつつ基板処理することができる基板処理方法を提供する。

【解決手段】基板を処理室内へ搬入する搬入工程と、前記処理室内へ搬入された基板に、第1のガスを吸着させる第1ガス供給工程と、前記第1ガス供給工程の後、前記処理室内から第1のガスを排気する第1ガス排気工程と、前記第1ガス排気工程の後、前記基板に付着した第1のガスを、分解機構により分解する第1分解工程と、前記第1分解工程の後、前記処理室内へ第2のガスを供給しつつ、前記分解機構により第2のガスを分解する第2ガス供給工程と、前記第2ガス供給工程の後、前記基板を処理室内から搬出する搬出工程とから、基板処理方法を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

基板処理装置及び基板処理方法

【課題】

本発明は、成膜の生成効率を向上できる光CVD法を用いた基板処理装置及び基板処理方法を提供することにある。

【解決手段】

本発明は、真空室である処理室に処理用ガスを導入し、前真空室である処理室に処理用ガスを導入し、前記処理用ガスに第1の光を、前記第1の光を透過する第1の透過窓を介して第1の照射をし、前記第1の照射によって発生した第1の成膜ガスを前記処理室内の基板に堆積させて成膜する際に、前記処理室に前記処理用ガスを導入する前に、前記処理用ガスを所定の温度まで加熱し、前記加熱された処理用ガスに第2の光を、前記第2の光を透過する第2の透過窓を介して第2の照射をし、前記第2の照射によって第2の成膜ガスを発生させ、前記第2の成膜ガスと第2の照射によって未反応である前記処理用ガスとを前記処理室に導入し、前記第1の成膜ガスと第2の成膜ガスとを前記基板に堆積させて成膜することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】吸湿性の高い絶縁膜を使用してもコンタクト又は配線の劣化を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板10上に第1の絶縁膜15を形成する工程(a)と、第1の絶縁膜15にホール24を形成する工程(b)と、ホール24の側壁上に、第1の絶縁膜15よりも水分を通しにくい第2の絶縁膜17を形成する工程(c)と、工程(c)の後、ホール24に導電体30を埋め込むことにより、プラグ19を形成する工程(d)とを備えている。

(もっと読む)

半導体装置とその製造方法

【課題】 結晶シリコンとアモルファスシリコンとを含むシリコンを活性層に有する薄膜半導体装置は、活性層がゲート絶縁層から剥がれやすく、良好な特性が得られない。

【解決手段】 基板(101)に、ゲート電極(102)、窒化シリコンを含むゲート絶縁層(103)、結晶シリコンとアモルファスシリコンとを含むシリコン層(105)、コンタクト層(107)、ならびにソース電極及びドレイン電極(108)が、順に積層された半導体装置であって、前記シリコン層(105)の内部で、前記基板に近い側から前記ソース電極及びドレイン電極に近い側に向かって、前記結晶シリコンの体積比率が大きくなっており、かつ、前記ゲート絶縁層(103)と前記シリコン層(105)との間に酸化シリコンを含む層(104)が挟まれていることを特徴とする半導体装置。

(もっと読む)

成膜方法

【課題】小さい膜厚比が得られる成膜ガスと、大きい膜厚比が得られる成膜ガスとを用いて、所定膜厚比の酸化膜を形成することができる成膜方法を提供する。

【解決手段】穴87の側壁及び底面を除いた基板81の表面に形成される酸化膜88の膜厚の、穴87の底面に形成される酸化膜88の膜厚に対する膜厚比が所定の膜厚比となるように、穴87の側壁及び底面を除く基板81の表面に、穴87の底面よりも厚い膜厚の酸化膜88を形成するに当たり、テトラエトキシシラン及び酸素の混合ガスをプラズマ化して酸化膜88aを形成した後、テトラエトキシシラン及び酸素の混合ガスよりも高い膜厚比が得られる、シラン及び亜酸化窒素の混合ガスをプラズマ化して酸化膜88bを形成し、テトラエトキシシラン及び酸素から形成される酸化膜88aと、シラン及び亜酸化窒素から形成される酸化膜88bとによって、所定膜厚比の酸化膜88を形成する。

(もっと読む)

シーケンシャル化学気相成長法

【課題】本発明は、高い反応性をもつガス(ラジカル)を利用できるようにラジカル発生装置を用いて、いかなる元素の薄膜の成長をも容易に行うことができる方法を提供する。

【解決手段】複数のサイクルを含むシーケンシャル気相成長法による、基板上へのAl2O3薄膜の成長方法において、それぞれのサイクルは、ガス状のトリメチルアルミニウム(TMA)にパーツを接触させること、ガス状のTMAの供給を停止すること、チャンバからガス状のTMAを除去すること、及び原子状酸素にパーツを接触させることを含む。

(もっと読む)

低水分誘電体膜を形成する方法

半導体装置の製造方法

【課題】後工程のダメージがなく、優れた特性を有する強誘電体キャパシタを提供する。

【解決手段】実施形態に係わる半導体装置の製造方法は、半導体基板の上方に、誘電体膜を下部電極と上部電極とで挟んでなるキャパシタ(200,300,400)を形成する第1の工程と、O3とTEOSを原料としたCVD法により、キャパシタ(200,300,400)を覆う酸化膜(122,125,128)を形成する第2の工程と、ALD法により、酸化膜(122,125,128)上に保護膜としてのAl2O3(123,126,129)膜を形成する第3の工程とを備える。

(もっと読む)

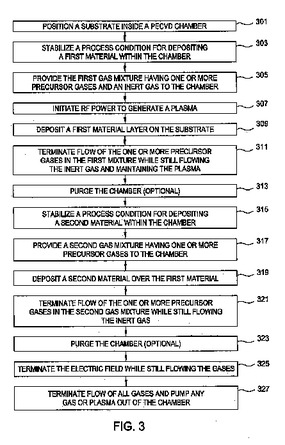

連続プラズマを用いるPECVD(プラズマ化学気相堆積)マルチステップ処理

本発明の諸実施形態は、多層堆積する間中の欠陥を低減する方法を提示する。一実施形態では、この方法は、基板をプラズマの存在下で第1のガス混合物および不活性ガスに曝して、基板上に第1の材料の層を堆積するステップと、第1の材料の所望の厚さが得られたときに、プラズマを引き続き維持しつつ不活性ガスを流しながら、第1のガス混合物を終了させるステップと、基板をプラズマの存在下で、第1のガス混合物と共存できる不活性ガスおよび第2のガス混合物に曝して、第1の材料の層の上に第2の材料の層を同じ処理チャンバ内で堆積するステップとを含み、第1の材料の層と第2の材料の層は互いに異なる。  (もっと読む)

(もっと読む)

薄膜均一性を制御する方法およびそれにより生産された製品

【課題】大型基板上に堆積されるオルガノ珪酸塩膜の厚さ均一性を制御する方法を提供する。

【解決手段】CVD、PECVD、急速加熱処理などにより、処理チャンバ内に大型基板を提供するステップと、前記大型基板の表面周囲領域と前記周囲領域の内側表面領域とを含むように、前記大型基板上の識別可能な少なくとも2か所の温度を制御するステップと、前記大型基板の表面周囲領域の温度を、前記周囲領域の内側表面領域の温度より約10℃低い温度から、前記周囲領域の内側表面領域の温度より約20℃高い温度までの範囲内に維持するステップと、オルガノ珪酸塩膜を堆積するステップを備え、堆積された前記オルガノ珪酸塩膜は約10%以下の膜均一性を提供する方法。

(もっと読む)

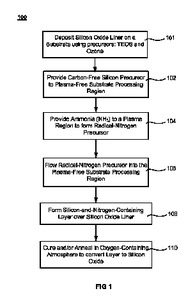

酸化物ライナを使用する流動可能な誘電体

酸化ケイ素層を形成する方法が記載される。方法は、無炭素シリコン含有前駆体をラジカル−窒素前駆体と混合すること、シリコン−窒素含有層を基板上に堆積することを含む。ラジカル−窒素前駆体は、プラズマ内に水素−窒素含有前駆体を流すことによって、プラズマ中で形成される。シリコン−窒素含有層を堆積する前に、酸化ケイ素ライナ層が形成され、シリコン−窒素含有層の接着、平滑性、流動性を改善する。シリコン−窒素含有層は、膜を硬化およびアニーリングすることにより、シリコン−酸素含有層に変換することができる。方法は、酸化ケイ素ライナ層を形成し、その後スピンオンシリコン含有材料を塗布することも含む。  (もっと読む)

(もっと読む)

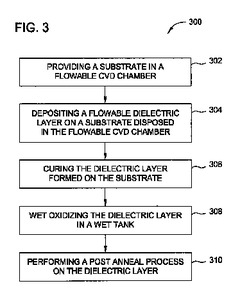

流動性CVD処理から形成された誘電体材料上で実行される湿式酸化処理

基板内に画定されたトレンチまたはビアを充填するケイ素含有誘電体材料上で湿式酸化処理を実行する方法が提供される。一実施形態では、誘電体材料を基板上に形成する方法は、流動性CVD処理によって誘電体材料を基板上に形成するステップと、基板上に配置された誘電体材料を硬化させるステップと、基板上に配置された誘電体材料上で湿式酸化処理を実行するステップと、酸化させた誘電体材料を基板上に形成するステップとを含む。  (もっと読む)

(もっと読む)

SiO2膜を堆積する方法

【課題】プラズマ化学気相成長法(PECVD)を用いて低い温度で無機SiO2膜を堆積する方法を提供する。

【解決手段】チャンバ内でプラズマ化学気相成長法(PECVD)を用いて250℃よりも下の温度で無機SiO2膜を堆積する方法であって、オルトケイ酸テトラエチル(TEOS)及びO2を前駆体として15:1と25:1との間のO2/TEOS比で供給し、前記前駆体を、RF駆動シャワーヘッドを用いて堆積し、前記RF駆動シャワーヘッドを、高周波成分及び低周波成分を用いて駆動する。

(もっと読む)

引張膜のための応力管理

クラッキングする傾向を減少させた、間隙充填酸化ケイ素層の形成が記載される。堆積は、トレンチの充填を容易にする、流動可能なシリコン含有層の形成を含む。高い基板温度における後続の処理が、従来技術の方法に従って形成された流動可能な膜よりも、誘電体膜中のクラッキングを少なくする。間隙充填酸化ケイ素層の形成に先立って堆積された圧縮性ライナ層が記載され、後続して堆積される膜がクラックする傾向を減少する。流動可能なシリコン含有層の後に堆積される圧縮性キャッピング層も、クラッキングを減少させるように決定された。圧縮性ライナ層および圧縮性キャッピング層は、単独でまたは組み合わせて使用され、クラッキングを減少させ、多くの場合クラッキングをなくすことができる。開示した実施形態の圧縮性キャッピング層は、下にある窒化ケイ素の層を酸化ケイ素層に変換できることが、さらに確定されている。 (もっと読む)

半導体装置の製造方法

【課題】MIM容量素子の絶縁膜SiO2について、電圧係数以外の特性として温度係数の小さなMIM容量素子を獲得する。

【解決手段】メタル−容量絶縁膜−メタル(MIM)容量素子のSiO2絶縁膜の製造方法であって、前記容量絶縁膜は、プラズマCVD法でTEOS(テトラエトキシシラン)を原料とし、成膜温度を330℃乃至350℃で成膜されることを特徴とする。

(もっと読む)

パルスRFプラズマを用いたTEOS酸化物の堆積

【課題】プラズマ増強化学気相成長とTEOSを用いて基板上に高品質の二酸化ケイ素膜を堆積する方法を提供する。

【解決手段】該方法には、TEOS酸化物プラズマを生成するために用いられる高周波パルス電源を供給することにより、基板上の二酸化ケイ素の堆積速度を制御するステップが含まれる。得られた二酸化ケイ素膜は、薄膜トランジスタを形成する応用において電気的及び機械的膜特性が良好である。

(もっと読む)

成膜方法及び処理システム

【課題】スループットを高く維持しつつリーク電流を抑制してリーク特性も高く維持することが可能な成膜方法を提供する。

【解決手段】被処理体の表面とゲート電極との間に介在されるゲート絶縁層を形成する成膜方法において、シリコンを含む界面膜を所定の温度で形成する界面膜形成工程S1と、被処理体を冷却する冷却工程S2と、冷却された被処理体に対して界面膜形成工程の所定の温度より低い温度でゲート絶縁膜を形成するゲート絶縁膜形成工程S3とを有する。

(もっと読む)

酸化膜形成方法

【課題】酸化膜とCVD膜との密着性を高めて界面特性の優れた膜の作製を実現する。

【解決手段】処理チャンバ205内において、処理基板に対してオゾン含有ガスのみを供給して処理基板上に酸化膜を形成する酸化工程と、この酸化工程を経た処理基板に対してCVD原料ガスとオゾン含有ガスとを供給して当該処理基板上に前記原料ガスの成分の酸化物からなる酸化膜を形成させるCVD工程とが実行される。前記CVD工程の初期段階の製膜速度は前記酸化工程の製膜速度よりも小さく制御される。また、前記CVD工程を経た処理基板をオゾン含有ガスの雰囲気または紫外光領域の波長を有する光が照射されたオゾン含有ガスの雰囲気に曝すアニール工程と、このアニール工程を経た処理基板を前記CVD工程に供する工程とを有するとよい。前記アニール工程を経た処理基板を前記CVD工程に供する工程を複数繰り返すとなおよい。

(もっと読む)

21 - 40 / 210

[ Back to top ]