Fターム[5F058BF25]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜の形成法 (10,542) | 気相堆積 (7,977) | 堆積物形成反応ガス (3,745) | 主構成元素の化合物 (2,014) | TEOS (210)

Fターム[5F058BF25]に分類される特許

41 - 60 / 210

半導体装置の製造方法及び製造装置

【課題】 本発明の目的は、CVD法等で膜を堆積するにあたり、不純物の除去、更なる膜の改質、膜の安定化を図るものである。

【解決手段】第一の原料と基板に含まれたシリコン成分が結合しない温度で基板を支持するステップと、少なくとも第一の原料を含む材料を処理室に供給し、励起し、前記素子分離領域に、所望の厚みの堆積層を形成する第一の基板処理ステップとを有する第一処理と、第一の原料を含まず、第二の原料を含む材料を処理室に供給し、励起し、前記堆積層を反応、蒸発、もしくは改質する第二の基板処理ステップとを有する第二処理と、前記第一処理と前記第二処理を繰り返すよう処理する基板処理方法

(もっと読む)

金属−シリコン−含有膜のパルス化学蒸着方法

基板上に金属−シリコン−含有膜をパルス化学蒸着により形成するための方法が提供される。本方法は、前記基板をプロセスチャンバ内に準備し、前記基板を金属−シリコン−含有膜を、金属含有ガス及びシリコン含有ガスの前記基板上での熱分解による化学蒸着に適する温度に維持し、前記基板を前記金属含有ガスの連続フローに暴露し、及び前記連続フローの間に前記基板を前記シリコン含有ガスの順次的パルスに暴露する、方法である。  (もっと読む)

(もっと読む)

基板処理方法及び基板処理装置

【課題】高いアスペクト比で、狭い幅の溝に絶縁膜を埋め込むことの可能な、スループットの高い基板処理方法を提供する。

【解決手段】基板を処理室内へ搬入する工程と、炭素及び水素を含むシリコン化合物ガスを処理室内へ供給する工程と、処理室内へ供給されたシリコン化合物ガスに紫外光を照射して基板を処理する工程と、処理された基板を処理室から搬出する工程と、処理室内を励起された酸素含有ガスで処理する工程とを備える基板処理方法により、基板を処理する。これにより、シリコン化合物ガスに紫外光を照射して基板を処理する際に処理室内壁等に付着した付着物を、励起された酸素含有ガスで処理することにより改質することができる。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】オフ電流が低く、オン電流及び電界効果移動度が高い薄膜トランジスタを提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁層として窒化シリコン層と当該窒化シリコン層が酸化された酸化シリコン層を積層して形成し、該ゲート絶縁層の酸化シリコン層との界面直上から結晶成長した微結晶半導体層を形成する。ゲート絶縁層の直上から結晶成長するため、結晶性の高いオン電流及び電界効果移動度が高い薄膜トランジスタとすることができる。また、バッファ層を設けてオフ電流を低減させる。

(もっと読む)

デバイスの製造方法及びデバイス

【課題】メモリ機能等を有する機能膜の水による劣化を防止すること。

【解決手段】成膜装置内で、機能膜が形成された基板上に、上記機能膜を覆うように、絶縁膜を形成する絶縁膜形成工程と、形成した上記絶縁膜の表面をプラズマに曝すプラズマ処理工程とを繰り返すこと。

(もっと読む)

半導体装置の製造方法

【課題】低コストかつ作業効率の高い半導体装置の製造方法を提供する。

【解決手段】シリコン基板110の上に回路パターンを形成し、回路パターンが形成されたシリコン基板110の上に層間絶縁膜140を形成する。層間絶縁膜140に対して第1の加速電圧でイオン注入を行い第1イオン層310を形成する。続いて第1の加速電圧より高い第2の加速電圧でイオン注入を行い第2イオン層320を形成する。その後、層間絶縁膜140を、第2イオン層320の波形上端部320Puが表出するまで研磨する。

(もっと読む)

層間絶縁膜の平坦化方法

【課題】配線層による層間絶縁膜の凹凸の影響を排除することで、平坦化を容易とすることができる層間絶縁膜の平坦化方法を提供する。

【解決手段】層間絶縁膜の平坦化方法は、まず、配線層12a,12bを形成し、高密度プラズマCVDにより配線層12a,12bを覆って第1HDP酸化膜13を形成し、テトラエトキシシランガスを用いたプラズマCVDにより第1HDP酸化膜13上にPL−TEOS酸化膜14を形成し、高密度プラズマCVDによりPL−TEOS酸化膜14上に、第2HDP酸化膜15を形成する。次に、PL−TEOS酸化膜14が露出するまでCMPにより第2HDP酸化膜15を研磨する。そして、PL−TEOS酸化膜14が除去されるまで、第2HDP酸化膜15とPL−TEOS酸化膜14とを同時にCMPにより平坦化する。そうすることで、平坦化された層間絶縁膜10を得ることができる。

(もっと読む)

プラズマ付着により成長させた基材構造

基材(6)およびプラズマ成長層(6a)を含む基材構造。得られる基材構造(7)の表面は、相関するスケーリング成分により特徴づけられる。該スケーリング成分は、粗さ指数α、成長指数βおよび動的指数zを含み、該成長指数βは0.2未満の値を有し、該動的指数zは6を超える値を有する。そのような基材構造を提供するための方法も開示する。 (もっと読む)

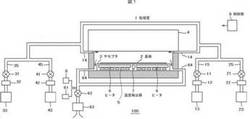

大気圧プラズマ処理装置、大気圧プラズマ処理方法及び大気圧プラズマ処理装置用の電極システム

【課題】高いキャリア移動度を示す有機薄膜トランジスタ素子及びその製造方法を提供することにあり、更には、非真空系の連続生産、例えば、所謂ロールツーロール(Roll to Roll)工程により製造するのに適しており、低コストの大量生産が可能になる有機薄膜トランジスタ素子及びその製造方法を提供することにある。

【解決手段】放電ガスを励起させて励起放電ガスを発生させる手段と、反応ガスと前記励起放電ガスとを接触させて前記反応ガスをプラズマ化させる手段と、を有し、前記プラズマ化した反応ガスを基材の表面に接触させて前記基材の表面処理を行う、大気圧プラズマ処理装置において、前記反応ガスが前記励起放電ガスに挟みこまれるようにして接触することを特徴とする気圧プラズマ処理装置。

(もっと読む)

低誘電率絶縁膜のダメージ回復方法及び半導体装置の製造方法

【課題】埋め込まれた金属の酸化、及びパターン欠損の発生を抑制しつつ、低誘電率絶縁膜自体の電気的特性を十分に回復できる低誘電率絶縁膜のダメージ回復方法を提供すること。

【解決手段】低誘電率絶縁膜を加工処理した後、低誘電率絶縁膜の表面に加工処理によって生じたダメージ性官能基を、疎水性官能基に置換し(ST.2)、低誘電率絶縁膜の表面に置換処理によって生じたデンス層の下に存在するダメージ成分を、紫外線加熱処理を用いて回復させる(ST.3)。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、しきい値電圧のばらつきを低減し、電気特性を安定させることを課題の一とする。また、オフ電流を低減することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に絶縁性酸化物を含む酸化物半導体層を積層し、酸化物半導体層とソース電極層又はドレイン電極層とが絶縁性酸化物を含む酸化物半導体層を介して接触するように薄膜トランジスタを形成することによって、薄膜トランジスタのしきい値電圧のばらつきを低減し、電気特性を安定させることができる。また、オフ電流を低減することもできる。

(もっと読む)

半導体装置の製造方法

【目的】層間絶縁膜内の電荷による電界への影響を緩和して、素子のリーク電流の減少と耐圧の向上を図ることができる半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜をSiH4とN2Oから形成される堆積酸化膜2aとTEOSとO2から形成されるTEOS酸化膜2bとの二層の複合膜とすることで、TEOS酸化膜2b中の電荷5による電界への影響を堆積酸化膜2aで緩和できて、素子のリーク電流が低減され、耐圧が向上する。その結果、良品率を向上させることができる。

(もっと読む)

シリコン酸化膜の成膜方法および半導体装置の製造方法

【課題】絶縁性の高いシリコン酸化膜を低温下で成膜することができるシリコン酸化膜の成膜方法を提供する。

【解決手段】シリコン酸化膜の成膜方法は、被処理基板Wを保持する保持台34の表面温度を300℃以下に保った状態でシリコン化合物ガス、酸化性ガスおよび希ガスを処理容器32内に供給し、処理容器32内にマイクロ波プラズマを生成し被処理基板Wにシリコン酸化膜を形成する工程と、酸化性ガスおよび希ガスを処理容器32内に供給し、処理容器32内にマイクロ波プラズマを生成し被処理基板W上に形成されたシリコン酸化膜をプラズマ処理する工程とを含む。

(もっと読む)

薄膜トランジスタの製造方法

【課題】酸化物半導体薄膜、特に、前駆体から熱変換され形成される酸化物半導体薄膜を有する薄膜トランジスタの製造方法において、半導体特性の向上およびその安定性が向上した生産効率の高い薄膜トランジスタを提供する。

【解決手段】基体310上に、ゲート電極302、ゲート絶縁膜303、酸化物半導体薄膜306を有する薄膜トランジスタの製造方法において、ゲート絶縁膜303が大気圧プラズマ法により形成されることを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板側から熱酸化膜、CVD酸化膜の2層を積層したゲート絶縁膜を有する半導体装置において、アニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することによる半導体基板等の歪みを低減する。

【解決手段】熱酸化膜とCVD酸化膜との間に、リンガラス膜を形成する。リンガラスは、シリコン酸化膜中にリン(P)を導入して軟化温度(ガラス転移温度)を低くした酸化膜であり、850〜900℃でリフローと呼ばれる流動現象が生じる。900℃以上で行われるCVD酸化膜のアニール処理時には、リンガラス膜がリフロー流動状態となり、熱酸化膜とCVD酸化膜と間で緩衝材として機能する。これによってアニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することが抑制され、ゲート絶縁膜や半導体基板の歪みが低減される。

(もっと読む)

金属層間誘電体による拡散防止バリヤ層を有する集積回路およびその製造方法。

【課題】ライン間キャパシタンスを減少できる構造を有する集積回路および不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止できる集積回路の製造方法を提供する。

【解決手段】低誘電率材料中での不純物の移動を防止できるキャップ層あるいはバリヤ層により、不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止する。集積回路は第一の誘電体層と集積回路のより上層の導電層間に拡散防止バリヤ層を堆積して製造される。拡散防止バリヤ層はその次の金属層で不純物を含む誘電体層へその場で形成され、さらに、研磨を含む処理が多層誘電体構造に対してなされる。キャップ層あるいはバリヤ層にその場堆積は不純物を含む層を雰囲気にさらすのを防止し、そしてキャップ層あるいはバリヤ層により、水分、水素あるいはそのたのものにより、層が汚染されるのを防止することができる。

(もっと読む)

低温ギャップフィル改善のための酸化シリコンCVDへの前駆体添加

基板上に酸化シリコン層を堆積させる方法は、一様な酸化シリコン成長速度が基板表面全域にわたって実現されるように、処理チャンバ中にシリコン含有前駆体、酸化性ガス、水、および添加剤前駆体を流入させることを伴う。実施形態により成長した酸化シリコン層の表面粗さは、添加剤前駆体を用いて成長させることにより低減させることができる。本発明の別の態様では、トレンチが、内部のボイドの数量が少なくおよび/またはサイズが小さい酸化シリコンフィラー材料で埋められるように、処理チャンバ中にシリコン含有前駆体、酸化性ガス、水、および添加剤前駆体を流入させることによって、表面上にトレンチを具備するパターン形成基板上に酸化シリコン層を堆積させる。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】スルーホールの側壁に湿性の高い層間絶縁膜が露出しない構造を、より少ない処理工程数で実現可能な半導体素子の製造方法を提供することを課題とする。

【解決手段】本発明の第1の態様に係る半導体素子の製造方法は、基板上に下層金属配線パターンを形成する工程と;前記下層金属配線パターンを覆うようにシリコン酸化膜からなる第1層間絶縁膜を形成する工程と;前記第1層間絶縁膜上にO3−TEOS膜または絶縁塗布膜からなる第2層間絶縁膜を形成する工程と;前記下層金属配線パターンの直上部に形成された前記第2層間絶縁膜を除去する工程と;前記第1及び第2層間絶縁膜上に第3層間絶縁膜として、シリコン酸化膜を形成する工程と;前記第1及び第3層間絶縁膜を貫通して前記下層金属配線に達するスルーホールを形成する工程と;を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】熱CVD法で素子分離溝に絶縁膜を埋め込む際に、アクティブエリアの変形を防止する。

【解決手段】本発明の半導体装置の製造方法は、シリコン基板1上に被加工膜を形成し、シリコン基板1及び被加工膜を加工して素子分離溝5を形成し、素子分離溝5に熱CVD法により絶縁膜6を埋め込む製造方法であって、絶縁膜6を埋め込む工程の熱CVD法の成膜条件を、素子分離溝5のうちのシリコン基板1の上面1aの高さ以下の部分を埋め込む絶縁膜6aの空孔率が5%以上となると共に、素子分離溝5のうちのシリコン基板1の上面1aの高さを越える部分を埋め込む絶縁膜6bの堆積速度が素子分離溝5のうちのシリコン基板1の上面1aの高さ以下の部分を埋め込む絶縁膜6aの堆積速度よりも小さくなる条件に設定した。

(もっと読む)

薄膜トランジスタの作製方法

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁層を形成し、ゲート絶縁層上に、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスとを用い、プラズマを発生させて、厚さ3〜10nm、好ましくは3〜5nmの第1の半導体層を形成する。次に、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを用い、プラズマを発生させて、非晶質半導体と、第1の半導体層を種結晶として部分的に結晶成長させて、形成される微結晶半導体で形成される複数の錐形状の凸部を有する第2の半導体層を形成する。次に、一導電型を付与する不純物元素が添加された半導体層を形成し、導電層を形成して、薄膜トランジスタを作製する。

(もっと読む)

41 - 60 / 210

[ Back to top ]