Fターム[5F064BB31]の内容

ICの設計・製造(配線設計等) (42,086) | ICの機能 (7,082) | 試験 (314)

Fターム[5F064BB31]に分類される特許

1 - 20 / 314

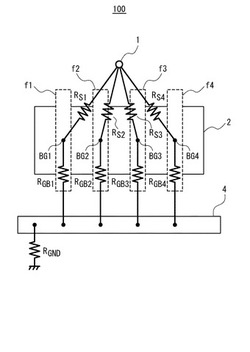

ノイズ解析モデル及びノイズ解析方法

【課題】解析対象回路内に設けられた素子のそれぞれに対する基板ノイズの影響を解析することができるノイズ解析モデル及びノイズ解析方法を提供すること。

【解決手段】本発明の一態様にかかるノイズ解析モデル100は、抵抗RS1〜RS4、抵抗RGB1〜RGB4及び接地抵抗RGNDを有する。抵抗RS1〜RS4は、ノイズ発生源から半導体基板を介して基板ノイズが伝搬する接続点1と、バックゲート直下の半導体基板中の点BG1〜BG4の間にそれぞれ接続される。抵抗RGB1〜RGB4は、バックゲート直下の半導体基板中の点BG1〜BG4とガードバンド4との間に接続される。接地抵抗RGNDは、ガードバンド4と接地電位との間に接続される。

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

半導体チップ

【課題】チップ面積が小さく低コストで誤動作が発生し難い半導体チップを提供する。

【解決手段】半導体チップ1をパッケージ3に搭載する場合は80個のパッドPAをパッケージ3の80個の端子TAに接続し、半導体チップ1をパッケージ5に搭載する場合は100個のパッドPA,PB,PCをパッケージ5の100個の端子TAに接続する。半導体チップ1の内部回路は、電極E1,E2が絶縁されている場合は80端子のマイクロコンピュータ4として動作し、電極E1,E2がボンディングワイヤWの端部によって短絡されている場合は100端子のマイクロコンピュータ4として動作する。したがって、パッケージの端子数を設定する専用パッドが不要となる。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体集積回路,および,半導体集積回路の検査方法

【課題】故障検査のために観測用フリップフロップ回路を配置することなく,故障検査を可能とする半導体集積回路,その検査方法を提供する。

【解決手段】第2の論理回路51の試験の際に試験モードを示す制御信号TSMが,故障検査用回路41に入力され,この試験モードに対応するテスト値が,論理回路51に入力されると,故障検査用回路41により,論理回路51の出力論理が,論理回路13に対応するフリップフロップ回路14に入力される。さらに,通常モード時に,論理回路13の出力論理が,故障検査用回路41により,論理回路13に対応するフリップフロップ回路14にそのまま入力される。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

1 - 20 / 314

[ Back to top ]