Fターム[5F064CC25]の内容

ICの設計・製造(配線設計等) (42,086) | 使用素子 (2,627) | シリコン以外の材料を用いているもの (59)

Fターム[5F064CC25]の下位に属するFターム

GaAs (8)

Fターム[5F064CC25]に分類される特許

1 - 20 / 51

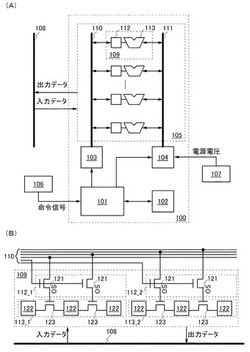

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

一方向性アンチヒューズ素子及びこれを用いた発光ダイオードユニット

【課題】1列に直列接続された各発光ダイオード(LED)素子の各々にそれぞれ1つのアンチヒューズ素子が並列接続されているLEDユニットにおいて、電源を誤って逆方向に接続した場合にも、LEDユニットを保護する一方向性アンチヒューズ素子を提供する。

【解決手段】1はカソード電極端子Kに接続されたカソード電極層、2はp型不純物層21及びn型不純物層22よりなる半導体層、3は絶縁層、4はボンディングワイヤ5によってアノード電極端子Aに接続されたアノード電極層、6は封止樹脂層である。カソード電極端子Kとアノード電極端子Aとの間に順方向電圧が印加された場合のみ、一方向性アンチヒューズ素子はアンチヒューズとして作用する。カソード電極端子Kとアノード電極端子Aとの間に逆方向電圧が印加された場合には、一方向性アンチヒューズ素子はアンチヒューズとして作用しない。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒューズ配線を溶断する際に素子分離構造や半導体基板に与えるダメージを抑制することができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板10と、半導体基板の主面の面内方向に互いに離間するように形成された一対の電極12A,12Bと、これら電極12A,12Bを被覆し、上面に凹部13cを有する下層絶縁膜13と、凹部13cに形成されたヒューズ配線20Cと、下層絶縁膜13及びヒューズ配線20Cを被覆する層間絶縁膜21と、層間絶縁膜21上に形成され、ヒューズ配線20Cの直上にレーザトリミング用の開口部1hを有する上層絶縁膜31とを備える。

(もっと読む)

電子素子の製造方法および電子素子

【課題】有機絶縁層を有する電子素子の配線短絡を簡素な工程により絶縁することが可能な電子素子の製造方法および電子素子を提供する。

【解決手段】配線層21,22の上に有機絶縁層12を形成したのち、配線層21,22の短絡部23に、有機絶縁層12に対して透過性を持つ波長のレーザ光LBを有機絶縁層12を介して照射、または基板11に対して透過性を持つ波長のレーザ光LBを基板11を介して照射する。レーザ照射領域24では短絡部23が消失して、配線層21と配線層22との間の絶縁が回復する。短絡部23の上下に接する有機絶縁層12または基板11は残されている一方、レーザ照射領域24(短絡部23が消失した部分)には空洞25が生じる。

(もっと読む)

半導体装置及びその作製方法

【課題】書き込み電圧が小さいアンチヒューズを提供する。

【解決手段】アンチヒューズは読み出し専用の記憶装置のメモリ素子に用いられる。アンチヒューズは、第1導電層、絶縁層、半導体層、及び第2導電層を有する。アンチヒューズに含まれる絶縁層は、原料ガス中にアンモニアを添加して形成した酸化窒化シリコンであり、層中に1.2×1021以上3.4×1021atoms/cm3以下の水素、または3.2×1020以上2.2×1021atoms/cm3以下の窒素を含むことで、低電圧での書き込みが可能となる。

(もっと読む)

電流ヒューズ、半導体装置及び電流ヒューズの切断方法

【課題】ヒューズ部を容易に切断する。

【解決手段】基体上に設けられるヒューズ部20と、前記ヒューズ部20の上層又は前記基体と前記ヒューズ部20の間の下層に配置され、かつ前記ヒューズ部20が通電した際に、前記ヒューズ部20の一部分と同電位となり、前記ヒューズ部20の一部分側から、前記一部分と相違する電位となる前記ヒューズ部20の他の部分の上層又は下層まで延在する導電部16と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】 ソース領域側だけに不活性イオン注入領域が形成される非対称型SOI電界効果トランジスタを容易に実現する半導体装置の製造方法を提供する。

【解決手段】 イオン注入前にトランジスタが形成される半導体層のゲート電極について対称構造をなす2つの電極のいずれか一方をソース又はドレインとして指定する電極指定データを予め保持する設計工程と、電極指定データに応じてソース領域側だけのイオン注入を可能にするためのイオン注入用マスクを製作するマスク製作工程と、対称をなす2つの電極を有する半導体層表面にフォトレジストを塗布しイオン注入用マスクを用いて露光してフォトレジストの少なくともソース領域に対応する部分を除去するレジスト形成工程と、レジスト形成工程の実行後、イオン注入用マスクに対応して残されたフォトレジストを有する半導体層表面からイオンを注入する工程と、を備える。

(もっと読む)

炭化珪素絶縁ゲート電界効果トランジスタを用いたインバータ回路および論理ゲート回路

【課題】動作速度を高速化できる SiC MISFETで構成された論理ゲート回路デバイスを得る。

【解決手段】nチャネルエンハンスメント型SiC MISFET(22)と、nチャネルデプリーション型SiC MISFET(22、22b)とでインバータ、NAND/NOR論理ゲート回路を構成する。

(もっと読む)

半導体集積回路装置およびその設計方法

【課題】オフリーク電流を抑制でき、動作速度および駆動力に優れた半導体集積回路装置およびそのような半導体集積回路装置の設計方法を提供する。

【解決手段】スタンダードセルを配置して動作タイミングおよび消費電力の少なくともいずれかを解析し、得られた解析結果に基づいて特性の改善が望まれるスタンダードセルを着目セルとして特定し、ウェル近接効果の影響を考慮して前記着目セル周辺の空き領域の配置および形状を最適化し、最適化された空き領域のうち、ウェル近接効果を利用できる空き領域を特定し、特定された空き領域のレイアウト、または特定された空き領域および前記着目セルのレイアウトを、所望の特性に応じてウェル近接効果の影響が変動するように変更する。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】

使用現場で使用者や顧客の要望に応じて、回路システムを形成することのできる薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】

薄膜トランジスタ装置において、TFTにより構成した複数の集積回路ブロック1,2と、これらの集積回路ブロックを相互に接続するための網目状に交差したマトリックス配線3、4、5、6を設ける。相互の集積回路ブロック間の接続は、使用現場で使用者や顧客の要望に応じて導電性材料を印刷等により、マトリックス配線の各々の配線交差部に選択的に設けることにより行い、所望の回路システムを構成する。

(もっと読む)

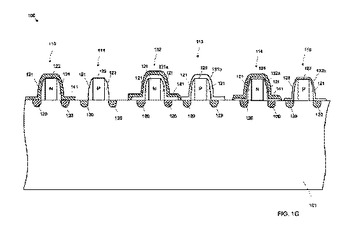

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】供給位置の片寄りを緩和して面内の電源電位差の抑制可能な配線の半導体装置を

提供する。

【解決手段】マクロセル35のある半導体基板5と、半導体基板5の上、直線状で、両端

部で高電位パッド11に接続された幹配線22a、及び幹配線22aと交差した枝配線2

2bを有する上位高電位電源配線21と、幹配線22aの面にあり交互に並行して直線状

で、両端部で低電位パッド13に接続された幹配線24a、及び幹配線24aと交差した

枝配線24bを有する上位低電位電源配線23と、半導体基板5と上位高電位電源配線2

1の間で、幹配線22aに並行して直線状に伸び、マクロセル35に接続し、上位高電位

電源配線21にビアプラグ31で接続された下位高電位電源配線25と、下位高電位電源

配線25の面にあり交互に並行して直線状で、マクロセル35に接続し、上位低電位電源

配線23にビアプラグ31で接続された下位低電位電源配線27とを備える。

(もっと読む)

アンチヒューズ、アンチヒューズ形成方法、および、不揮発性メモリ素子の単位セル

【課題】MOSトランジスタから成るアンチヒューズのゲート絶縁膜を安定的に破壊させて、読み取り動作時のデータセンスマージンを改善させ、動作の信頼性を向上させることができるアンチヒューズおよびその形成方法、そしてこれを備えた不揮発性メモリ素子の単位セルを提供する。

【解決手段】本発明は、基板上に形成されたゲート絶縁膜と、本体部と、前記本体部から伸長された複数個の突出部を備え、前記本体部および前記突出部が前記ゲート絶縁膜上に接するように前記ゲート絶縁膜上に形成されたゲート電極と、前記突出部の側壁に露出した前記基板内に形成された接合領域と、を備える。

(もっと読む)

半導体集積回路の設計方法,設計装置および製造方法

【課題】ウェーハ内のチップ間ばらつきを解決してチップ歩留まりの向上を図る。

【解決手段】プロセスばらつきのデータベースを作成するステップ(S8,S9)と、前記作成されたデータベースからウェーハ上のプロセスばらつきを算出するステップ(S3A)と、前記算出されたプロセスばらつきから、配線抵抗および配線容量のRC定数を算出するステップ(S3B)と、前記ウェーハ上のプロセスばらつきに応じた配線幅を算出して配置するステップ(S3C)と、を備えるように構成する。

(もっと読む)

垂直コンタクト部を備える電気回路

【解決手段】 本発明は、一の平面内に広がる平面状の基板上に形成される少なくとも2つのユニットセルを備える電気回路であって、ユニットセルはそれぞれ、異なる機能を持つコンタクトポイントを少なくとも2つ有しており、基板および/またはユニットセルの上に配設されている少なくとも1つの誘電層と、コンタクトポイントおよび/または基板の上方に、平面に対して平行に配設されている少なくとも2つのコンタクト面とを備え、同一の機能を持つコンタクトポイントは、誘電層を貫通している少なくとも1つの貫通コンタクト部を介して、同一の機能を持つコンタクトポイントの少なくとも一部のための少なくとも1つの共通のコンタクト面に電気的に接続されており、対応するコンタクト面を介して、外部と共通に接触する電気回路に関する。 (もっと読む)

ゲート電極下に金属シリサイドのパイプを有する電気ヒューズ

【課題】 信頼性が向上しているとともに比較的低い電圧でプログラムされることが可能な電気ヒューズを提供する。

【解決手段】 電気ヒューズは、半導体基板と、導電性または一部導電性のポリシリコンを具備するゲートと、を具備する。半導体基板はゲートの近くにおいてアモルファス化されたパイプ領域を具備するとともにパイプ領域に隣接する第1、第2電極領域を具備する。電気ヒューズは、第1、第2電極領域内の半導体基板上の金属シリサイド層をさらに具備する。金属シリサイドは、ニッケル・シリサイド、コバルト・シリサイド、チタン・シリサイド、パラジウム・シリサイド、プラチナ・シリサイド、エルビウム・シリサイド、およびこれらの組合せからなる群から選択される。

(もっと読む)

電子装置の製造方法、メモリ回路の動作方法、および電子装置

半導体基板(10)上に形成された誘電体層(12)を備える、電子装置。誘電体層(12)上には、代表長さを有するポリシリコンヒューズ構造(14)が形成される。ポリシリコンのヒューズ構造の第1部分(141)と第2部分(143)は、シリサイド化さる。ポリシリコンヒューズ構造(114)のうち、第1部分(141)と第2部分(143)の両方に隣接する第3部分(142)は、シリサイド化されない。  (もっと読む)

(もっと読む)

半導体装置、および集積回路の設計方法

【課題】小型化および製造コストの削減を図り易いスタンダードセル方式の半導体装置を得ること。

【解決手段】所定の回路が形成されている複数種類の機能セルを配置・配線することで形成された集積回路を備え、機能セルそれぞれにおけるy軸方向の長さは互いに同じで、x軸方向の長さは該機能セルの種類毎に異なるスタンダードセル方式の半導体装置を構成するにあたり、グリッド方式のレイアウトツールを用いて機能セルを配置・配線する際の配線グリッドの間隔をDとしたときに、x軸方向の長さを間隔Dの整数倍から外すことで回路の形成に利用されない余剰領域Rを削減した機能セルFC1を集積回路に含ませ、これにより当該集積回路の形成に利用されない余剰領域を低減させてチップサイズを小さくして、1枚のシリコンウェハやSOI基板等から切り出される個数を増加させる。

(もっと読む)

1 - 20 / 51

[ Back to top ]