Fターム[5F064EE09]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線幅 (593)

Fターム[5F064EE09]の下位に属するFターム

電流に応じた配線幅 (112)

Fターム[5F064EE09]に分類される特許

1 - 20 / 481

閾値テーブルの作成方法、クロストーク解析の悲観性削減方法、クロストーク解析方法、及びクロストーク解析プログラム

ビア故障から保護するための方法及び構造

設計支援装置

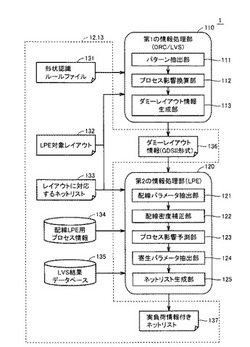

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

ESD耐量検証方法及びESD耐量検証装置

【課題】 ESD耐量の低いパス及びその原因素子を安易且つ良好に特定できる検証方法及び検証装置を提供する。

【解決手段】 設計用回路データから2つの検証対象端子とその間に接続される検証対象素子を特定し、電流方向を設定し、検証対象素子の夫々を識別情報、電流方向別の特性情報及び耐量情報を記憶した素子シンボル情報を備える素子シンボルで表した等価回路データを作成し、2ノード間の特性情報及び耐量情報を記憶可能な分岐点シンボルを用い、検証対象端子に対応する分岐点シンボルを頂点とし、等価回路データをツリー構造データに変換し、素子シンボル情報に基づいて分岐点シンボル情報を作成し、頂点の分岐点シンボルの耐量情報が基準耐量以下の場合に、耐量情報に基づいて耐性が最も低い最低耐量経路と耐量制限シンボルを特定し、当該耐量制限シンボルに対応する設計用回路データの素子を特定する。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

半導体装置

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】レイアウトデータの検証を行うLVS処理やDRC処理と、OPC処理には、プログラムの実装に重複(冗長)な処理が存在する。そこで、これらの処理を、統合することも考えられる。しかし、そのような統合を実際に行えば、プログラムの変更が大規模になり、半導体設計装置のコストを上昇させてしまう。そのため、既存のリソースを有効活用しつつ、OPC処理の処理スピードを向上させた半導体設計装置が、望まれる。

【解決手段】半導体設計装置は、半導体集積回路のレイアウトデータの検証を行うレイアウトデータ検証部と、レイアウトデータ検証部が生成するOPC処理用中間データを用いて、OPC処理を行うOPC処理部と、を備えている。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラム

【課題】マクロの全端子で配線が引き出し可能かを判定できるレイアウト設計装置、レイアウト設計方法およびレイアウト設計プログラムを提供する。

【解決手段】記憶部11は内部にマクロを含んだ多層回路の階層レイアウトの設計データを記憶する。チャネル数算出部13は設計データに基づいて、マクロの各端子から所定の配線層まで配線を引き出すために使用可能なチャネル数を端子毎に算出する。経路算出部15は算出したチャネル数の少ない端子から順に、端子から所定の配線層まで配線を引き出すための経路を算出する。経路判定部16はマクロの全ての端子について引き出し経路を算出できたか否かを判定する。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

半導体集積回路装置

【課題】チップ面積を増加させることなく、効率良くリーク電流を抑制することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は論理が同一のセルA−1,B−1,C−1を備えている。セルB−1はセルA−1よりセル幅W2が大きいが、MOSトランジスタのゲート長L1はセルA−1と等しい。セルC−1は、セルB−1とセル幅W2が等しいが、ゲート長L2が大きいMOSトランジスタを有しており、セルA−1,B−1と比べて回路遅延は遅くなるがリーク電流は小さくなる。このため例えば、空き領域に隣接したセルA−1をセルB−1に置き換え、タイミングに余裕があるパスにおけるセルB−1をセルC−1に置き換えることによって、チップ面積を増加させることなく、リーク電流を抑えることができる。

(もっと読む)

原版データの生成方法、原版作成方法、原版データを作成するためのプログラム及び処理装置

【課題】 微細なパターンを精度よく形成する原版のデータを生成する生成方法を提供する。

【解決手段】 光源からの光を用いて原版を照明する照明光学系と、前記原版のパターンを基板に投影する投影光学系とを備える露光装置に用いられる原版のデータをコンピュータによって生成する生成方法であって、近似空中像に基づいて主パターンを決定し、補助パターンを挿入することで原版のデータを生成する生成方法を提供する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム

【課題】半導体集積回路の設計において、EM検証結果がNGとなる確率を低減する。

【解決手段】半導体集積回路の設計方法は、(A)設計対象回路のネットリスト中のネットに仮の寄生容量及び0個以上の仮の寄生抵抗が付加された寄生RC付きネットリストを作成するステップと、(B)寄生RC付きネットリストを用いて回路シミュレーションを行い、ネットにつながるそれぞれの素子端子の電流である素子端子電流及び仮の寄生容量の電流である寄生容量電流を算出するステップと、(C)寄生容量電流をそれぞれの素子端子に分配することによって、素子端子電流の値を変更するステップと、(D)変更後の素子端子電流に基づいて、ネットに関する配線幅制約を算出するステップと、を含む。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、半導体装置のレイアウト方法

【課題】新たな要因に起因したクラックの発生を抑制すること。

【解決手段】第1のAl配線31と絶縁膜33とを含む第1のAl配線層30と、第2のAl配線41と絶縁膜43とを含む第2のAl配線層40と、複数の第3のAl配線51と絶縁膜52とを含む第3のAl配線層50と、第1のAl配線31と第2のAl配線41とを接続する第1のビア32と、第2のAl配線41と第3のAl配線51とを接続する第2のビア42とを有し、少なくとも一部の第3のAl配線51は隣り合う第3のAl配線51同士の間隔Bが2.25μm以下である隙間60を形成しており、平面視で隙間60の中の少なくとも一部は第1のAl配線31及び第2のAl配線41と重ならない領域を有し、隙間60を形成するように対峙した第3のAl配線51の対峙方向の配線幅Cは15μmより大きく、第2のビア42同士の間隔Fは第2のビア42の径Gの3倍以上である半導体装置。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

1 - 20 / 481

[ Back to top ]