Fターム[5F064EE18]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 配線の位置、座標 (294) | 配線の対称性 (65)

Fターム[5F064EE18]に分類される特許

1 - 20 / 65

半導体装置

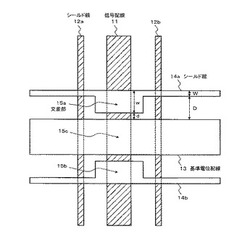

【課題】配線間の影響を抑制することができる多層配線を有する半導体装置を実現する。

【解決手段】本発明の実施形態における半導体装置は、下層の配線層に第1の方向に沿って形成された信号配線11と、下層の配線層と絶縁膜を介して配置される上層の配線層に第1の方向と交差する第2の方向に沿って形成された基準電位配線13と、 上層の配線層に基準電位配線13に沿って近接して形成されたシールド線14a、14bと、を有し、信号配線11と基準電位配線13の交差部15cにおいて基準電位配線13とシールド線14a、14bとの距離が他の部分に比べてより狭くなっていることを特徴とする。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体集積回路設計装置、半導体集積回路設計方法及びプログラム

【課題】メガマクロブロックとの重なりが少ないクロック構造を広い解空間において効率良く探索できるようにすること。

【解決手段】チップ情報に含まれるチップ領域を覆う格子を設定する格子設定部と、チップ領域の中心から格子の各セルの中心へクロック信号を分配するクロック構造であってチップ領域を格子に含まれるセルの境界に沿って縦方向又は横方向に2分割することを再帰的に繰り返すことにより生成されたクロック構造を構成する線分の候補を候補線分として生成する候補線分生成部と、チップ領域の分割方向及び分割順序を節点及び枝として有する2分木を生成する2分木生成部と、候補線分に設定された重みの総和である目的関数が最小となるように2分木の各節点の分割方向を選択する分割方向選択部と、各節点の分割方向が選択された2分木によって表されるクロック構造を生成するクロック構造生成部と、を有する。

(もっと読む)

対称的な電気挙動を有する物理的に非対称的な半導体装置を採用するシステム及び方法

互いに平行に配置され、それらの間に空間を画定する第1の細長い構造体及び第2の細長い構造体を備える集積回路装置。集積回路装置はまた、第1及び第2の細長い構造体間の空間に分布された導電性構造体を備える。導電性構造体の少なくとも第1の1つの導電性構造体は、第2の細長い構造体よりも第1の細長い構造体に近く配置される。導電性構造体の少なくとも第2の1つの導電性構造体は、第1の細長い構造体よりも第2の細長い構造体に近く配置される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置のレイアウト設計方法

【課題】アナログ回路に利用される抵抗素子の配置領域面積を低減し、抵抗素子の相対精度を向上させる半導体装置及び半導体装置のレイアウト設計方法を提供する。

【解決手段】一の方向に並列配置されたトランジスタ素子(トランジスタ素子Q1及びトランジスタ素子Q2)と、トランジスタ素子上に層間絶縁膜(層間絶縁膜14)を介して形成された抵抗素子(抵抗素子R1及び抵抗素子R2)を有し、平面視において抵抗素子の長さ方向はトランジスタ素子のチャネル幅方向に直交する。

(もっと読む)

2層式トランス

【課題】それぞれ少なくとも2つの巻数からなる2つのコイルを備え、2つの導電層に実現可能であって、これによりコイルの端子がこの構造の反対側に配置される、対称型トランスのための構造を提供する。

【解決手段】積層コイル構造を持つ対称型トランスは、それぞれ少なくとも2つの巻線を有する2つのコイルを備える。該構造は、4つの同じ基本エレメントを備え、各基本エレメントは、前記コイルの一部のための導電経路を提供するものである。トランスの端子は、該構造の反対側に配置されており、構造はチェーン式に容易に接続できる。本発明はまた、こうした構造を備えた半導体デバイスに関する。

(もっと読む)

半導体装置

【課題】局所的な電圧降下を効果的に抑制できる電源配線構造を有した半導体装置を提供する。

【解決手段】第1配線層は複数の第1配線ブロック10を含み、当該各第1配線ブロック10には、第1電位を持ち且つ少なくとも二方向以上に延びる第1配線11と、第1電位と異なる第2電位を持ち且つ少なくとも二方向以上に延びる第2配線12とが配置されている。第2配線層は、隣り合う一対の第1配線ブロック10における第1配線11同士を電気的に接続する第3配線21と、当該一対の第1配線ブロック10における第2配線12同士を電気的に接続する第4配線22とを含む。

(もっと読む)

半導体装置及びそれを用いた表示装置のデータドライバ

【課題】省面積化を図るデコーダ及び、それを用いた省面積(低コスト)のデータドライバを提供。

【解決手段】トランジスタ(21〜24)の配列と、第1の配線層(71)に配置され前記配列上方を互いに離間して行方向に延在される複数の参照電圧信号線と、第2の配線層(72)に配置され、前記配列上方を互いに離間して行方向に延在される複数の参照電圧信号線を備え、行、列方向に隣接するトランジスタの拡散層(56)には、互いに異なる配線層の参照電圧信号線が接続される。

(もっと読む)

半導体装置

【課題】従来のプログラマブルな半導体装置であるFPGAやMPLDはコストパフォーマンスが悪く、かつ長い信号線に対する配慮が不充分であった。

【解決手段】メモリと、アドレス−データ対を有する複数のMLUTから構成されるMLUTブロックにフリップフロップを内蔵した。また隣接するMLUT間の近距離配線には交互配置配線を導入し、隣接していないMLUT間の配線には専用の離間配線、更にはトーラス配線網を設けた。

(もっと読む)

半導体装置

【課題】チップ面積を縮小することができ、かつコンタクト間の短絡を防止することができる半導体装置を提供する。

【解決手段】電源配線Paは第1方向に延びている。第1および第2ゲートG1、G2のそれぞれは、第1方向と交差する第2方向に延びる第1および第2端部領域RA1、RA2を含む。第1および第2端部領域RA1、RA2は、第1方向において互いに第1間隔S1を空けて配列されている。絶縁膜は、第1および第2端部領域RA1、RA2の間の少なくとも一部を埋め、平面視において第2の方向に沿って第1および第2端部領域RA1、RA2の間を通る空隙部VDを有する。電源コンタクトCPaは第1および第2端部領域RA1、RA2の間の領域の第2方向に沿った延長領域から離れて配置されている。

(もっと読む)

半導体集積回路装置

【課題】チップへの回路セルの実装率を保ちつつ、微細化の進んだ半導体素子および配線の均等性を保つことのできる技術を提供する。

【解決手段】NAND回路セルを形成するnチャネル型MISFETQn2およびnチャネル型MISFETQn3のそれぞれのゲート電極4を同一ノードとし、同じ入力信号に従って同時にオン・オフ動作を行う構成とする。nチャネル型MISFETQn2およびnチャネル型MISFETQn3は隣接して配置し、電気的には直列に接続された構造とする。また、NAND回路セルを形成pチャネル型MISFETQp3およびpチャネル型MISFETQp4のそれぞれのゲート電極4を同一ノードとし、同じ入力信号に従って同時にオン・オフ動作を行う構成とする。pチャネル型MISFETQp3およびpチャネル型MISFETQp4は隣接して配置し、電気的には直列に接続された構造とする。

(もっと読む)

データ処理装置、データ処理方法およびプログラム

【課題】クロック・スキューを最小にし、末端の配線構造の効率的な設計を支援し得るデータ処理装置を提供する。

【解決手段】データ処理装置20は、レイアウト領域に設定された複数のサブ領域を、配線が設けられるべき局所領域と配線が設けられないダミー領域とに分類する領域設定部22Bと、これらサブ領域内にクロック・スキューを最適化する仮想配線の規則構造を形成する規則構造生成部22Cと、当該形成された規則構造のうちダミー領域内に形成された仮想配線を、ダミー領域と局所領域との間の境界線を対称軸として折り返すことにより配線パターンを構成する配線構築部22Dと、を備える。

(もっと読む)

半導体集積回路装置

【課題】高電位電源配線と低電位電源配線との間の電位差の平面分布を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】高電位電源に接続されるパッド11と、上位の配線層に配置され、パッド11と接続され、幅の広いL字形を組み合わせた十字形を有する幹配線13と、幹配線13と同じ配線層に配置され、幹配線13より狭い幅を有し、幹配線13と接続され、幹配線13を2辺として形成する矩形に含まれる領域にそれぞれ分布する枝配線15と、低電位電源に接続されるパッド21と、下位の配線層に配置され、パッド21と接続され、幅の広いL字形を有し、投影面上で幹配線13に対向する位置に配置された幹配線23と、幹配線23と同じ配線層に配置され、幹配線23より狭い幅を有し、幹配線23と接続され、幹配線23を2辺として形成する矩形に含まれる内側の領域にそれぞれ分布する枝配線25とを備える。

(もっと読む)

1 - 20 / 65

[ Back to top ]