Fターム[5F082BC03]の内容

Fターム[5F082BC03]の下位に属するFターム

相補 (129)

Fターム[5F082BC03]に分類される特許

1 - 20 / 155

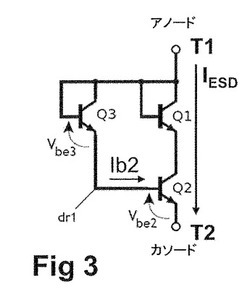

低減したクランプ電圧を有するESD保護デバイス

【課題】寄生容量に悪影響を与えることなく、より低いクランプ電圧が達成できるESD保護回路を提供する。

【解決手段】ESD保護回路は、第1および第2端子(T1,T2)の間にある主要なESD電流伝導経路において、複数のバイポーラトランジスタ、即ち、複数のESD電流伝導トランジスタ(q1,q2,q4)を備え、ESD電流伝導トランジスタの少なくとも1つ(q1)と並列に接続され、ESDイベントの発生時に、ESD電流伝導トランジスタの1つ又はそれ以上(q2)に駆動電流(Ib2)を伝導するために設けられた少なくとも1つの駆動トランジスタ(q3)をさらに備える。

(もっと読む)

電圧検知回路

【課題】高精度で低コストの電圧検知回路を提供する。

【解決手段】パワーオンリセット回路は、分圧回路1、バイポーラトランジスタQ1,Q2、抵抗素子R1,R2、およびベース電流補償回路10を備える。分圧回路1の出力電圧VINがバンドギャップ電圧VBGの場合、バイポーラトランジスタQ1,Q2のコレクタ電流I1,I2が一致する。電圧補償回路10は、電流I1に基いてバイポーラトランジスタQ1,Q2のベース電流の和に相当する電流I6を生成し、その電流I6をバイポーラトランジスタQ1,Q2のベースに供給する。したがって、バイポーラトランジスタQ1,Q2の各々のベース電流が大きい場合でも、高い検出精度が得られる。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体集積回路装置

【課題】絶縁素子分離型のバイポーラトランジスタの放熱性を改善する。

【解決手段】薄い半導体層の第1のエリアに配置された第1のトランジスタと、薄い半導体層の第2のエリアに配置された第2のトランジスタで構成される回路部と、を備え、第1のトランジスタは、並列接続された複数のバイポーラトランジスタ素子を構成する複数の単位能動領域の配列全体を囲って配置された素子分離溝を含み、素子分離溝を能動領域から少なくとも1μm離間して設け、能動領域で生成される熱を単位能動領域を囲んで存在する半導体領域から外方に放熱させる構成を備えてなり、第2のトランジスタは、バイポーラトランジスタ動作を行う単位能動領域と、単位能動領域を取り囲んで形成され単位能動領域から1μm以下の位置に配置された素子分離溝を含む。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことを容易に可能にする。

【解決手段】ESD保護素子101の高濃度不純物領域121SH,120DH,122SHを、ゲート電極111G,112Gの下方に形成しない。高濃度不純物領域121SH,120DH,122SHを、半導体基板100の面(xy面)にて、少なくとも低濃度不純物領域121SL,121DL,122DL,122SLを介してゲート電極111G,112Gの側部に位置するように形成する。また、高濃度不純物領域121SH,120DH,122SHを、低濃度不純物領域121SL,121DL,122DL,122SLおよび不純物領域121SM,120DM,122SMよりも深い位置まで形成する。

(もっと読む)

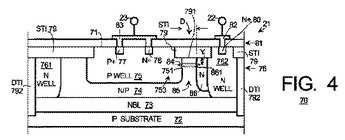

ESD保護デバイスおよび方法

関連するデバイスまたは回路24を保護する静電気放電(ESD)保護クランプ21、21’、70、700は、バイポーラ21、21’、70、700を備える。アバランシェ降伏が、上にある誘電体・半導体界面791から離れ、デバイス70、700のベース領域74、75の部分84,84以内に望ましく起こるように向かうベース75およびコレクタ86領域のドーパントを構成される。例えば、半導体ダイまたはウェハのトランジスタ21、21’、70、700の異なる方位配向のおかげで、ESDトリガ電圧の最大変化(△Vt1)MAXはベース・コレクタ間隔寸法Dの関数である。トリガ電圧一貫性および製造歩留まりが改良される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

半導体装置

【課題】ドレイン端での電流集中を防止して静電放電に対する耐性に優れた半導体装置を提供する。

【解決手段】保護素子1は、MOS構造のデバイスの一部に、縦型バイポーラトランジスタQ1と寄生バイポーラトランジスタQ2とを形成した構造になっている。N+ドレイン領域3とゲート直下のチャネル領域4との間にはNドリフト領域5が形成されている。N+ソース領域6に隣接してP+ベースコンタクト領域7が形成されている。ソース側に縦型トランジスタQ1を形成して、静電放電時に発生したホール電流を縦型トランジスタQ1に流すようにしたため、N+ドレイン領域のベース側端部での電流集中を緩和できる。

(もっと読む)

ESD保護素子

【課題】ESD耐量及びノイズ耐性を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、NPNバイポーラトランジスタTr1と、一端がパッド10に接続されたトリガ素子20とを具備する。NPNバイポーラトランジスタTr1は、第1ベース拡散層204と、パッド10に接続されたコレクタ拡散層4と、第1ベース拡散層204上に形成され、第1配線L1を介してトリガ素子20の他端に接続されたトリガタップ1と、第1ベース拡散層204上に形成され、第1配線L1と異なる第2配線L2を介してGNDに共通接続されたエミッタ拡散層2及び第2ベース拡散層3とを備える。

(もっと読む)

高利得ワイドバンドギャップ・ダーリントン・トランジスタ及び関連する製造方法

パッケージ化電力電子デバイスが、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ・ドライバ・トランジスタ(112)と、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ出力トランジスタ(116)とを含む。出力トランジスタのコレクタ端子は、ドライバ・トランジスタのコレクタ端子に結合され、出力トランジスタのベース端子は、ドライバ・トランジスタのエミッタ端子に結合され、ダーリントン対をもたらす。平面図における出力トランジスタの面積は、ドライバ・トランジスタの面積より少なくとも3倍大きい。例えば、出力トランジスタのドライバ・トランジスタに対する面積比は、約3:1から約5:1までの間とすることができる。関連するデバイス及び製造方法についても説明される。 (もっと読む)

バイポーラ・トランジスタ及びその製造方法

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

1 - 20 / 155

[ Back to top ]