Fターム[5F083AD10]の内容

Fターム[5F083AD10]に分類される特許

261 - 278 / 278

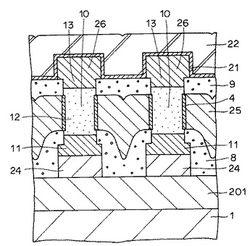

半導体装置の製造方法

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜13が設けられる。キャパシタ絶縁膜13を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面ストラップの高さにばらつきによって生じる、表面ストラップのシリサイド化を防止できる半導体装置を提供すること。

【解決手段】 半導体装置は、半導体基板1と、半導体基板1上に形成され、開口部12を有する絶縁膜10と、開口部12内に埋め込まれ、表面ストラップ13と、表面ストラップ13上に設けられ、絶縁膜10よりも小さいエッチングレートでエッチングできるたサリサイドブロック14と、半導体基板1内に形成され、表面ストラップ13と電気的に接続するトレンチキャパシタの蓄積電極4と、半導体基板1の表面に形成され、表面ストラップ13を介して蓄積電極4と電気的に接続するソース/ドレイン領域16とを備えている。

(もっと読む)

容量素子とその製造方法

【課題】 キャパシタ誘電体膜の歪みの低減、比誘電率の増大、及びリーク電流の低減の全てを同時に実現することが可能な容量素子とその製造方法を提供すること。

【解決手段】 シリコン基板(基材)1と、シリコン基板1の上に形成された下地絶縁膜2と、下地絶縁膜2の上に下部電極4a、キャパシタ誘電体膜5a、及び上部電極6aを順に形成してなるキャパシタQとを有し、キャパシタ誘電体膜5aが、(Ba1-y,Sry)mYpTiQO3+δ(0<p/(p+m+Q)≦0.015、−0.5<δ<0.5)で表される材料により構成されることを特徴とする容量素子による。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】キャパシタ容量およびデータ保持特性をさらに向上させることができる半導体記憶装置とその製造方法を提供する。

【解決手段】半導体基板と、半導体基板に形成されたトランジスタTrと、半導体基板に形成されたトレンチに形成され、トランジスタの一方のノードに接続する第1記憶ノード電極を有する第1メモリキャパシタCtと、トランジスタを被覆して形成された層間絶縁膜と、層間絶縁膜上に形成され、一方のノードに接続する第2記憶ノード電極を有する第2メモリキャパシタCsと、層間絶縁膜を貫通して形成され、第1記憶ノード電極と第2記憶ノード電極を接続する記憶ノードコンタクトプラグとを有し、第1メモリキャパシタ、第2メモリキャパシタおよびトランジスタを有するメモリセルが複数個配置されている構成とする。

(もっと読む)

トランジスタ、メモリセルアレイ、および、トランジスタ製造方法

【課題】トレンチ型DRAMメモリセルの形成において、垂直型トラジスタとトレンチ型キャパシタの接続を容易化し、高集積化する。

【解決手段】第1および第2ソース/ドレイン領域と、該第1および第2ソース/ドレイン領域を接続する、半導体基板の中に配置されたチャネル領域と、ゲート電極とを含み、該ゲート電極は、上記第1および第2ソース/ドレイン領域間に流れる電流を制御するために、上記チャネル領域に沿って配置され、該チャネル領域から電気的に絶縁されている。また、上記チャネル領域では、該チャネルがリッジ状の形をなしたフィン領域を有している。この「リッジ状」とは、1つの上面と、第1ソース/ドレイン領域と第2ソース/ドレイン領域とを接続する線に対して(断面図では)垂直である2つの側面とからなる。この上面は、半導体基板の表面よりも下に配置されており、ゲート電極は、この上面および2つの側面に沿って設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ素子分離の機械的応力を制御した構造を有するロジックLSIと、このロジックLSIの製造プロセスを用いて製造可能な1トランジスタ+1キャパシタ型のメモリ素子とを混載しうる半導体装置及びその製造方法を提供する。

【解決手段】トレンチ16a及びトレンチ16bが形成された半導体基板10と、トレンチ16aの内に形成されたシリコン窒化膜20を含むライナー膜とシリコン酸化膜系の絶縁膜とを有する素子分離膜32aと、トレンチ16bの底部に埋め込まれた素子分離膜32bと、トレンチ16bの上部の側壁部分に形成され、第1の電極としての不純物拡散領域40と、シリコン酸化膜系の絶縁膜よりなるキャパシタ誘電体膜43と、第2の電極46とを有するキャパシタとを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ドライエッチングにより半導体基板やポリシリコン層に生じるダメージ層を効果的に除去して、寄生抵抗や接合リークが低減された半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記絶縁膜を、ドライ工程によりエッチングする工程と、前記エッチングにより前記半導体基板上に生じたダメージ層を、熱分解した原子状の水素により、所定の温度下で除去する工程とを含む。

(もっと読む)

半導体装置

【課題】 ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】 ソース/ドレイン領域の一方になり、かつビット線にもなる第1の不純物拡散層24の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】水素の触媒作用によるコンタクトプラグ不良を防止する。

【解決手段】ソース領域、ドレイン領域およびゲートからなるトランジスタが集積化された半導体基板上に、前記ソース領域またはドレイン領域に接続されたコンタクトプラグと、前記コンタクトプラグに接続された下部電極と、前記下部電極の間に埋め込まれた酸素バリアを有する絶縁膜と、前記容量絶縁膜に形成された上部電極からなる強誘電体キャパシタにおいて、前記下部電極が酸素に対する導電性バリアを含み、さらに前記下部電極と絶縁膜との間に前記下部電極との反応を防止するための絶縁性反応防止膜を備えた構造になっている。

(もっと読む)

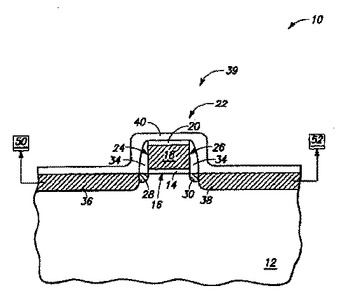

キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法

プレーナ型であることが好ましいトランジスタ(142)とキャパシタ(144)とを有する集積回路構造(140)が開示されている。キャパシタ(44)の下部電極は、トランジスタ(142)のチャネル領域と共に、1つのSOI基板に配置されている。回路構造(140)は、簡単に製造でき、優れた電子特性を有している。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 データの破壊を効果的に防止する。

【解決手段】 一対のメモリセルMCL、MCRのドレイン拡散領域14、ソース拡散領域15にシリサイド層18が埋め込まれ、シリサイド層18の底面はシリコン酸化膜11まで達している。

(もっと読む)

半導体装置の製造方法

【課題】 基板面積の増大なしにキャパシタを容量増大できるDRAM又はこれとロジック回路とを混載した半導体装置の製造方法の提供。

【解決手段】 半導体装置の製造方法は次の通りである。基板上面に第1の絶縁膜50で埋められたトレンチを形成。第1の絶縁膜の一部の上部を除去し、トレンチ内及び基板の上面上に第2の絶縁膜を形成し、その上に導体膜を形成。導体膜及び第2の絶縁膜をパターニングし、ゲート電極16a、プレート電極16b及び容量絶縁膜15を形成。ゲート電極及びプレート電極をマスクとし、イオン注入によりメモリトランジスタの低濃度ドレイン拡散層17b及びソース拡散層18を形成。ゲート電極、プレート電極の側面上に、各々第1、第2のサイドウォール25a、25bを形成。尚、プレート電極は基板の上面の一部とトレンチの露出している側面とに亘る領域上に形成され、ソース拡散層は第1、第2のサイドウォールによって覆われる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 誘電体膜の段差被覆性がよく、かつ誘電体物質の廃棄量を少なくする。

【解決手段】 下地膜8上に、パターニングされた下部電極11を形成する工程と、インクジェット方式の塗布機構を用いて、下部電極11上に誘電体物質を塗布する工程と、塗布された誘電体物質を加熱することにより、下部電極11上に誘電体膜12を形成する工程と、誘電体膜12上に上部電極を形成する工程とを具備する。上部電極を形成する工程は、下地膜8上及び誘電体膜12上に層間絶縁膜を形成する工程と、層間絶縁膜に、誘電体膜上に位置する開口部を形成する工程と、開口部の中及び層間絶縁膜上に導電体を堆積する工程と、層間絶縁膜上から導電体を除去することにより上部電極を形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

メモリ・アレイ、メモリ・アレイを形成する方法、及びビット線に対するコンタクトを形成する方法

本発明は、メモリ・アレイと、メモリ・アレイを形成するために利用することができる方法を含む。ビット線コンタクト位置まで開口を残しながらストレージ・ノード・コンタクト位置を覆うパターン化されたエッチング停止層が、メモリ・アレイの製造期間に使用される。エッチング停止層上及びビット線コンタクト位置上に絶縁材料を形成し、絶縁材料を通ってトレンチが形成される。トレンチ内に導電材料を設け、ビット線コンタクト位置と電気的に接触し且つエッチング停止層によってストレージ・ノード・コンタクト位置から電気的に分離されたビット線相互接続線を形成する。後続の処理において、エッチング停止層を通って、ストレージ・ノード・コンタクト位置まで開口を形成する。次いで、開口内に、ストレージ・ノード・コンタクト位置と電気的に接触するようにメモリ記憶装置を形成する。  (もっと読む)

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【構成】自己整列リセス・ゲート構造及び形成方法が開示されている。最初に,絶縁用のフィールド酸化物領域を半導体基板内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。 (もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

261 - 278 / 278

[ Back to top ]