Fターム[5F083AD10]の内容

Fターム[5F083AD10]に分類される特許

61 - 80 / 278

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の歩留まりを向上させること。

【解決手段】シリコン基板20に溝20aを形成する工程と、溝20aに充填材30を充填する工程と、溝20aに充填材30が充填された状態で、シリコン基板20に対してウエット処理を行う工程と、ウエット処理の後、充填材30を除去する工程と、充填材30を除去した後、溝20a内に、キャパシタ誘電体膜45aを介してキャパシタの対向電極50pを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】バイアス切替の前後でドレイン電流の大きさが変化しない縦型トランジスタを実現する。

【解決手段】半導体装置1は、第1の下部拡散層6A、第1の上部拡散層7A、及び第1のゲート電極9Aを有する第1の縦型トランジスタ4Aと、第2の下部拡散層6B、第2の上部拡散層7B、及び第2のゲート電極9Bを有する第2の縦型トランジスタ4Bと、第1及び第2のゲート電極9A,9Bに接続されるゲート配線と、第1の下部拡散層6A及び第2の上部拡散層7Bに接続される第1の配線W1と、第1の上部拡散層7A及び第2の下部拡散層6Bに接続される第2の配線W2とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

半導体装置の製造方法

【課題】非対称構造のソースおよびドレイン領域を有するMOSトランジスタを容易に形成する。これにより、高性能の半導体装置を容易に製造する。

【解決手段】第1のマスク層の互いに対向する両側面上に、2つの第2のマスク層を形成する。導電層上の、第1及び第2のマスク層が形成されていない部分の上に、第3のマスク層を形成する。第2及び第3のマスク層をマスクに用いて、導電層に対して異方性エッチングを行った後、不純物を注入することによって、1つの第1不純物拡散層を形成する。第2のマスク層をマスクに用いて異方性エッチングを行い第2のマスク層の下に、2つのゲート電極を形成する。第1不純物拡散層と共にゲート電極を挟む半導体基板の2つの領域に不純物を注入することによって、2つの第2不純物拡散層を形成する。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチ内に埋め込まれたシリコン層と複数のトレンチ間の半導体基板上に形成されたシリコン層とを同じイオン注入を行ない導電層とすること。

【解決手段】半導体基板10に複数のトレンチ30と、前記複数のトレンチ間の前記半導体基板上に第1キャパシタ絶縁膜22を介し第1シリコン層24と、を形成する工程と、前記複数のトレンチ内に埋め込み絶縁膜36を埋め込む工程と、前記埋め込み絶縁膜を前記複数のトレンチの側面に第2キャパシタ絶縁膜33が残存するように除去し、前記埋め込み酸化膜内に凹部を形成する工程と、前記凹部内の前記第2キャパシタ絶縁膜上と前記複数のトレンチ間の前記第1シリコン層上とに第2シリコン層40を直接形成する工程と、前記凹部内および前記第1キャパシタ絶縁膜上に形成された前記第2シリコン層内に不純物を同時にイオン注入する工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】データの保持時間を長くすることができるキャパシタレスDRAMの半導体装置及びその製造方法を提供する。

【解決手段】基板層42、埋め込み絶縁層43、及び半導体層41が順次積層された基板11と、半導体層41の主面41aに形成され、Y方向に延在し、半導体層41よりなるピラー状電荷保持部26と、ピラー状電荷保持部26と埋め込み絶縁層43との間に位置する半導体層41よりなり、ピラー状電荷保持部26と一体に形成され、X方向の幅がピラー状電荷保持部26の幅よりも広い第1の板状チャネル部25と、X方向から第1の板状チャネル部25を挟む第1及び第2の不純物拡散領域32,33と、少なくともピラー状電荷保持部26及び第1の板状チャネル部25の上面に設けられた電極用絶縁膜34と、電極用絶縁膜34を覆うように設けられ、ピラー状電荷保持部26に電圧を加える電荷保持用電極35と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン抵抗とメモリ回路とを混載した半導体装置において、メモリの情報の保持時間を長くして、かつ書込・読出時間を短くする。

【解決手段】容量素子400はメモリセルを構成しており、第1トランジスタ200は、ソース及びドレインとなる第1拡散層226が容量素子400に接続している。シリコン抵抗素子300はシリコン層からなる。第1拡散層226はシリサイド層を有していない。また第1ゲート電極230は、金属層232及びシリコン層234を積層した積層構造を有している。そして第1ゲート電極230は、素子分離膜50上に位置する領域の少なくとも一部にシリサイド層235を有しており、かつ第1拡散層226に挟まれた領域にはシリサイド層を有していない。そしてコンタクト513は、シリサイド層235を介して第1ゲート電極230に接続している。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

キャパシタを有する半導体装置およびその製造方法

【課題】信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】MOSトランジスタ20のソース/ドレイン領域12の一方に電気的に接続されたストレージノード1は、シリコン窒化膜24、BPTEOS膜4およびTEOS膜5に設けられた開口部6の側壁および底壁に沿って形成されており、かつ互いに間隔をあけて配置された複数の結晶粒を表面に有している。キャパシタ誘電体層2はストレージノード1上を覆い、かつストレージノード1の表面の結晶粒の間隔の1/2未満の膜厚Cを有している。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位変換回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法および半導体装置の作製方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に、書き込みトランジスタのソースを書き込みビット線に、読み出しトランジスタのソースとドレインとを、それぞれ、読み出しビット線及びバイアス線に接続する。さらに、キャパシタの他方の電極を読み出しワード線に接続する。配線数を減らすために、読み出しビット線を書き込みビット線で代用する。そして、読み出しビット線を、基板上に形成された溝状の開口部に埋め込むように形成する。

(もっと読む)

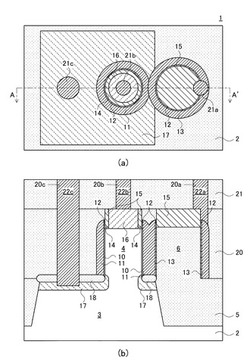

埋立ビットラインを有する半導体装置及び半導体装置の製造方法

【課題】埋立ビットラインを有する半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】埋立ビットラインを備えて低抵抗を有する垂直ピラートランジスタを含む半導体装置及びその製造方法が開示される。垂直ピラートランジスタは、基板上に形成され、下部と上部を有する本体、本体の上部に配置されるソース/ドレインノード、そして、本体の下部に配置されるドレイン/ソースノードを含む。半導体装置は、少なくとも本体の下部の上部表面に形成され、金属シリサイドを含む前記埋立ビットライン及び前記本体の上部を部分的に包むワードラインを備える。

(もっと読む)

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

61 - 80 / 278

[ Back to top ]