Fターム[5F083AD10]の内容

Fターム[5F083AD10]に分類される特許

41 - 60 / 278

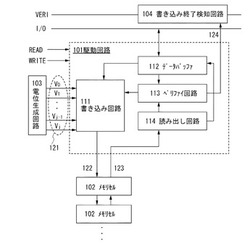

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】集積度が高く、データ保持時間の長い半導体記憶装置。

【解決手段】基板上の半導体膜と、半導体膜を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を介して半導体膜上に設けられた第1のゲート電極と、第1のゲート絶縁膜上にあり、半導体膜と重畳しない、第1のゲート電極と同一層かつ同一材料である第1の導電膜と、第1のゲート絶縁膜上にあり、第1のゲート電極および第1の導電膜の上面を露出し、第1のゲート電極および第1の導電膜の間に溝部を有する絶縁膜と、該絶縁膜上にあり、第1のゲート電極、第1の導電膜および溝部と接する酸化物半導体膜と、酸化物半導体膜を覆う第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜および溝部上に設けられた第2のゲート電極と、第2のゲート絶縁膜および酸化物半導体膜を介して第1のゲート電極上に設けられた、第2のゲート電極と同一層かつ同一材料である第2の導電膜と、を有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

キャパシタ、半導体装置及びそれらの製造方法

【課題】高い比誘電率を有する容量絶縁膜を使用して、静電容量を大きくし、しかもリーク電流を低減する。

【解決手段】容量絶縁膜として、c軸配向した結晶酸化ニオブを用い、特に成膜時の酸素含有量を、例えば、スパッタガスにおける酸素ガス比を調整することで制御して、a軸配向ピークを示さず、c軸配向ピークが優先した膜を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体素子および作製方法

【課題】ソフトエラー率を有意に低下させる半導体素子およびその作製方法に関する。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】シリンダ型下部電極の剥がれ落ちを防止する、半導体装置の製造方法を提供する。

【解決手段】複数の第1の開口を有するコア絶縁膜を半導体基板上に形成し、複数の第1の開口の側面を導電膜で覆う、シリンダ状の複数の下部電極を形成し、少なくとも複数の下部電極間のコア絶縁膜の上面を覆うサポート膜を形成し、サポート膜を用いて少なくとも複数の下部電極が形成される領域の外側を除去したマスク膜を形成し、マスク膜を形成した後、複数の下部電極間の一部にコア絶縁膜が残るように、コア絶縁膜に対して等方性エッチングを行うものである。

(もっと読む)

固体撮像素子

【課題】記憶部で発生するリーク電流を抑制した固体撮像素子を提供する。

【解決手段】複数の画素回路1aと、列信号線21と、複数の単位記憶回路2aとを備え、複数の単位記憶回路2aのそれぞれは、書き込みトランジスタ31と、記憶容量32と、n型の第1拡散領域143と、第1拡散領域143から所定距離離して形成され、書き込みトランジスタ31のソース又はドレイン領域に隣接する絶縁分離領域141と、絶縁分離領域141の周囲に、第1拡散領域143から所定距離離して形成された、p型の第2拡散領域142とを有し、少なくとも第2拡散領域142の表面には、金属シリサイド層が形成されていないことを特徴とする。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ時間のマージンを十分に確保しつつ、微細化が可能な半導体記憶装置を提供することを目的とする。

【解決手段】メモリセルを、読み出しトランジスタ、書き込みトランジスタ、キャパシタにより構成する。かかる構成において、キャパシタは読み出しトランジスタのゲートにかかる電位を制御する。書き込みトランジスタは、データの書き込みおよび消去を制御するとともに、キャパシタに蓄積された電荷が、該書き込みトランジスタのリーク電流で消失しないように、オフ時の電流が小さいトランジスタで構成する。書き込みトランジスタを構成する半導体層は、読み出しトランジスタのゲート電極とソース領域の間を架橋するように設ける。キャパシタは、読み出しトランジスタのゲート電極と重畳するように設ける。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】データの保持期間を長くする半導体装置又は半導体記憶装置を提供する。

【解決手段】一対の不純物領域を有する第1の半導体層152aと、第1の半導体層と同じ材料であり、第1の半導体層と離間する第2の半導体層152bと、第1、第2の半導体層の上に設けられた第1の絶縁層153と、第1の絶縁層153を介して第1の半導体層に重畳する第1の導電層154と、第1の絶縁層153を介して第1の導電層に重畳し、第1の半導体層と異なる材料である第3の半導体層156と、第1の導電層及び第3の半導体層に電気的に接続される第2の導電層157bと、第3の半導体層156に電気的に接続され、第2の導電層と同じ材料である第3の導電層157aと、第3の半導体層、第2の導電層、及び第3の導電層の上に設けられた第2の絶縁層158と、第2の絶縁層を介して第3の半導体層に重畳する第4の導電層159と、を含む。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

41 - 60 / 278

[ Back to top ]