Fターム[5F083AD10]の内容

Fターム[5F083AD10]に分類される特許

121 - 140 / 278

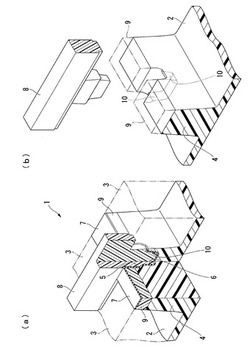

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が制御されて、且つ特性のばらつきが抑制された半導体装置を提供する。

【解決手段】基板2と、STI素子分離領域3と、活性領域4と、活性領域4に形成された第1ゲートトレンチ5と、第1ゲートトレンチ5の底部に設けられた第2ゲートトレンチ6と、第1及び第2ゲートトレンチ5,6にゲート絶縁膜7を介して埋め込み形成されたゲート電極8と、第1ゲートトレンチ5の幅方向両側の活性領域4にイオンを注入することによって形成されたソース/ドレイン領域9とを備え、第2ゲートトレンチ6と第2ゲートトレンチ6の長手方向に位置するSTI素子分離領域3との間に、チャネルを構成するシリコン薄膜部10が設けられていることを特徴とする半導体装置1。

(もっと読む)

半導体装置とその製造方法

【課題】基板からの高さが異なる導電層に、コンタクト窓を形成するDRAM等の半導体装置を提供する。

【解決手段】半導体基板16上に、第1導電パターン19、20と第1絶縁膜26、エッチング特性の異なる第2絶縁膜30、第3絶縁膜52、蓄積電極39、キャパシタ絶縁膜、対向電極40、エッチング特性の異なる第4絶縁膜41を形成し、第1導電パターン19,20上方に第1開口、対向電極40上方に第2開口を有するマスクを形成し、第1絶縁膜26をストッパとして、第1開口下方の第4絶縁膜41、第2絶縁膜30をエッチングし、第3絶縁膜52をストッパとして、第2開口下方の第4絶縁膜41、対向電極40をエッチングし、第1開口下方の第1絶縁膜26をエッチングして第1コンタクトホール44を形成し、第2絶縁膜30をストッパとして、第2開口下方の第3絶縁膜52をエッチングして第2コンタクトホール42を形成し、導電材を埋め込む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】簡便な方法により、マスク側壁への反応生成物の堆積を防止することができる半導体装置を製造する方法を提供する。

【解決手段】下部電極21、強誘電体、常誘電体、反強誘電体等による誘電体層22、及び上部電極23を含むキャパシタを複数備える半導体装置の製造方法は、上部電極層をパターニングして、複数の上部電極23、23’、23”を形成する工程と、複数の上部電極23、23”を被覆し、かつ最端に配置された上部電極23’の少なくとも一方側の端部を露出する第1マスクパターンを形成する工程と、第1マスクパターンを用いて、誘電体層22をパターニングする工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソースドレイン領域表面にシリサイド層が形成された構成のDRAM領域とロジック領域とが混載された半導体装置において、DRAMの保持特性を良好にする。

【解決手段】半導体装置100は、DRAM領域200に形成され、不純物としてヒ素とリンとを含む第1のソースドレイン領域126を含む第1のトランジスタ120と、ロジック領域210に形成され、不純物として少なくともヒ素を含む第2のソースドレイン領域146を含む第2のトランジスタ140とを含む。第1のソースドレイン領域126および第2のソースドレイン領域146の表面には、それぞれシリサイド層172が形成されている。第1のソースドレイン領域126において、リンによりジャンクション深さが規定され、当該ジャンクション深さが第2のソースドレイン領域146のジャンクション深さよりも深い。

(もっと読む)

半導体装置及びその製造方法

【課題】電極と対向する半導体基板との間で容量を形成し、半導体基板に形成された溝内に電極が形成され、リーク電流の抑制が図られたキャパシタを含む半導体装置を提供する。

【解決手段】半導体装置は、溝101が形成された半導体基板1と、溝101内に形成されたキャパシタ電極8Cと、溝101の底上に形成され、半導体基板1とキャパシタ電極8Cとの間に介在する第1の絶縁膜5と、溝101の側壁上に形成され、半導体基板1とキャパシタ電極8Cとの間に介在する第2の絶縁膜6Caと、溝101の底で、キャパシタ電極8Cと第1の絶縁膜5との間に介在する第1の金属酸化物膜7Caとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化した場合であっても電気的特性の良好なメモリセルを得ることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上及びトレンチ12cの側壁に形成されたキャパシタ誘電体膜30aと、キャパシタ誘電体膜上に形成されたキャパシタ電極36aとを有するキャパシタ40と、キャパシタ40に接続されたメモリセルトランジスタ54と、メモリセルトランジスタとキャパシタとが形成されたメモリセル領域4における半導体基板に形成された第2導電型の第1のチャネルドープ層26aと、メモリセル領域における半導体基板内に形成され、第1のチャネルドープ層よりも浅い第2導電型の第2のチャネルドープ層27とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化した場合であっても電気的特性の良好なキャパシタを得ることができる半導体装置及びその製造方法を提供する。

【解決手段】トレンチ12cが形成された半導体基板10と、半導体基板上及びトレンチの側壁に形成されたキャパシタ誘電体膜30aと、キャパシタ誘電体膜上に形成されたキャパシタ電極38とを有するキャパシタ40とを有し、キャパシタ電極は、半導体基板上及びトレンチ内に形成された第1の層32aと、第1の層が形成されたトレンチ内に埋め込まれた第2の層34と、第1の層上及び第2の層上に形成された第3の層36aとを有している。

(もっと読む)

キャパシタレスメモリ素子

本発明は、キャパシタレスメモリ素子に関し、半導体基板と、前記半導体基板上に位置する絶縁層と、前記絶縁層上の一部領域に形成されたストレージ領域と、前記ストレージ領域上に位置し、前記ストレージ領域とバランスバンドエネルギー差を有するチャネル領域と、前記チャネル領域上に順次に形成されたゲート絶縁膜及びゲート電極と、前記チャネル領域に接続され、前記ゲート電極の両側領域に位置するソース及びドレイン電極とを含むキャパシタレスメモリ素子を提供する。このように、チャネル領域部の下側にチャネル領域部とバランスバンドエネルギーが異なるストレージ領域部を配設し、ストレージ領域部にトラップされた電荷が容易に抜け出ないようにして、電荷の保有時間を増加させて、情報貯蔵能力を向上させることができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】半導体基板1と、半導体基板1上の絶縁層19と、絶縁層19内の複数のコンタクトプラグ16,66と、絶縁層30と、絶縁層30内に設けられた、キャパシタ82、複数のコンタクトプラグ25,75、バリアメタル層27,87及び銅配線29,88とを備えている。半導体基板1の上面内のソース・ドレイン領域9は銅配線29に電気的に接続されている。また、半導体基板1の上面内のソース・ドレイン領域59の一方は銅配線88に電気的に接続されている。そして、ソース・ドレイン領域59の他方はキャパシタ82に電気的に接続されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の製造安定性を向上させる。

【解決手段】半導体装置100においては、シリコン基板101にメモリ領域とロジック領域が混載されている。メモリ領域においてシリコン基板101に溝部111が設けられ、メモリ領域にメモリセルトランジスタ120が設けられるとともにロジック領域にロジックトランジスタ130が設けられる。メモリセルトランジスタ120は金属材料により構成された第一ゲート電極115を含む。第一ゲート電極115は溝部111に埋設されるとともに溝部111の外部に突出して設けられる。ロジックトランジスタ130は第一ゲート電極115と同一材料により構成された第二ゲート電極127を含む。

(もっと読む)

半導体装置の製造方法

【課題】embedded DRAMに対して、ロジック回路に用いるCMOSトランジスタのゲート電極上およびソース/ドレイン領域をコバルトシリサイド化することができる半導体装置の製造方法を提供する。

【解決手段】少なくともメモリセル領域を除く領域のソース/ドレイン領域7a、7b上に形成されたUSG9と、ゲート電極4上に形成されたUSG9及びシリコン酸化膜5を除去する。USG9は、耐コバルトシリサイド化反応膜として作用する。コバルトをスパッタ法によりウエハ全面に成膜してランプアニール等の熱処理を行うことにより、USGに覆われていない領域のロジック回路領域のトランジスタのソース/ドレイン領域7a、7bとゲート電極4上にコバルトシリサイド膜11を形成することにより、ロジック回路の高性能化及び高集積化が可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化を進める際に製造容易な構造を提供する。

【解決手段】基板の平面方向において連続して配置されるMOSトランジスタを有する半導体装置において、ゲート電極および該ゲート電極間を接続する配線部(矢印13で図示する箇所)が、拡散層14が形成される基板10の表面より下層に埋め込まれている。基板10の表面には、ソース・ドレイン領域として機能する拡散層14どうしを分離するSTI構造の第一の素子分離領域12が形成されている。そして該第一の素子分離領域12が存在する層より下の層に、隣接するMOSトランジスタのチャネル領域どうしを分離するSTI構造の第二の素子分離領域11が形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】

ロジックプロセスとの整合性の高い、メモリセルを含む半導体装置及びその製造方法を提供する。

【解決手段】

半導体装置は、半導体基板の主面側に画定され、各々が、長尺状の平面視形状を有し、トランジスタ部とキャパシタ部を含む、複数の活性領域と、活性領域を取り囲んで半導体基板に形成された溝部と、該溝部を埋め込んだ絶縁材とを含むSTIと、各活性領域のキャパシタ部の幅方向両側のSTIの絶縁材を底部を残して掘り下げ、活性領域側壁を露出するキャパシタ用凹部と、各活性領域のトランジスタ部上面上に形成され、第1絶縁膜とその上の第1導電層とを含む絶縁ゲート電極構造と、各活性領域のキャパシタ部の上面上と露出された側面上に形成され、第1絶縁膜と同一材料で形成された第2絶縁膜と、第2絶縁膜を覆い、複数の活性領域に亘って、第1導電層と同一材料で形成された第2導電層とを含むMISキャパシタ構造と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲートラストプロセスで形成されたゲート構造において、ソース・ドレイン領域に接続するコンタクトとゲート電極とのショートを防ぐ。

【解決手段】半導体装置100は、ゲートラストプロセスで形成された第1のゲート210を含む。第1のゲート210は、絶縁膜中に形成された第1の凹部内の底面に形成されたゲート絶縁膜、当該第1の凹部内のゲート絶縁膜上に形成されたゲート電極、および当該第1の凹部内のゲート電極上に形成された保護絶縁膜140を含む。また、半導体装置100は、第1のゲート210の両側方のN型不純物拡散領域116aに接続され、第1の凹部よりも径が大きい第2の凹部内に埋め込まれたコンタクト134を含む。

(もっと読む)

半導体記憶装置

【課題】高い性能の単一トランジスタDRAMを有する半導体記憶装置を提供する。

【解決手段】支持基板11の主面に絶縁膜12を介して形成された半導体膜13に、ゲート絶縁膜14を介して形成されたゲート電極15と、ゲート電極15をゲート長方向に挟むように形成されたドレイン領域16およびソース領域17とを有し、ドレイン領域16がゲート電極15と隣接する長さWdが、ソース領域17がゲート電極15と隣接する長さWsより大きいセルトランジスタ18を具備する。セルトランジスタ18がマトリックス状に配置され、第1の方向Xには、隣接するセルトランジスタ18同士でドレイン領域16およびソース領域17を共用するように配列され、第2の方向Yには、素子分離領域27を挟んで隣り合うセルトランジスタ18がドレイン領域16とソース領域17とが互いに対向するように配列されている。

(もっと読む)

半導体装置の製造方法

【課題】溝の形状を維持しながらバリを除去するとともに、溝内壁におけるシリコン表面のダメージを除去することが可能な半導体装置の製造方法、及び該製造方法によって製造された半導体装置を提供する。

【解決手段】基板1に埋設領域Mを形成して素子分離を行なう工程と、基板1に溝7a,7b,7cのパターンを形成する工程と、溝7a,7b,7c内壁に保護膜8を形成する工程と、異方性の強い条件でエッチバックすることにより、溝7a,7b,7cのゲート垂直方向側壁7dの一部に保護膜8を残しながら、溝7a,7b,7cのゲート平行方向内壁7eの保護膜8を除去する工程と、保護膜8の除去によってシリコンが露出した領域に水素ベーク処理を行って、溝7a,7b,7cのパターン形成の際に副生されたバリ1a,1aを除去する工程と、を少なくとも有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法並びにデータ処理システム

【課題】トレンチゲート型トランジスタのサブスレショルド特性の向上を図りつつ、ゲートトレンチの幅が縮小された高性能な半導体装置を提供する。

【解決手段】ゲートトレンチ16の底部16bは、STI14から相対的に遠い第1の底部16b1と、STI14から相対的に近い第2の底部16b2を有している。そして、活性領域10aのうち、ゲートトレンチの第2の底部16b2を構成する部分は、側壁チャネル領域10dを構成し、ゲート電極18とSTI14との間に挟まれた薄膜SOI構造を有している。一方、ゲートトレンチの第1の底部16b1を構成する部分は、副チャネル領域10eとして機能する。第2の底部16b2の曲率半径は第1の底部16b1の曲率半径よりも大きい。ゲートトレンチ16の幅方向の略中央部分においては、トレンチの底面が略平坦であるのに対し、幅方向の端部においては、トレンチの底面がほぼ全体的に湾曲している。

(もっと読む)

半導体装置の製造方法

【課題】高精度で歩留まりよくフィンを形成できる半導体装置の製造方法を提供する。

【解決手段】素子分離領域3の高さよりも活性領域4の高さを低くすることにより、活性領域4を凹部36とする工程と、凹部36の側壁にサイドウォール37を形成する工程と、凹部36の底面に半導体基板2を露出させ、半導体基板2上にシリコン膜38を選択的にエピタキシャル成長させる工程と、シリコン膜38を熱酸化して熱酸化膜39を形成する工程と、ゲート形成領域を除く領域にゲート反転レジストパターンを形成し、ゲート形成領域のサイドウォール37を除去した後、ゲート反転レジストパターンを除去する工程と、熱酸化膜39をマスクとして半導体基板2をエッチングしてトレンチを形成する工程とを備える半導体装置の製造方法とする。

(もっと読む)

半導体記憶装置

【課題】良好な動作を維持しながら高集積化された半導体記憶装置を提供する。

【解決手段】第1のワード線20、第2のワード線33、ビット線及びキャパシタとトランジスタを含むメモリセルを有する半導体記憶装置であって、トランジスタは、半導体基板主面から突起した柱状半導体層14と、柱状半導体層14の側面に形成されたゲート絶縁膜19と、柱状半導体層14の側面を覆うように設けられたゲート電極20と、柱状半導体層14の上部に形成された上部拡散層と、柱状半導体層14の側面下方の半導体基板部分に形成された下部拡散層18とを有し、このトランジスタとキャパシタを含むメモリセルが配置された第1のセルアレイ部と、第1のセルアレイ部と同じレイアウトでダミーセルが配置された第2のセルアレイ部を有し、第2のセルアレイ部において、第1のワード線20と第2のワード線33が導電プラグ30を介して接続されている半導体記憶装置。

(もっと読む)

121 - 140 / 278

[ Back to top ]