Fターム[5F083CR01]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | マスクROM (119)

Fターム[5F083CR01]の下位に属するFターム

イオン注入の有無によるマスクROM (18)

配線接続の有無によるマスクROM (74)

Fターム[5F083CR01]に分類される特許

1 - 20 / 27

半導体装置

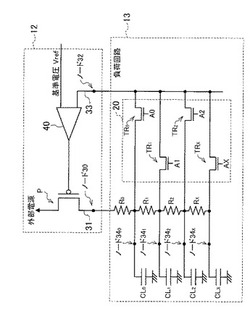

【課題】適切に電源電圧を負荷回路に供給することができる、半導体装置を提供する。

【解決手段】電圧トランスファ20及びセンスノード配線33が設けられており、電圧トランスファ20は、各Sub−Arrayに応じて設けられたNMOSトランジスタTRにより、ノード32とノード30との間が接続される。電圧トランスファ20のトランジスタTRは、ソース及びドレインの一方が電源線31の各Sub−Arrayに応じた位置に接続されており、ソース及びドレインの他方がセンスノード配線33に接続されている。また、トランジスタTRのゲートには、対応するSub−Arrayのデコード信号A0〜AXが入力される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】比較的高い抵抗率を持つ導電体を電極に用いた場合でも、高信頼な抵抗変化素子を実現する。

【解決手段】不揮発性半導体記憶装置は、第1配線54と、第2配線55と、一端を前記第1配線54に、他端を前記第2配線55にそれぞれ電気的に接続されたメモリセル40とを具備する。メモリセル40は、抵抗値の変化で情報を記憶する抵抗変化層41と、抵抗変化層41の両端にそれぞれ接続され、貴金属を含まない第1電極51及び第2電極52とを備える。第1電極51は、外側電極43と、外側電極43と抵抗変化層41との間に設けられた界面電極42とを含む。界面電極42の膜厚は、外側電極43の膜厚よりも薄い。界面電極42の抵抗率は、外側電極43の抵抗率よりも高い。第1電極51の抵抗値Rsは、抵抗変化層52の低抵抗状態の抵抗値Ronよりも低い。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルを微細化しても、抵抗変化動作に十分な電流を流すことが可能なダイオードを備える抵抗変化型の不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、X方向に延在する第1配線13と、Y方向に延在する第2配線20と、第1配線13と第2配線20との交点に設けられたメモリセル10とを具備する。メモリセル10は、第1配線13上に設けられ一端を第1配線13に接続されたダイオード15と、ダイオード15上方に設けられ一端をダイオード15に直列接続され、他端を第2配線20に接続され、抵抗値の変化で情報を記憶する抵抗変化部19とを備えている。ダイオード15は、第1導電型の第1半導体層13と、第2導電型で、第1半導体層13の内部に伸びている第2半導体層14とを含んでいる。

(もっと読む)

半導体記憶装置及びその回路の電位測定方法

【課題】大規模な半導体記憶装置における不良トランジスタの検出と、不良トランジスタの特性の測定とを高速で行うことができる、半導体記憶装置を提供する。

【解決手段】メモリ素子が縦横にマトリックス状に配列されたメモリセルアレイと、接地ノードあるいは電源ノードに接続する枝配線を有する半導体記憶装置において、電源ノードあるいは接地ノードに接続する少なくとも1つの枝配線の複数箇所に電圧測定点を接続したモニター用スイッチを有し、クロック信号に同期して前記モニター用スイッチのゲートを順に開くスイッチ選択信号発生回路を有し、前記スイッチ選択信号発生回路で選択されてゲートが開かれたモニター用スイッチを介して前記電圧測定点の電位を測定する。

(もっと読む)

プロセス評価用半導体集積回路

【課題】 微妙なプロセスコントロールのための判断材料となる情報を短時間のうちに採取することができるプロセス評価用半導体集積回路を提供する。

【解決手段】 プロセス評価用半導体集積回路としてのSRAMは、メモリセルに電源電圧を供給する給電系統と、メモリセル以外の回路に電源電圧を供給する給電系統とが分離されており、メモリセルに供給する電源電圧を他の回路に対する電源電圧と独立に制御可能な構成となっている。メモリセルに対する電源電圧を段階的に下げつつ、各メモリセルに対するアクセスを試み、動作不良を検出することにより、メモリセル間のトランジスタの電気的特性の微妙な変化を判定することができる。

(もっと読む)

集積回路装置及びその端子配置方法

【課題】複数の機種に展開される集積回路装置の低コスト化を実現する集積回路装置及びその端子配置方法を提供する。

【解決手段】マスクROMを内蔵する集積回路装置は、EPROMを内蔵する集積回路装置の第1の辺に沿って配置される外部端子群と共通の第1の共通外部端子群と、前記EPROMにアクセスするEPROM版処理回路の機能の少なくとも一部を有し、その処理内容に対応した信号が前記第1の共通外部端子群を介して入力又は出力される処理回路と、前記処理回路によってアクセスされる前記マスクROMとを含み、前記第1の共通外部端子群が、当該集積回路装置の周囲の4辺のうち前記第1の辺に対応する第2の辺に沿って配置され、前記外部端子群を構成する各外部端子の並び順序と、前記第1の共通外部端子群を構成する各共通外部端子の並び順序とが同じである。

(もっと読む)

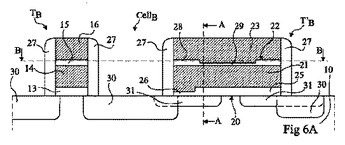

EEPROM構造を有する読出し専用メモリ

【解決手段】本発明は、少なくとも第1及び第2のメモリセル(CellB) を備えた不揮発性メモリ(M) に関しており、第1及び第2のメモリセルは、デュアルゲート(21,23) とデュアルゲート(21,23) 間に設けられた絶縁層(22)とを有する蓄積MOS トランジスタ(TB') を夫々備えている。第2のメモリセル(CellB) の蓄積トランジスタ(TB') の絶縁層(22)は、第1のメモリセルの蓄積トランジスタの絶縁層より絶縁性が低い少なくとも1つの部分(29)を有している。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法並びに半導体製造装置

【課題】プログラムされた情報のセキリュティが高く、半導体チップ毎に異なる情報をプログラムすることを簡単に可能とすること。

【解決手段】本発明は、半導体ウエハ内に配列された複数の半導体チップとなるべき領域12内にそれぞれ設けられたOTP−ROMセル配列21に対応するプログラムドット配列を有するプログラムヘッド80を、複数の半導体チップとなるべき領域12のうち1つの領域内のOTP−ROMセル配列21に合わせる工程と、プログラムヘッド80を用いOTP−ROMセル配列21を、複数の半導体チップとなるべき領域12ごとに異なるパターンでプログラムする工程と、を有することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置及びその作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体領域を用いて形成された半導体素子を有する素子基板上に、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着することにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体及び素子基板が固着された半導体装置を作製する。

(もっと読む)

半導体装置

【課題】CPU搭載無線タグのメモリ内のデータの書き換えを可能にした上で、CPUシステムを高速化し、無線タグの通信性能の向上を行う。

【解決手段】CPUが搭載されている無線タグにRFバッテリー付きのSRAMを搭載することで、CPUシステムの高速化による通信性能を向上させる。また、CPU搭載無線タグのメモリ内のデータの書き換えを可能にした。RFバッテリーは、アンテナ回路と、電源部と、蓄電装置と、を有する。SRAMとRFバッテリーとを組み合わせることで、SRAMに不揮発性メモリとしての機能を持たせる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】基板表面と基板上に形成された配線とで形成される段差部分にシリコン膜を形成した場合においても、メモリ素子の書き込み特性を低下させない半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】絶縁表面を有する基板10上に形成された第1の電極11と、第1の電極11の側壁部に形成されたサイドウォール絶縁層12と、第1の電極11上及びサイドウォール絶縁層12を覆って形成されたシリコン膜13と、シリコン膜13上に形成された第2の電極14と、を有し、第1の電極11又は第2の電極14は、シリコン膜13と合金化する材料で形成されているメモリ素子を複数有している。

(もっと読む)

半導体装置

【課題】メモリーにおいて波長以下の線幅を有する微細なワード線やデータ線をパターニングする際、メモリーアレーとサブワードドライバやセンスアンプの境界部において、パターン端部で生ずる回折光が干渉するためワード線やデータ線端がショートしたり、断線を起こす問題を解決するパターン形成方法を提供する。

【解決手段】ワード線やデーター線をパターニングするためのマスクパターン(a)において、終端部の隣り合うワード線WL1、WL2、WL5、WL6の長さを変えて先端をずらし、さらにワード線端WL1、WL2、WL5,WL6を斜めに角を落とす。レジストパターン内の分離やパターン同士の接触を防止することができ、パターニングする配線の断線や、配線間のショートを防止することができる。

(もっと読む)

半導体装置とその作製方法

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。また信頼性の高い半導体装置を提供する。

【解決手段】チャネル形成領域と、ソース領域またはドレイン領域を有する島状半導体膜131〜134と、ゲート絶縁膜と、ゲート電極103〜106とを有する薄膜トランジスタ118〜121と、層間絶縁膜と、層間絶縁膜中に形成され、ソース領域またはドレイン領域の一方に達する複数のコンタクトホール142を含む第1のコンタクトホールと、ソース領域またはドレイン領域の他方に達する第2のコンタクトホール141とを有し、第2のコンタクトホール141の径は、第1のコンタクトホールに含まれる複数のコンタクトホール142のそれぞれの径より大きく、第1のコンタクトホール142の底面積の合計と、第2のコンタクトホール141の底面積は等しい半導体装置に関するものである。

(もっと読む)

半導体装置及び電子機器

【課題】メモリにおけるデータの読み出しに関し、低消費電力なメモリを搭載した半導体装置を提供することを課題とする。

【解決手段】ワード線と、ビット線と、ワード線及びビット線に電気的に接続されたメモリセルを有する半導体装置において、ビット線に接続され、ビット線の電位をメモリセルに保持されたデータを読み出すための電位にするプリチャージ回路を有し、プリチャージ回路はビット線毎に設けられており、ビット線毎にメモリセルに保持されたデータを読み出すための電位にする構成とする。

(もっと読む)

メモリ・セルにおける金属ラインのレイアウト

【課題】メモリ・セルの設計に関する種々の制約を同時に叶えるメモリ・セルの金属ラインのレイアウトを提供する。

【解決手段】メモリ・セルは、第1の方向に走るポリシリコン・ゲート2を有して提供される。金属ラインの一連の層は、第1の方向と実質的に直交する第2の方向に走るビット・ライン4の層を含み、その後に、第2の方向に走るデータ・ライン6を含み、そして、次に、第1の方向に走るワード・ライン8を含んで、提供される。データ・ライン6は、ビット・ライン4が、メモリ・セル内に記憶されたデータ値を感知するために用いられている間に保持されている値にプリチャージされる。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一シリコン基板上に、少なくとも、ソース・ゲート間あるいはドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設けるとともに、トンネル電流の大きさが異なる複数種類のMOSトランジスタのうち、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入された制御回路とを有し、制御回路に供給される制御信号により、主回路を構成するトンネル電流が大きいMOSトランジスタのソース・ゲート間あるいはドレイン・ゲート間に流れることの許容/不許容を制御するようにした。

(もっと読む)

半導体記憶装置、半導体装置、半導体記憶装置の製造方法および半導体装置の製造方法

【課題】メモリセルごとに書き込まれる電位のばらつきを抑えることが可能な半導体記憶装置、半導体装置、半導体記憶装置の製造方法および半導体装置の製造方法を提供する。

【解決手段】半導体記憶装置100は、半導体基板11と、半導体基板11上に形成されたゲート絶縁膜14と、ゲート絶縁膜14上に形成されたゲート電極15と、半導体基板11上部であってゲート電極15下を挟む一対の領域に形成された低濃度拡散領域16と、低濃度拡散領域16上に形成された電荷蓄積部18とを含むメモリセル1と、メモリセル1を覆うように半導体基板11上に形成され、所定波長のUVレーザ光を透過させる絶縁性の第1パッシベーション21と、第1パッシベーション21上に形成され、UVレーザ光を遮断し、電荷蓄積部18上に開口を有する第2パッシベーション23とを有する。

(もっと読む)

マスクROMを具備する半導体装置及びその製造方法

【課題】マスクROMを具備する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100と、半導体基板の複数の活性領域を画定する素子分離膜パターン110と、活性領域に形成されノーマリオントランジスタとノーマリオフトランジスタにより構成されたマスクROM領域MRRと、活性領域上に配置され素子分離膜パターン110上を交差して伸びるゲートライン170と、ゲートライン170と活性領域との間に形成されたゲート絶縁膜121,160を有し、ノーマリオフトランジスタはさらに前記ゲートラインと前記ゲート絶縁膜190との間において浮遊導電パターン131とゲート層間絶縁膜パターン141を順に積層する。

(もっと読む)

微小構造体及び微小電気機械式装置の作製方法

【課題】微小構造体の空間を形成するために設ける犠牲層に使用されるフォトマスクの枚数を低減し、製造コストを削減する。

【解決手段】同一のフォトマスクを用いてパターニングされたレジストマスクにより犠牲層を形成する。レジストマスクにより第1の犠牲層をエッチングして形成した後に、同一のフォトマスクを使用してパターンを形成されたレジストマスクを用いて第2の犠牲層をエッチングして形成する。レジストマスクは一方の犠牲層のエッチング前に外形寸法を拡大又は縮小する等して変形することで、大きさの異なる犠牲層を形成することができる。

(もっと読む)

半導体記憶装置

【課題】

デコーダ部の両側にそれぞれのワード線に対応したドライバを設けることは困難となってきていた。

【解決手段】

半導体記憶装置は、行デコーダ部と、前記行デコーダ部の一方に配置された第1のセルアレイと、前記行デコーダ部の他方に配置された第2のセルアレイと、前記行デコーダ部上に配置され、前記第1のセルアレイの所定の行アドレスに対応するワード線と前記第2のセルアレイの前記所定の行アドレスに対応するワード線を短絡する配線層とを有する。

(もっと読む)

1 - 20 / 27

[ Back to top ]