Fターム[5F083CR14]の内容

半導体メモリ (164,393) | ROM(EPROM、EEPROMを除く) (635) | PROM(Programmable ROM) (484) | 絶縁膜破壊型ROM (178)

Fターム[5F083CR14]に分類される特許

1 - 20 / 178

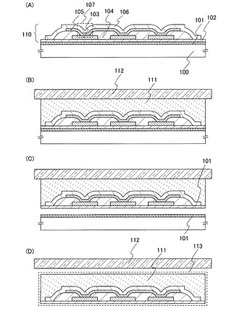

半導体装置

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導

体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体

装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体

を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製す

る方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に

有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金

層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物

を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成さ

れるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

高速OTP感知スキーム

【課題】不揮発性メモリアレイのための高速感知スキームを提供する。

【解決手段】メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

OTPメモリ

【課題】より秘匿性の高いOTPメモリを提供する。

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法

【課題】カップリングチャネルを使用したアンチヒューズメモリ及びその操作方法を提供する。

【解決手段】カップリングチャネルを使用したアンチヒューズメモリは、第1導電型の基板と、第2導電型のドープ領域と、カップリングゲートと、ゲート誘電層と、アンチヒューズゲートと、アンチヒューズ層と、を含む。基板中に隔離構造を有する。ドープ領域が基板中に設置され、且つドープ領域及び隔離構造の間にチャネル領域を定義する。カップリングゲートがドープ領域及び隔離構造の間の基板上に設置され、且つカップリングゲートとドープ領域と隣り合う。ゲート誘電層がカップリングゲート及び基板の間に設置される。アンチヒューズゲートがカップリングゲート及び隔離構造の間の基板上に設置され、アンチヒューズゲート及びカップリングゲートの間に間隔を有する。アンチヒューズ層がアンチヒューズゲート及び基板の間に設置される。

(もっと読む)

半導体装置

【課題】プロセス技術が比較的簡単、且つ、少ない素子数で多値情報を記憶することがでるメモリを提供する。

【解決手段】メモリ素子426において、第1の記憶素子における第1の電極417の形状の一部を、第2の記憶素子における第1の電極417の形状と異ならせることで、第1の電極417と第2の電極420の間の電気抵抗が変化する電圧値を異ならせて、1ビットを越える多値の情報の記憶を一つのメモリセルで行う。第1の電極417を部分的に加工することで単位面積当たりの記憶容量を増大することができる。

(もっと読む)

メモリストリングにダイオードを有する3次元アレイのメモリアーキテクチャ

【課題】信頼でき、非常に小型の3次元集積回路メモリ用の構造を低い製造コストで提供する。

【解決手段】3次元アレイは第1の端部と第2の端部を含む2つの端部を有し、第1の端部と第2の端部の一方はビット線BLに接続され、第1の端部と第2の端部の他方はソース線CSLに接続される不揮発性メモリセルのNANDストリングのスタック1412、1413、1414と、ビット線BL及びソース線SLの一方をメモリセルのストリング1412、1413、1414に接続させるダイオード1492を有する。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

デュアル機能を有する不揮発性半導体メモリセル

【課題】デュアル機能を有する不揮発性半導体メモリセルは、基板、第1ゲート、第2ゲート、第3ゲート、電荷蓄積層、第1拡散領域、第2拡散領域及び第3拡散領域を有する。

【解決手段】第2ゲート及び第3ゲートは、デュアル機能のワンタイムプログラミング機能に対応する第1電圧及びデュアル機能のマルチタイムプログラミング機能に対応する第2電圧を受けるために用いられる。第1拡散領域は、ワンタイムプログラミング機能に対応する第3電圧及びマルチタイムプログラミング機能に対応する第4電圧を受けるために用いられる。第2拡散領域は、マルチタイムプログラミング機能に対応する第5電圧を受けるために用いられる。

(もっと読む)

半導体装置

【課題】コイル状のアンテナ部の内部に、占有面積が大きい導電層が設けられていると、電源を安定して供給することが困難になっていた。

【解決手段】記憶回路部とコイル状のアンテナ部とを積層して配置することにより、記憶回路部が含む占有面積の大きい導電層に電流が流れてしまうことを防止することができ、省電力化を図ることができる。また、記憶回路部とコイル状のアンテナ部とを積層して配置することにより、スペースを有効に利用することができる。従って、半導体装置の小型化を実現することができる。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

不揮発性半導体記憶装置

【課題】レイアウト面積の増大を抑制しつつ、容量を拡張することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルに複数のアンチヒューズ素子F1、F2を設け、各アンチヒューズ素子F1、F2の電界効果トランジスタのゲートを互いに接続することで、アンチヒューズ素子F1、F2の一端をノードAに共通に接続し、メモリセルを多値化する。

(もっと読む)

積層した接続レベルを有する集積回路装置用マスク数の低減法

【課題】3D積層メモリ装置は、各接続レベル毎に別個のマスクが使用されるので必要なマスク数は多くなるが、パターンを工夫して必要マスク数を減らす。

【解決手段】3次元積層集積回路装置は配線領域に接続レベルの積層部を有する。接続レベルの積層部で2のN乗個のレベルまで含む配線接続領域を形成するためのN個のエッチングマスクの組だけが必要とされる。幾つかの例によれば、2のX−1乗(2X−1)個の接続レベルは、連続番号Xのエッチングマスクでエッチングされ、1つのマスクがX=1であり、他の1つのマスクがX=2であり、X=Nまで付与される。当該方法は接続レベルでの形成領域に整合した配線接続領域を形成する。

(もっと読む)

半導体装置およびその動作方法

【課題】省面積化を図ることが可能な半導体装置およびその動作方法を提供する。

【解決手段】各記憶素子21は、P型の半導体層211Pと、半導体層211P内で互いに分離するように配設されたN型の半導体層212N,213Nと、半導体層211P上の半導体層212N,213N間に対応する領域に設けられた下層側の誘電体膜216および上層側の導電体膜217と、半導体層212Nと電気的に接続された電極215Aと、半導体層213Nと電気的に接続された電極215Bと、導電体膜217と電気的に接続された電極215Cとを有する。駆動対象の記憶素子21に対して、電極215B,215C間に所定の閾値以上の電圧V1を印加して、誘電体膜216の少なくとも一部分を絶縁破壊させて導電体膜217,半導体層213N間に電流を流し、半導体層212N,213N間の領域にフィラメント210を形成することにより、情報の書き込み動作を行う。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体装置

【課題】アンチヒューズにおいて、電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにする。

【解決手段】アンチヒューズ12は、ゲート絶縁膜、ゲート電極114、及び第1拡散層116を有している。第2拡散層126は、素子分離膜102を介して第1拡散層116と離間しており、第1拡散層116と同一導電型を有している。ゲート配線124はゲート電極114と一体として形成されており、素子分離膜102上を延伸している。共通コンタクト220は、ゲート配線124と第2拡散層126を接続している。そしてゲート電極114は、第1拡散層116と同一導電型の不純物が導入された半導体、例えばポリシリコンにより形成されている。また第2拡散層126は、共通コンタクト220のみに接続している。

(もっと読む)

メモリセルアレイ、メモリ装置、及び無線チップ

【課題】従来の調査方法では、質問事項に対して回答しない客がいるという問題があった

。また客の主観や見栄等による影響があり、客のニーズを的確に判断することが困難であ

った。

【解決手段】客に無線通信が可能なチップ(無線チップ)の装着された物を持たせる。更

に、店舗の売場の入口、出口、及び売場の内部の複数のポイント各々にアンテナを配置す

る。客が入口、出口及び複数のポイントに近づくと、近づいたポイントに配置されたアン

テナから無線チップに位置情報と時刻情報とを書き込む。無線チップに書き込まれた情報

を読み取ることで客の売場内での移動経路等を判断する。この結果をもとに客のニーズを

判断する。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

1 - 20 / 178

[ Back to top ]