Fターム[5F083FR00]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733)

Fターム[5F083FR00]の下位に属するFターム

キャパシタを有するもの(破壊読出型) (1,245)

MFS型(非破壊読出型) (230)

ブロック構造 (61)

Fターム[5F083FR00]に分類される特許

161 - 180 / 197

ニオブ酸ビスマス系微粒子の製造方法

【課題】製造が容易で組成及び粒子径の均一性に優れ、特に高い結晶性を有するニオブ酸ビスマス系微粒子の製造方法の提供。

【解決手段】酸化物基準のモル%表示で、MO(M=Mg、Ca、Sr及びBaからなる群より選ばれる1種以上)を25〜60%、Bi2O3を3〜25%、Nb2O5を2〜25%及びB2O3を15〜60%含む溶融物を得る工程と、前記溶融物を急速冷却して非晶質物質とする工程と、前記非晶質物質からニオブ酸ビスマス系結晶を析出させる工程と、得られた析出物から前記ニオブ酸ビスマス系結晶を分離する工程と、をこの順に含むことを特徴とするニオブ酸ビスマス系微粒子の製造方法。

(もっと読む)

磁気抵抗効果素子を含む半導体装置及びその製造方法

【課題】 磁気抵抗効果素子の抵抗のばらつきを抑制することができる半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に、磁化方向が固定された強磁性材料からなるピンド層と、外部磁場によって磁化方向が変化するフリー層とで非磁性層を挟んだ磁気抵抗効果素子を形成する。(b)窒化されることによって、元の材料よりも水分を透過させにくい絶縁物になる絶縁材料からなる層間絶縁膜を、磁気抵抗効果素子を覆うように形成する。(c)層間絶縁膜の表層部を窒化する。

(もっと読む)

半導体メモリ

【課題】ワード線ドライバの新レイアウトによりチップサイズの縮小を図る。

【解決手段】本発明の例に関わる半導体メモリは、メモリセルアレイ11と、メモリセルアレイ11上に配置される複数のワード線WL11,・・・WL1Cと、複数のワード線WL11,・・・WL1Cの各々に1つずつ接続される複数の転送トランジスタ21とを備え、複数の転送トランジスタ21のうちの1つは、他の1つの転送トランジスタと向きが異なる。

(もっと読む)

ナノチューブトランジスタアクセスデバイスを備えたメモリ

メモリセルは、メモリ素子と、当該メモリ素子にアクセスするために当該メモリ素子に接触したナノチューブトランジスタとを有している。  (もっと読む)

(もっと読む)

分極信号検出デバイス

【課題】 従来の強誘電体メモリは不揮発性を利用する強誘電体薄膜がメモリセル毎に孤立している。したがって、不揮発性メモリとして集積度を高める際には強誘電体薄膜も小さな形状に裁断されることとなり、その結果、充分な特性や信頼性が得られず、微細化、高集積化には限界が生ずるという課題があった。

【解決手段】 強誘電体薄膜を複数個の電極で挟み、強誘電体薄膜の中で分極信号を転送する分極転送部と、ゲート部に強誘電体薄膜を有する電界効果型トランジスタを分極検出部とをメモリの構成要素として組み合わせ、かつ強誘電体薄膜を連続、一体化した構成をとることにより、強誘電体特性を確保し、微細化、高集積化に適した強誘電体メモリを得る。

(もっと読む)

分極転送デバイス、及びその転送制御方法

【課題】 従来の強誘電体メモリは不揮発性を利用する強誘電体薄膜がメモリセル毎に孤立している。したがって、不揮発性メモリとして集積度を高める際には強誘電体薄膜も小さな形状に裁断されることとなり、その結果、充分な特性や信頼性が得られず、微細化、高集積化には限界が生ずるという課題があった。

【解決手段】 強誘電体薄膜を複数個の電極で挟み、強誘電体薄膜を連続、一体化した構成をとり、強誘電体薄膜の中で分極信号を転送する分極転送デバイス構造を強誘電体メモリのメモリセル群として用いることにより、強誘電体特性を確保し、微細化、高集積化に適した強誘電体メモリが得られる。

(もっと読む)

分極メモリセルアレイ

【課題】 従来の強誘電体メモリは不揮発性を利用する強誘電体薄膜がメモリセル毎に孤立している。したがって、不揮発性メモリとして集積度を高める際には強誘電体薄膜も小さな形状に裁断されることとなり、その結果、充分な特性や信頼性が得られず、微細化、高集積化には限界が生ずるという課題があった。

【解決手段】 強誘電体薄膜を複数個の電極で挟み、強誘電体薄膜の中で分極信号を転送する分極転送デバイスをメモリセルアレイとして集積し、強誘電体薄膜を連続、一体化した構成をとることにより、強誘電体特性を確保し、微細化、高集積化に適した強誘電体メモリを得る。

(もっと読む)

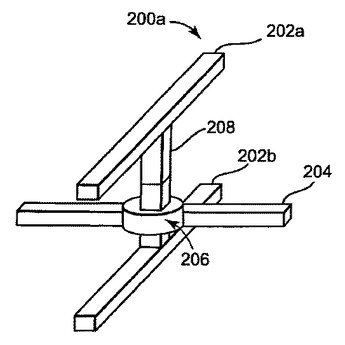

分極転送方向選択デバイス

【課題】 従来の強誘電体メモリは不揮発性を利用する強誘電体薄膜がメモリセル毎に孤立している。したがって、不揮発性メモリとして集積度を高める際には強誘電体薄膜も小さな形状に裁断されることとなり、その結果、充分な特性や信頼性が得られず、微細化、高集積化には限界が生ずるという課題があった。

【解決手段】 強誘電体薄膜を連続、一体化した構成をとり、かつ複数個の電極で挟み、強誘電体薄膜の中で分極信号を転送する分極転送デバイスと転送方向を選択する分極転送方向選択デバイスを強誘電体メモリのメモリセル群として用いることにより、強誘電体特性を確保し、微細化、高集積化に適した強誘電体メモリを得る。

(もっと読む)

強誘電性記憶素子、その素子を含むデバイス及びその製法

【課題】安価で非揮発性の記憶要素の提供。

【解決手段】 第1の電極システムが、少なくとも1個の強誘電性要素を含んでなる要素システムにより、第2の電極システムから少なくとも一部は絶縁されており、前記第1の電極システムが導電性表面又は導電性層であり、前記第2の電極システムが読み出し又はデータ・入力の目的のためのみに相互から隔離された複数の導電性ピンと接触している電極のパターン又は複数の隔離された導電性領域である、第1の電極システム及び第2の電極システムを含んでなる第1の受動強誘電性記憶要素を提供する。前記の第1の電極システム、前記の第2の電極システム及び前記の要素システムすべてが通常の印刷技術により印刷可能である。

(もっと読む)

白金薄膜の形成方法

【課題】酸化シリコンの上に剥離しにくい状態で、平坦性が優れて<111>方向に配向した白金の薄膜が形成できるようにする。

【解決手段】主表面が(100)面とされた単結晶シリコンからなるシリコン基板101を用意し、シリコン基板101の主表面に酸化シリコン層102が形成された状態とする。例えば、熱酸化法により酸化シリコン層102のが形成可能である。また、CVD(化学的気相成長法)により、酸化シリコン層102のが形成可能である。次に、白金ターゲットを用い、加えて酸素ガスを導入したECRスパッタ法により、酸化シリコン層102の上に、遷移層103を介して膜厚150〜200nm程度の白金薄膜104が形成された状態とする。

(もっと読む)

強誘電体記憶素子及び強誘電体記憶装置

【課題】本発明は、簡素な構造で高集積化に向くだけでなく、データを破壊することなくデータを読み出すことができる強誘電体記憶素子及び強誘電体記憶装置を提供する。

【解決手段】本発明に係る強誘電体記憶素子1Aは、互いに対向する第1及び第2電極11、14間に、有機強誘電体から成る有機強誘電体層12と該有機強誘電体層12の少なくとも一方面に有機半導体から成る有機半導体層13とが積層されている構造である。

(もっと読む)

半導体装置の製造方法

【課題】金属不純物捕獲能力の向上を図ることができ、且つ、素子分離構造のエッチングによる形状変化(片落ち)を抑制する。

【解決手段】シリコン酸化膜よりなる素子分離構造2が形成されたシリコン基板1上に、熱燐酸によりウェットエッチングに対するエッチング選択比が素子分離構造2に比較して高いシリコン窒化膜3を金属不純物捕獲膜として形成する。イオン注入後、熱燐酸によりウェットエッチングによりシリコン窒化膜3を除去する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】設計の自由度に優れ、また、微細化が可能な構造を有する、強誘電体膜を用いた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、基板11上に形成された下部電極12と、下部電極12の上に形成された強誘電体膜13と、強誘電体膜13の上に互いに間隔を置いて配置されたソース電極14及びドレイン電極15と、ソース電極14とドレイン電極15との間に形成された絶縁膜16とを備えている。

(もっと読む)

検出コンタクト・プローブ

【課題】マイクロカンチレバー梁の端部の位置及び角度の変わりやすさを低減するための方法及び装置を提供すること。

【解決手段】検出コンタクト・プローブは、梁支持部及びプローブを含む。このプローブは、梁支持部から、ある位置を占め、ある角度の方向に向いているプローブ先端面まで延びる曲げ梁本体を有する。曲げ梁本体は、互いに接合され、梁本体を曲げる異なる残留応力を有する、第1及び第2の梁層を有する。曲げ梁本体内に応力緩和領域が形成される。この応力緩和領域は、プローブ先端面の位置及び角度方向を制御するために曲げを調整する、調整応力特性を有する。

(もっと読む)

光電磁波変換方法および強誘電体の分極状態検出方法

【課題】 電圧を印加しなくても、テラヘルツ帯域の周波数成分を含む電磁波を放出する光電磁波変換方法および装置を提供する。

【解決手段】 本発明の光電磁波変換方法は、強誘電体層3を形成する強誘電体に、前記強誘電体のバンドギャップを超えるエネルギーのパルス光7を照射し、前記強誘電体からテラヘルツ帯域の周波数成分を含む電磁波8を放出させる。前記パルス光がフェムト秒パルス光であってもよい。前記強誘電体が、ペロブスカイト型強誘電体であってもよい。

(もっと読む)

成膜装置及び成膜方法

【課題】スパッタにより成膜された基板上のPZT膜への、防着板上の堆積膜からの再蒸発Pbの付着によるPb組成比の増加に関し、前記成膜におけるPb組成比の制御を可能にする。

【解決手段】スパッタ装置のチャンバ内に、基板表面より下側で、その基板を載置する支持台が搭載されたペデスタル側面とチャンバ底壁とを覆って、絶縁体を介して底壁に固定された下方防着板を設け、前記下方防着板に電位を印加可能のようにし、前記印加電位の制御によって、成膜PZT中のPb組成比を制御する。

(もっと読む)

SBT薄膜の形成方法

【課題】強誘電体メモリデバイスの作成が容易に行える半導体基板の上であっても、c軸方向以外の特定の方向へ配向したSBT薄膜が形成できるようにする。

【解決手段】ECRスパッタ法により基板温度(成膜温度)を370℃程度とした状態で、ストロンチウム(Sr)とビスマス(Bi)とタンタル(Ta)と酸素(O)とからなる金属酸化物(SBT)を基板101の上に堆積する。次に、酸素雰囲気中において、蛍石構造のSBT薄膜102(基板101)を800℃程度に加熱し、基板101の上に、<115>方向に配向したアウリビリウス(Aurivillus)構造のSBT薄膜103が形成された状態とする。

(もっと読む)

β‐ジケチミナート配位子源およびその金属含有化合物、およびそれらを含むシステムと方法

本発明は、一種以上のβ‐ジケチミナート配位子を含む金属含有化合物、およびそれらを生成する方法と使用する方法を提供する。或る実施形態では、金属含有化合物は一種以上のフッ素含有有機を置換基として持つ一種以上のβ‐ジケチミナート配位子を含む。他の或る実施形態では、金属含有化合物は、当該技術分野で周知の或る金属含有化合物のβ‐ジケチミナート配位子における対応する置換基よりも大きな自由度を有するように選択された一種以上の脂肪族基を置換基として持つ、一種以上のβ‐ジケチミナート配位子を含む。化合物は蒸着法を用いて金属含有層を堆積させるために利用できる。化合物を含む蒸着システムも提供される。β‐ジケチミナート配位子の源も提供される。 (もっと読む)

スイッチング素子

【課題】高速動作及び3D化が可能なメカニカルスイッチを提案する。

【解決手段】本発明の例に関わるスイッチング素子は、第1入出力電極13と、第1入出力電極13に対して接触/非接触を繰り返す可動部14と、可動部14に接続される第2入出力電極15と、可動部14に絶縁層16を介して結合され、電荷が蓄積されるフローティングゲート電極17と、フローティングゲート電極17との間で静電力を発生させ、可動部14の動作を制御する第1ゲート電極FGとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】膜厚測定を簡易化出来る半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板10の第1領域に、設けられた第1の半導体層13と、半導体基板10の第2領域上に、絶縁膜11を介在して設けられた第2の半導体層12と、半導体基板10の第3領域上に、絶縁膜11及び第2の半導体層12を介在して設けられた第3の半導体層13とを備え、第3領域内の第3の半導体層13の上面の高さは第2領域内の第2の半導体層12の上面の高さよりも高いことを特徴としている。

(もっと読む)

161 - 180 / 197

[ Back to top ]