Fターム[5F083FR00]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733)

Fターム[5F083FR00]の下位に属するFターム

キャパシタを有するもの(破壊読出型) (1,245)

MFS型(非破壊読出型) (230)

ブロック構造 (61)

Fターム[5F083FR00]に分類される特許

81 - 100 / 197

強誘電体膜、電子部品及び強誘電体膜の製造方法

【課題】結晶化しようとする強誘電体膜の配向を変換して任意に制御した強誘電体膜を提供する。

【解決手段】本発明の一態様に係る強誘電体膜は、基板上に形成された(111)配向したPt膜4と、前記Pt膜上に形成されたPZT膜6と、を具備し、前記PZT膜は、(111)+(001)、(001)、(001)+(110)及び(110)のいずれかに配向されていることを特徴とする。

(もっと読む)

強誘電体膜の評価方法及びそれを用いた液体噴射ヘッドの製造方法

【課題】亀裂の原因を判別することができる強誘電体膜の評価方法、及びこれを用いた、製造工程にすぐにフィードバックをかけることができる液体噴射ヘッドの製造方法を提供する。

【解決手段】強誘電体膜の評価方法は、一対の電極間に形成した強誘電体膜に電圧を印加して、強誘電体膜にリークを生じさせるリーク発生工程と、発生したリークの発生数を測定し、発生数に基づいて強誘電体膜の評価を行う評価工程とを備える。液体噴射ヘッドの製造方法は、圧電素子形成工程後、この強誘電体膜の評価方法を行い、強誘電体膜の評価が良い場合には圧力発生室形成工程を行う。

(もっと読む)

強誘電体薄膜の製造方法

【課題】基板の外周端部の膜をクラックや局部剥がれを生じることなく除去して、パーティクルの発生を防止する。

【解決手段】強誘電体薄膜形成用の有機金属化合物を含有するCSD溶液を基板2に塗布してゲル状塗膜1を形成する工程と、基板2を回転させながら外周端部に水Wを噴射又は滴下して、ゲル状塗膜1の外周端部を除去する工程と、外周端部について除去された後のゲル状塗膜1を加熱処理して強誘電体薄膜を形成する工程とを有する。

(もっと読む)

強誘電体メモリ素子の製造方法

【課題】分極方向の均一性が高められた強誘電体層を有し、書き込み及び読み出しに際しての精度を高め得る強誘電体メモリ素子の製造方法。

【解決手段】基板2上に電極3が形成されており、電極3上に強誘電体層4が積層されている積層体を用意し、積層体の強誘電体層4の上面4a上に、強誘電体層4を構成している金属元素の単体または化合物からなる改質材料板5を配置する工程と、改質材料板5が配置された状態で積層体を熱処理する、強誘電体メモリ素子1の製造方法。

(もっと読む)

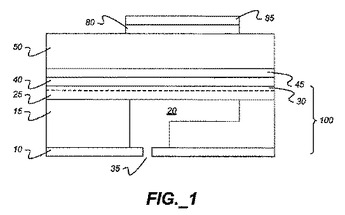

半導体装置

【課題】回路を形成する領域を確保しつつ、十分な耐圧、容量を備えた容量素子を備える半導体装置を提供する。

【解決手段】半導体装置は、DRAMセルのキャパシタ上部電極19と、上部電極19の下方に形成されたキャパシタ下部電極17とを含む情報記憶部と、情報記憶部へのアクセスを制御するアクセストランジスタとを有するメモリセルと、アクセストランジスタに接続され、情報記憶部にデータの書き込み又は読み出しを行うビット線16と、アクセストランジスタのゲート電極に接続され、アクセストランジスタを制御するワード線と、キャパシタ上部電極19の上方に形成された第1金属配線21と同一層からなる上部電極23と、キャパシタ上部電極19と同一層の下部電極22とを有し、メモリセルが形成された領域外に形成された容量素子とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

積層メモリ素子

【課題】高集積化が容易な積層メモリ素子を提供する。

【解決手段】本願発明の積層メモリ素子は、基板と、基板上に互いに積層された、少なくとも1層のメモリ層をそれぞれ含む複数のメモリグループと、該複数のメモリグループのうち、複数の隣接した2つのメモリグループ間に介在する複数のXデコーダ層と、前記複数の隣接した2つのメモリグループ間に、複数のXデコーダ層と交互に介在される複数のYデコーダ層と、を具備する積層メモリ素子である。

(もっと読む)

PZT薄膜の形成方法及び半導体装置の製造方法

【課題】基板面内の膜組成分布を向上せしめると共に、基板面内の結晶粒の発生の微視的なバラツキを抑制し、さらに表面ラフネスの向上を達成することができるPZT薄膜の形成方法及びこの薄膜を含んでなる半導体装置の製造方法の提供。

【解決手段】Pb、Zr及びTi用のそれぞれの有機金属化合物原料として、Pb(thd)2及びPb(dmhd)2から選ばれた1種類のPb用有機金属化合物原料と、Zr(dmhd)4、Zr(thd)2(dmhd)2、Zr(thd)3(dmhd)、Zr(i−PrO)2(thd)2、及びZr(i−PrO)(thd)3から選ばれた1種類のZr用有機金属化合物原料と、Ti(i−PrO)2(dmhd)2のTi用有機金属化合物原料とを用いる。この強誘電体薄膜を含む半導体装置を製造する。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】従来の強誘電体薄膜よりも低いリーク電流密度、かつ、高い絶縁耐圧が得られる、薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、Siを含む複合酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、複合金属酸化物Aを構成するための原料並びに複合金属酸化物Bを構成するための原料が上記一般式で示される金属原子比を与えるような割合で有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

積層メモリ素子

【課題】集積度を高めることが容易な3次元積層された多層構造メモリ素子を提供する。

【解決手段】本積層メモリ素子は、基板と、基板上に相互積層され、複数の群に分割された複数のメモリ層と、各群内のメモリ層と電気的に接続され、各群内のメモリ層の間に配された複数のインターデコーダと、複数のインターデコーダと電気的に接続され、複数のインターデコーダの間に配された少なくとも一つのプレデコーダと、を備えることを特徴とする。

(もっと読む)

圧電体膜とその成膜方法、圧電素子、及び液体吐出装置

【課題】配向制御層や保護膜等の圧電素子として本来必要でない膜を必須とせず、複雑なプロセスを要することなく、圧電性能と耐電圧とがいずれも良好な圧電体膜を提供する。

【解決手段】圧電素子1は、基板10上に、下部電極20と圧電体膜30と上部電極40とが順次積層された素子であり、圧電体膜30は、膜表面における最大高さ(ピーク値P)と最小高さ(バレー値V)との差で規定される表面粗さP−V値が170.0nm以下であり、圧電定数d31>150pc/Nであり、かつ、電流値が1μA以上となる印加電圧により定義される絶縁破壊電圧が80V以上である。

(もっと読む)

強誘電体、圧電体及びこれらの製造方法

【課題】強誘電特性及び圧電特性の劣化が抑制され、リーク特性が改善された強誘電体及び圧電体を提供する。

【解決手段】BiFeO3を主成分とする強誘電体及び圧電体13は、BiFeO3の複数のFeサイトが、Tiと、Mn、Ni及びCuのいずれかとに元素置換されている。BiとFeとTiとMn、Ni及びCuのいずれかとからなるターゲットにパルスレーザを照射することで、基板11上に、BiとFeとTiとMn、Ni及びCuのいずれかとを堆積させることにより、BiFeO3を主成分とする強誘電体又は圧電体13の製造方法。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】簡便な手法で、従来の強誘電体薄膜よりも大幅に比誘電率を向上し得る、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、Y(イットリウム)を含む複合金属酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、各原料が上記一般式で示される金属原子比を与えるような割合で、かつ、BとAとのモル比B/Aが0.005≦B/A<0.03の範囲内となるように、有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】リーク電流の低減と絶縁耐圧の向上の両特性をバランスよく改善することができる、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、P(燐)を含む複合酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、複合金属酸化物Aを構成するための原料並びに複合酸化物Bを構成するための原料が上記一般式で示される金属原子比を与えるような割合で有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】簡便な手法で、従来の強誘電体薄膜よりも大幅に比誘電率を向上し得る、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、Smを含む複合金属酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、各原料が上記一般式で示される金属原子比を与えるような割合で、かつ、BとAとのモル比B/Aが0.005≦B/A<0.03の範囲内となるように、有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】簡便な手法で、従来の強誘電体薄膜よりも大幅に比誘電率を向上し得る、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、Snを含む複合金属酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、各原料が上記一般式で示される金属原子比を与えるような割合で、かつ、BとAとのモル比B/Aが0.003≦B/A≦0.05の範囲内となるように、有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜

【課題】従来の強誘電体薄膜と同程度の比誘電率を有し、かつ、低いリーク電流密度が得られる、高容量密度の薄膜キャパシタ用途に適した強誘電体薄膜形成用組成物、強誘電体薄膜の形成方法並びに該方法により形成された強誘電体薄膜を提供する。

【解決手段】PLZT、PZT及びPTからなる群より選ばれた1種の強誘電体薄膜を形成するための強誘電体薄膜形成用組成物であり、一般式:(PbxLay)(ZrzTi(1-z))O3(式中0.9<x<1.3、0≦y<0.1、0≦z<0.9)で示される複合金属酸化物Aに、Ceを含む複合金属酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、各原料が上記一般式で示される金属原子比を与えるような割合となるように、有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

スパッタされた圧電材料

Pb1.00+x(Zr0.52Ti0.48)1.00−yO3Nby(式中、x>−0.02且つy>0)の組成を有する圧電アクチュエータが記載される。この圧電材料は、アクチュエータにバイアスを印加した際に良好な屈曲作用を呈することができるペロブスカイトを有しうる。  (もっと読む)

(もっと読む)

圧電材料および圧電素子

【課題】圧電特性が良好な圧電材料を提供する。

【解決手段】下記一般式(1)で表されるペロブスカイト型複合酸化物からなり、前記ペロブスカイト型複合酸化物の結晶系が少なくとも単斜晶構造を含んでいる圧電材料。前記ペロブスカイト型複合酸化物の結晶系が、単斜晶構造と菱面体晶構造を有する混在系、または単斜晶構造と正方晶構造を有する混在系であることが好ましい。

(式中、AはBi元素であり、MはFe、Al、Sc、Mn、Y、Ga、Ybのうちの少なくとも1種の元素である。xは0.4≦x≦0.6の数値を表す。yは0.17≦y≦0.60の数値を表す。)

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】加工精度の向上等が可能な不揮発性記憶装置、集積回路装置及び電子機器を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え可能な不揮発性の複数のメモリーセル及び複数のビット線が配置される主記憶回路10と、電気的に書き換え可能な不揮発性の複数の情報メモリーセル及び複数のビット線が配置され、少なくとも主記憶回路10の不良メモリーセルのアドレス情報を記憶する情報記憶回路20と、主記憶回路10の複数のビット線のうちの対応ビット線と情報記憶回路20の複数のビット線のうちの対応ビット線との電気的接続をオン状態又はオフ状態にするための選択トランジスターが配置される選択回路30とを含み、情報記憶回路20は主記憶回路10と選択回路30との間に配置される。

(もっと読む)

81 - 100 / 197

[ Back to top ]