Fターム[5F083FR00]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733)

Fターム[5F083FR00]の下位に属するFターム

キャパシタを有するもの(破壊読出型) (1,245)

MFS型(非破壊読出型) (230)

ブロック構造 (61)

Fターム[5F083FR00]に分類される特許

181 - 197 / 197

半導体装置及びその製造方法

【課題】膜厚測定を簡易化出来る半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板10の第1領域に、設けられた第1の半導体層13と、半導体基板10の第2領域上に、絶縁膜11を介在して設けられた第2の半導体層12と、半導体基板10の第3領域上に、絶縁膜11及び第2の半導体層12を介在して設けられた第3の半導体層13とを備え、第3領域内の第3の半導体層13の上面の高さは第2領域内の第2の半導体層12の上面の高さよりも高いことを特徴としている。

(もっと読む)

強誘電体コンデンサラッチ回路

【課題】

従来の主な強誘電体メモリはデータを破壊読み出しするので再書き込みを必要とするか、あるいはメモリセルを行列状に配置して、データを破壊しなとような制御をしていた。したがって、制御回路が複雑で、かつデータ読み出しの際のサイクルタイムが長く、一般的ICの中に取り組むのが容易でなかった。

【解決手段】

強誘電体薄膜を有する強誘電体コンデンサと、MOSFETからなるインバータ回路を2個たすき掛けにしたラッチ回路を組み合わせた構成とした。

(もっと読む)

強誘電体コンデンサラッチ回路

【課題】データの読み書きの際に格別な制御方式や手順を必要とせず、通常のMOSFET回路と同じような取り扱いができ、かつ占有面積も少ない不揮発性ラッチ回路の提供

【解決手段】この発明は、ラッチ回路を構成するインバータ回路135、146からなるラッチ回路と、強誘電体コンデンサ11、12と、コンデンサ191、192とを少なくとも備え、これらにより不揮発性のラッチ回路を構成した。この発明は、上記構成により、電源の切断時に1ビットのデータを保持でき、電源再投入後には、強誘電体コンデンサ11、12の残留分極による電荷の偏りによって、電源切断時におけるラッチ回路のデータの保持状態に速やかに復帰できるようにした。さらに、回路自体の構成がデータの書き込み回路とデータ出力回路を兼ねることができ、余分な制御回路や読み出し、書き込みの手順を不要にするようにした。

(もっと読む)

磁気抵抗メモリを有するシングルチップ

シングルチップは、基板と、少なくとも1つの磁気抵抗メモリ層とを有する。基板は、下地メモリ及び制御回路を有する。磁気抵抗メモリ層は、基板上に位置し、制御回路により制御された複数の磁気抵抗ランダムアクセスメモリセルを有する。 (もっと読む)

半導体装置の製造方法、製造装置、シミュレーション方法、及びシミュレータ

【課題】 半導体装置製造プロセスを、テストピースなしに、所望の工程通り又は修正しながら進行することを可能とする半導体装置の製造方法を提供すること。

【解決手段】 複数の工程からなる半導体装置の製造方法において、前記複数の工程の少なくとも1つにおける実観測データを得る工程と、abinitio分子動力学プロセスシミュレータ又は経験的ポテンシャルを与えた分子動力学ミュレータにより、前記複数の工程の少なくとも1つにおける予測データを得る工程と、前記予測データと実観測データとを逐次、実時間で比較検定する工程と、前記比較検定により、製造工程因子の設定値と、前記実観測データから推測される前記複数の製造工程因子との間に有意差が認められた場合、前記製造工程因子を逐次実時間で修正処理する工程とを具備することを特徴とする。

(もっと読む)

強誘電体粒子の単一分域化方法及び強誘電体粒子の単一分域化装置

【課題】 結晶軸の方位が予め判明していない多数の強誘電体粒子からなる強誘電体に対しても、複数の強誘電体粒子の分域の向きを一方向に揃える強誘電体粒子の単一分域化方法を提供する。

【解決手段】 強誘電体粒子102に対して互いに異なる複数方向の電界を印加することにより、分極発現方向と電界印加方向との間に形成される角度のうち最も小さい角度を形成する印加方向の電界が分極の反転に寄与するので、強誘電体粒子に対して1方向の電界を印加する場合に比べて、強誘電体粒子の分極の向きを一方向に揃えるために要する電界の値を少なくすることが出来る。

(もっと読む)

強誘電体薄膜の製造方法

【課題】 電気泳動堆積法を用い、強誘電体微粒子の分極方向を揃えて基板上に堆積することによって強誘電体薄膜を形成する。この際に、基板内に形成された電子素子の破壊等の損傷を軽減する。

【解決手段】 強誘電体薄膜の製造方法は、基板105が入れられた液体103aと、強誘電体微粒子104bが分散された分散液104aとを、強誘電体微粒子104bが分散液104aから液体103aに対して拡散することができるように配置する工程と、分散液104a中の強誘電体微粒子104bの周囲に電界を形成して分散液104a中の強誘電体微粒子104bを基板105に向けて泳動させることにより、基板105上に強誘電体微粒子104bを堆積させる工程とを備え、基板105は、分散液104aから所定の距離以上離して配置されるようになっている。

(もっと読む)

発光材料、圧電体、電歪体、強誘電体、電場発光体、応力発光体、及びこれらの製造方法

【課題】 摩擦力、剪断力、衝撃力などの機械的な外力が加えられることによって生じる変形によって発光する新規な発光材料を提供する。

【解決手段】 本発明の発光材料は、ウルツ鉱型構造の酸化亜鉛と、立方晶又はウルツ鉱型構造の硫化亜鉛と、立方晶の酸化マンガンとの結晶構造の中から少なくとも2種類以上の結晶構造を有するものや、一般式(Ca1−xA’x)yBa1−yTiO3、(Mg1−xA’x)yBa1−yTiO3、及び(Sr1−xA’x)yBa1−yTiO3(0.0001≦x≦0.05,0.005≦y≦0.995,A’はDy,La,Gd,Ce,Sm,Y,Nd,Tb,Pr,Erからなる群より選ばれる希土類元素)からなるもの等のような、複数の結晶構造が混在した混相を含んでいる。

(もっと読む)

強誘電体薄膜の製造方法および基板

【課題】a分域の発生を抑制しつつ、内面にホールが形成されることなく、平坦性に優れた強誘電体薄膜を得ることができる強誘電体薄膜の製造方法を提供する。

【解決手段】ペロブスカイト型強誘電体生成用の前駆化合物及び水を含む反応液に、ミスカット表面を持つ基板を浸漬した後、ペロブスカイト型強誘電体の相転移温度より低い温度で反応液を水熱合成することにより、基板のミスカット表面上にペロブスカイト型強誘電体層が形成される。

(もっと読む)

不揮発性メモリ回路

【課題】電源電圧を印加しなくてもデータを記憶できる不揮発性メモリ回路及び不揮発性メモリ装置に関し、書き込み・読み出しを最適に行なえる不揮発性メモリ回路及び不揮発性メモリ装置を提供することを目的とする。

【解決手段】本発明は、不揮発性メモリ回路であって、第1又は第2のビット線に印加される電圧により不可逆的に内部回路を劣化させてデータを不揮発的にラッチするフリップフロップと、フリップフロップの第1の出力端子と前記第1のビット線との間に接続された第1スイッチと、フリップフロップの第1の出力端子と第1のビット線との間に接続された第2スイッチと、フリップフロップの第1の出力端子の出力を反転した出力を行なう第2の出力端子と第2のビット線との間に接続された第3スイッチと、フリップフロップの第2の出力端子と第2のビット線との間に接続された第4スイッチとを有することを特徴とする。

(もっと読む)

CVD用気化器、溶液気化式CVD装置及びCVD用気化方法

【課題】 CVD用の原料溶液の流量を長時間にわたって精度よく制御することができるCVD用気化器、溶液気化式CVD装置及びCVD用気化方法を提供する。

【解決手段】 本発明に係るCVD用気化器は、キャリアガス中に1種又は2種以上の原料溶液を微粒子状又は霧状に分散させるオリフィス管と、前記オリフィス管に前記1種又は2種以上の原料溶液を互いに分離して供給する1種又は2種以上の原料溶液用通路21〜25と、前記オリフィス管に前記キャリアガスを前記1種又は2種以上の原料溶液それぞれと互いに分離して供給するキャリアガス用通路33と、前記オリフィス管で分散された前記1種又は2種以上の原料溶液を気化する気化管31と、前記気化管と前記オリフィス管が繋げられ、前記オリフィス管で分散された前記原料溶液が前記気化管に導入される細孔と、を具備することを特徴とする。

(もっと読む)

ポリマー電極を有する強誘電性ポリマーメモリ装置及びその製造方法

導電性ポリマー電極を有する強誘電体メモリモジュールの製造方法と該方法に従って製造される強誘電体メモリモジュールとが開示される。強誘電性ポリマーメモリモジュールは、内部にトレンチを規定するILD層(102);トレンチ内に配置された第1電極層(104);第1電極層(104)上に配置された第1導電性ポリマー層(106);第1導電性ポリマー層(106)上に配置された強誘電性ポリマー層(108)を含む第1レイヤーセットを有する。該モジュールは更に、内部にトレンチを規定するILD層(114);ILD層(114)のトレンチ内に配置された第2導電性ポリマー層(112);第2導電性ポリマー層(112)上に配置された第2電極層(116)を含む第2レイヤーセットを有する。第1導電性ポリマー層(106)及び第2導電性ポリマー層(112)は、電極層(104、116)と強誘電性ポリマー層(108)との間に反応障壁及び/又は拡散障壁をもたらすように電極層(104、116)を覆う。  (もっと読む)

(もっと読む)

強誘電体材料の製造方法(放電プラズマ焼結による一軸配向性強誘電体セラミックスの合成)

【課題】 ビスマス層状構造強誘電体の分極軸をそろえ、配向性・結晶性が向上した強誘電体材料を提供する。

【解決手段】 アモルファス粉体をマトリックスとし、このマトリックスに前記アモルファス粉体と、板状結晶と、を所定量混合した粉体試料を一軸加圧成形しながら加圧方向と平行に直流パルス電流を印加することにより焼結した。

(もっと読む)

集積メモリデバイスおよびその製造方法

【課題】容易に製造可能であり、セルのサイズの縮小を可能にするメモリデバイスを提供する。

【解決手段】 本発明の、トンネル電界効果トランジスタ(TFET)と埋込みビット線とを用いたメモリデバイスには、記憶セルの行および列を含む行列が含まれる。各記憶セルには、少なくとも1つのセルトランジスタ(T01〜Tmn)が含まれ、そのセルトランジスタは第1のドープされた領域と第2のドープされた領域とを含んでおり、一方がソース領域(98)であり、もう一方がドレイン領域(152)である。そのメモリデバイスにはワード線(T01〜Tmn)が含まれ、各ワード線は1つの行にあるメモリセルとビット線とに接続されており、各ビット線は1つの列における記憶セルに接続されている。第1のドープされた領域と第2のドープされた領域のドーピングタイプは異なる。

(もっと読む)

半導体装置の製造方法

【課題】深さの異なる溝に絶縁膜を埋め込んで素子分離を形成するに際して、各素子分離の半導体基板表面からの高さを均等とし、高品質の半導体装置を製造する半導体装置の製造方法を得ること。

【解決手段】半導体基板上に第1〜第3のマスク層を形成し、第3及び第2のマスク層において深さの深い第1の素子分離及び深さの浅い第2の素子分離の対応領域をエッチングし、第1のマスク層において第1の素子分離の対応領域をエッチングし、第3及び第1のマスク層をマスクとして半導体基板における第1の素子分離の形成領域をエッチングして第1の溝を形成し、第1のマスク層における第2の素子分離に対応する領域をエッチングし、第3のマスク層をマスクとして半導体基板における第1の素子分離及び第2の素子分離の形成領域をエッチングして第2の溝を形成すると共に第1の溝をさらに深堀し、第1の溝及び第2の溝に絶縁膜を埋め込み、絶縁膜を平坦化する。

(もっと読む)

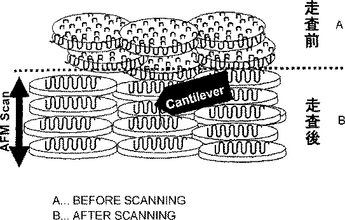

薄膜及びその製造方法

本発明は、任意の微小な領域のみを構造制御する全く新しい薄膜の製造方法を提供することを目的とする。製膜途中または製膜後の膜全体または膜内の任意の部分について、その膜温度を非晶部のガラス転移温度以上に設定した上で、鋭利な先端形状を有する部材を用いて力を加えることにより、膜の構造を制御するようにした。本製造方法を実現する装置として、原子間力顕微鏡を用いることもできる。  (もっと読む)

(もっと読む)

強誘電性およびエレクトレットメモリセルおよびデバイスの双峰動作

データ記憶に適用されインプリント状態をとった強誘電性またはエレクトレットメモリセルのデータ記憶能力を高めるための方法において、非破壊的読出動作におけるインプリント分極状態から区別できる揮発性分極状態へのインプリント状態の一時的緩和を誘起するために適切な電圧パルスが使用される。メモリセルのそれぞれ、不揮発性および揮発性分極状態を示す読出信号を誘起するのに1つ以上の電圧パルスのシーケンスが使用されるが、前記分極状態は変えない。インプリントメモリセルに第1の論理値を割り当てかつ緩和揮発性状態へ移転されたメモリセルに選択された移転により第2の論理値を割当てることにより、インプリントメモリセルをオーバライトして強誘電性またはエレクトレットメモリデバイス内でメモリデバイス内のデータの一時記憶すなわち揮発性記憶を行うことができ、記憶された論理値はインプリントメモリセルおよび緩和メモリセルのダイナミック応答の差を検出して区別することができる。  (もっと読む)

(もっと読む)

181 - 197 / 197

[ Back to top ]