Fターム[5F083FR00]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733)

Fターム[5F083FR00]の下位に属するFターム

キャパシタを有するもの(破壊読出型) (1,245)

MFS型(非破壊読出型) (230)

ブロック構造 (61)

Fターム[5F083FR00]に分類される特許

141 - 160 / 197

強誘電体膜とその製造方法、強誘電体素子、及び液体吐出装置

【課題】PZT系の強誘電体膜において、焼結助剤やアクセプタイオンを添加することなく、Bサイトに10モル%以上のドナイオンを添加することを可能とする。

【解決手段】本発明の強誘電体膜は、多数の柱状結晶からなる柱状結晶膜構造を有し、下記式(P)で表されるペロブスカイト型酸化物を主成分とするものである。

A1+δ[(ZrxTi1−x)1−yMy]Oz・・・(P)

(式中、AはAサイト元素であり、Pbを主成分とする少なくとも1種の元素である。Zr,Ti,及びMはBサイト元素である。MはV,Nb,Ta,及びSbからなる群より選ばれた少なくとも1種の元素である。0<x≦0.7、0.1≦y≦0.4。δ=0及びz=3が標準であるが、これらの値はペロブスカイト構造を取り得る範囲内で基準値からずれてもよい。)

(もっと読む)

半導体装置及びその作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体領域を用いて形成された半導体素子を有する素子基板上に、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着することにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体及び素子基板が固着された半導体装置を作製する。

(もっと読む)

強誘電性の積層体とその製造方法

【課題】常温でもI型結晶構造を多く含む強誘電性の積層体とその製造方法を提供する。

【解決手段】フッ化ビニリデン系ポリマーを含むポリマー層の片面に、フッ化ビニリデン系オリゴマーを含むオリゴマー層が積層されてなる積層体。

(もっと読む)

圧電体薄膜、これを用いた圧電体素子、圧電アクチュエータ、インクジェット記録ヘッド

【課題】 不均一部分が少なく、かつ良好な圧電特性を保持した圧電体薄膜、この圧電体薄膜を用いた圧電体素子、本圧電体素子を用いた圧電アクチュエータおよびインクジェット式記録ヘッドを提供する。

【解決手段】一般式Pb(1-x)Lax(ZryTi1-y)O3(式中、0≦x<1、0.05≦y≦1)で表されるペロブスカイト型結晶の圧電体薄膜において、該薄膜の膜厚を1000nm以上4000nm以下とし、該薄膜の任意の箇所における組成のy値の最大値と最小値の差を0.05以下とする。

(もっと読む)

強誘電体ナノドットを有する強誘電体情報記録媒体及びその製造方法

【課題】強誘電体ナノドットを有する強誘電体情報記録媒体及びその製造方法を提供する。

【解決手段】強誘電体ナノドットを有する強誘電体情報記録媒体は、基板10と、基板10上に形成された下部電極20と、下部電極20上に形成された強誘電体ナノドット32とを具備し、強誘電体ナノドット32は、互いに離隔するように形成され、複数の強誘電体ナノドットが1つのビット領域を形成する。ヘッド40と下部電極20との間に電圧パルスを印加すれば、強誘電体ナノドット32の分極が変化しうる。電圧の符号によって、分極方向が上向きまたは下向きになる。このような分極状態の読み取りは、記録/読み取りヘッド40を利用して検出でき、強誘電体ナノドット32からなる1ビット領域の記録データを読み取ることが可能である。

(もっと読む)

強誘電体薄膜

【課題】高密度のメモリデバイスとして有用な強誘電体メソ結晶を基板表面に配向して規則正しく並んだ構造の強誘電体薄膜およびその製造方法の提供。

【解決手段】各種基板上へスピンコーティングにより原料溶液を塗布(1段目、2000回転、10秒、2段目、4000回転、30秒)し、その後、大気中で熱処理して規則的に配列されたナノサイズの細孔からなる珪酸塩メソ多孔体薄膜を作製する。次に強誘電体前駆体溶液を合成し、この溶液中に珪酸塩メソ多孔体薄膜の形成された基板をつけ込み、1日静置し、取り出した後、空気中で焼成することにより珪酸塩ナノ多孔質薄膜の細孔内に強誘電体メソ結晶が充填されてなる強誘電体担持薄膜を作製する。

(もっと読む)

スタックにおける電気的相互垂直接続

【課題】基板により支持され、又はサンドイッチ自己支持構造を形成した少なくともスタックされた2層を有するメモリ及び/又はデータ処理装置の提供である。

【解決手段】前記層は、メモリ及び/又は前記層間及び/又は前記基板における回路に対する相互接続を有する処理回路を備え、前記層は、連続する層が前記装置の少なくとも1エッジ上にジグザク構造を形成するように相互に配列され、少なくとも1エッジ電導体を一度に1層のエッジを越え、1ステップ下がって設けて、前記スタックにおいて次に続く層のいずれかにおける導電体に対する接続を可能にする。この種の装置を製造する方法は、複数の層がジグザク構造を形成するように1度に1層を連続的に前記複数の層に付加する工程と、1以上の層に少なくとも1電気接触パッドを設けて1以上の中間層エッジ・コネクタに連結させる工程を備えている。

(もっと読む)

圧電磁器および圧電素子

【課題】 圧動的d33定数が大きく、200℃の高温下においても使用可能であり、室温の動的d33定数に対する200℃の動的d33定数の変化の小さい圧電磁器および圧電素子を提供する。

【解決手段】 圧電磁器を組成式でBi4Ti3O12・β[(1−γM1TiO3・γM2M3O3]と表したとき、0.405≦β≦0.498、0≦γ≦0.3を満足するとともに、M1が、Sr、Ba、Ca、(Bi0.5Na0.5)、(Bi0.5Li0.5)および(Bi0.5K0.5)のうち少なくとも1種であり、M2が、Bi、Na、KおよびLiのうち少なくとも1種であり、M3が、FeおよびNbのうち少なくとも1種であるビスマス層状化合物の主成分100質量部に対して、MnおよびFeのうち少なくとも1種を酸化物(MnO2、Fe2O3)換算の合量で0.05〜1質量部含有することを特徴とする。

(もっと読む)

使用済みコロイド溶液の再生方法

【課題】再生過程において不溶性沈殿物を発生させることなく、かつ使用済みコロイド溶液中に含まれる鉛及びジルコニウムを外部環境に排出することなく、使用済みコロイド溶液を再生することができる使用済みコロイド溶液の再生方法を提供する。

【解決手段】使用済みコロイド溶液を加熱して該使用済みコロイド溶液に含まれる酢酸を除去する加熱工程と、前記加熱工程によって析出した析出物を前記使用済みコロイド溶液から分離する分離工程と、前記析出物を、分散剤を含む溶液に溶解させて再生コロイド溶液を作製する溶解工程と、前記再生コロイド溶液にチタン化合物を加えて、使用される前の前記コロイド溶液中のチタンの濃度と等しくなるように前記再生コロイド溶液中のチタンの濃度を調整する調整工程とを具備する。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】基板表面と基板上に形成された配線とで形成される段差部分にシリコン膜を形成した場合においても、メモリ素子の書き込み特性を低下させない半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】絶縁表面を有する基板10上に形成された第1の電極11と、第1の電極11の側壁部に形成されたサイドウォール絶縁層12と、第1の電極11上及びサイドウォール絶縁層12を覆って形成されたシリコン膜13と、シリコン膜13上に形成された第2の電極14と、を有し、第1の電極11又は第2の電極14は、シリコン膜13と合金化する材料で形成されているメモリ素子を複数有している。

(もっと読む)

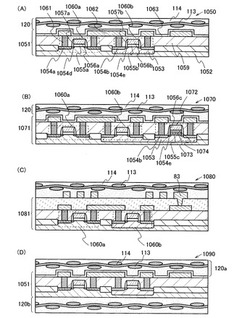

半導体メモリ素子の製造方法

【課題】エッチング方法を変化させてビットラインの損失を防止する半導体メモリ素子の製造方法を提供する。

【解決手段】第1の絶縁膜102上に金属配線層とエッチング停止膜112を形成する。金属配線層とエッチング停止膜112をパターニングして金属配線110を形成する。そして、第1の絶縁膜102上に第2の絶縁膜114を形成し、エッチング停止膜112が露出されるように第1のエッチングガスで第2の絶縁膜114の一部をエッチングする。続いて金属配線110が露出されるように第2のエッチングガスでエッチング停止膜112を除去する。それによって、たとえば比抵抗が低いアルミニウムを金属膜106として用い、そのアルミニウム金属膜106によるビットラインにビアホール120を連結する際、エッチングガスを変化させるだけで別途に追加膜を形成せずともアルミニウム金属膜106のエッチング損傷を抑制できる。

(もっと読む)

メモリデバイス構造の洗浄製剤

【課題】キャッピング層及び絶縁層のマイクロ電子デバイスからの除去に関する改良された組成物を提供する。

【解決手段】シリコン含有層を、かかる層をその上に有するマイクロ電子デバイスから除去する除去組成物及び方法を開示する。除去組成物は、次のものに限定されないが、シリコン酸化物、プラズマエンハンスド・テトラエチルオルソシリケート(P−TEOS)、ボロホスホシリケートガラス(BPSG)、プラズマエンハンスド酸化物(PEOX)、高密度プラズマ酸化物(HDP)、ホスホシリケートガラス(PSG)、スピンオン誘電体(SOD)、熱酸化物、アップドープされたシリケートガラス、犠牲酸化物類、シリコン含有有機ポリマー類、シリコン含有ハイブリッド有機/無機材料類、有機シリケートガラス(OSG)、TEOS、フッ素化シリケートガラス(FSG)、半球状グレイン(HSQ)、炭素ドープされた酸化物(CDO)ガラス、及びこれらの組み合わせを含む総を、下部電極、デバイス基板、及び/又はエッチストップ層の材料に対して、選択的に除去する。

(もっと読む)

薄膜トランジスタ及びその作製方法、並びに半導体装置

【課題】レーザー結晶化法により、粒界が一方向に揃った結晶質半導体膜と、その作製方法を提供する。

【解決手段】基板上に形成した半導体膜を線状レーザー光により結晶化するに際して、ストライプ状に凹凸が形成された位相シフトマスクを用いる。位相シフトマスクに形成されたストライプ状の凹凸は線状レーザー光の長軸方向と垂直に近い角度をなすように形成されている。レーザー光には連続発振のレーザー光を用い、該レーザー光の走査方向はストライプ状の凹凸(溝)の方向とほぼ平行である。長軸方向に周期的にレーザー光の輝度を変化させることによって、完全溶融した半導体膜の結晶核生成位置を制御することができる。

(もっと読む)

強誘電体組成物

【課題】塗布法で形成した場合でもムラができず、均一な厚みの強誘電体層が形成できる強誘電体塗布用組成物を提供する。

【解決手段】オクチル酸金属化合物を主成分とする、強誘電体塗布用組成物であって、

バインダーと、少なくとも1種以上の溶媒とを含んでなり、前記オクチル酸金属化合物の金属が、Zr、Ba、Ti、La、およびPbの群から選択される少なくとも2種以上のものであり、前記強誘電体塗布用組成物全体に対して、1〜10重量%含む。

(もっと読む)

情報記録媒体

【課題】半導体層とこの半導体層上に形成された強誘電体の層とを有する情報記録媒体において、比較的低い記録電圧で、迅速な記録を行うことが可能な記録媒体を与える。

【解決手段】前記情報記録媒体において、前記半導体層の厚みが、強誘電体の分極反転時に、半導体層が十分厚い場合に、過渡的に半導体層中に生じる空乏層の最大厚みに対して、薄い事を特徴とする情報記録媒体を用いる。

(もっと読む)

メモリセル及び不揮発性記憶装置

【課題】DRAM装置と同等の動作速度を維持しかつ電源切断時にデータを記憶する。

【解決手段】第1の制御用信号線に第1制御端子が接続され、第1の端子がビット線に接続された第1の電界効果トランジスタと、一端が上記第1の電界効果トランジスタの第2の端子に接続され、他端が第1の基準電位に接続されたキャパシタと、第1の電界効果トランジスタの第2の端子と上記キャパシタの一端が接続された記憶ノードに第3の端子が接続され、第2の制御端子が第2の制御用信号線に接続された第2の電界効果トランジスタと、一端が第2の電界効果トランジスタの第4の端子に接続され、他端が第2の基準電位に接続された不揮発性記憶素子とを有し、リフレッシュ動作の一分を代替すると共に電源オフ時に情報を記憶する。

(もっと読む)

分析方法

【課題】半導体装置等の製造において発生する水素が、当該半導体装置等に与える影響、例えばFRAMの製造においてキャパシタ膜である強誘電体膜に及ぼされる、当該強誘電体膜の弱点である水素による様々な影響を、分析用試料を用いて定量的に正確に把握することを可能とする。

【解決手段】シリコンウェーハ11上に、水素を吸蔵する性質を有するTi膜12と、水素を含む雰囲気で成膜されるHDP−SIO膜13とを順次積層形成し、分析用試料10を作製する。この分析用試料10を用いて、TDS分析を行い、その結果をPZT膜への水素によるダメージの定量的評価として供する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体膜を用いたキャパシタ型の不揮発性メモリにおいて、リーク電流を低減する。

【解決手段】半導体記憶装置は、基板(11)上に形成された第1の導電膜(12)と、第1の導電膜(12)の上に順に形成された第1の絶縁膜(13)、強誘電体膜(14)及び第2の絶縁膜(15)よりなる積層膜と、第2の絶縁膜(15)の上に選択的に形成された第2の導電膜(16)と、強誘電体膜(14)の上又は下に、第1の導電膜(12)と第2の導電膜(16)との間の領域の少なくとも一部を挟むように配置され、且つ、第1の絶縁膜(12)又は第2の絶縁膜(15)と接する第1のソース電極(17)及び第1のドレイン電極(18)とを備えている。

(もっと読む)

141 - 160 / 197

[ Back to top ]