Fターム[5F083FR01]の内容

Fターム[5F083FR01]の下位に属するFターム

Fターム[5F083FR01]に分類される特許

341 - 352 / 352

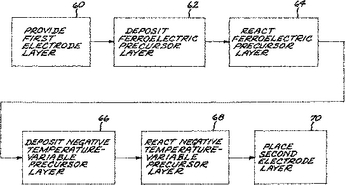

温度補償された強誘電キャパシタ装置およびその製造方法

温度補償されたキャパシタ装置20は、強誘電特性を有し、金属酸化物の強誘電材料のような強誘電材料を使用する強誘電キャパシタ22と、金属酸化物の常誘電材料のような負の温度係数のキャパシタンス材料を使用する負の温度可変キャパシタ24と、負の温度可変キャパシタ24と強誘電キャパシタ22との間の電気的に直列の接続26とを含んでいる。温度補償されたキャパシタ装置20は間にディスクリートな電気接続を有する集積された積層構造または別々のキャパシタとして形成されることができる。  (もっと読む)

(もっと読む)

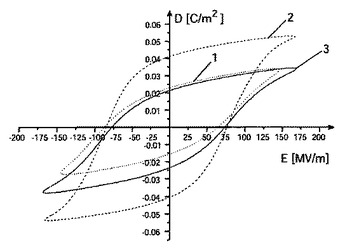

機能的中間層を持つ有機電子回路とその製法

特に高温での性能が改善された有機電子回路(C)であって、第1の電極(1a)と第2の電極(1b)との間に形成される有機エレクトレットまたは強誘電材料(2)で構成する。コンデンサ状の構造を持つセルが有機エレクトレットまたは強誘電材料(2)内に定義され、電極を介して直接または間接に電気的にアクセス可能である。少なくとも1つの機能的中間層(3a,3b)が電極(1a,1b)の1つと有機エレクトレットまたは強誘電材料(2)との間に形成される。中間層材料は一般に無機で、非導電で、有機エレクトレットまたは強誘電材料(2)に対して実質的に不活性である。一般に、中間層(3)は有機エレクトレットまたは強誘電材料(2)に対して、特に後者がフッ素を含む材料のとき、不活性である。マトリクス・アドレス可能なアレイを形成するために複数の回路(C)を用いる。中間層は、個別の中間層分子を解離せずに機能的中間層材料のソースから分子種として堆積される。  (もっと読む)

(もっと読む)

ポリマーメモリ装置の金属窒化物電極及び金属酸化物電極内への電子トラップ生成

本発明の一実施形態は、ポリマー強誘電体メモリ装置のポリマー強誘電体層に引き起こされるダメージを、金属電極とポリマー強誘電体層との間の絶縁性の金属窒化物及び/又は金属酸化物層に過剰正孔を生成することによって低減する。交流バイアスの下で金属電極から注入される電子はポリマー強誘電体層にダメージを与えるものであるが、金属窒化物及び/又は金属酸化物における過剰正孔がこのような電子をトラップする。 (もっと読む)

有機電子デバイスとこの種のデバイスの製造方法

有機電子デバイスは、電極の間に挟まれた1種又は複数の電気活性有機又は高分子材料からなる。このようなデバイスにおいて重要であるのは、電極と高分子との間のインターフェースであり、そこでは、デバイスの正常な機能にとって有害な劣化又は化学反応生成物が生成し得る。これは、直接結合しているか或いは側鎖を通して結合しているホスホネート又はホスフェート官能基を有する分子骨格からなる材料の1種又は複数からなる機能性中間層を導入することによって解決され、前記の機能性の層は、デバイスにおけるそれぞれの電極の少なくとも1つと前記の1種又は複数の電気活性材料との間に配置される。  (もっと読む)

(もっと読む)

強誘電性ポリマー層のパターニング方法

感光性架橋剤を含んでなる強誘電性スピンコーティング溶液から基材上に強誘電性ポリマーの層をスピンコーティングした後、強誘電性ポリマー層をマスクを通して照射し、強誘電性ポリマー層の非露光部分を除去することにより、例えば二フッ化ビニリデン(VDF)およびトリフルオロエチレン(TrFE)のコポリマーのような強誘電性ポリマーがパターニングされることができる。  (もっと読む)

(もっと読む)

縦型強誘電体キャパシタの形成方法

縦構造を持つ強誘電体キャパシタが、絶縁層(31)上に強誘電体層(33)が堆積されるプロセスによって形成される。第1のエッチング工程では、上記強誘電体材料がエッチングされて、その内部に開口部(35)が形成される。このとき、上記絶縁層は実質的にそのままにしておく。次に、上記強誘電体層内に形成された上記開口部内に、導電性の層(39)が堆積されて、上記開口部の側面に電極が形成される。さらにエッチングが行われて、上記Al2O3層(31)内にギャップが形成されて、その下にある導電性素子(3)と接触させる。従って、第2のエッチング工程が行われる時点までには、既に電極が上記強誘電体材料の側面を覆っていて、その間に絶縁フェンスは形成されない。  (もっと読む)

(もっと読む)

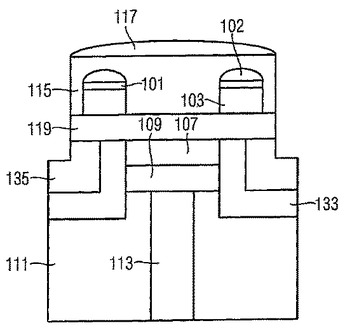

FeRAMキャパシタの製造方法及び該方法により作成されたFeRAMキャパシタ

強誘電体デバイスは底部電極119を含んでいる。底部電極119の上には強誘電体キャパシタ素子103が形成され、この強誘電体キャパシタ素子103の上に頂部電極101が形成されている。底部電極119は、導電性プラグ113を介して、該デバイスの下側層に接続されている。そして、プラグ113と底部電極119とは、Ir及び/又はIrO2からなるバリア素子107、109によって離間させられている。両バリア素子107、109は、底部電極119よりも狭く、個別のエッチング処理により形成される。これは、底部電極119のエッチング時にはIrの囲いが形成されないということを意味する。また、Ir及び/又はIrO2が、底部電極119を介して強誘電体キャパシタ素子に拡散することはほとんどない。それゆえ、強誘電体材料に損傷が生じる危険性はほとんどない。  (もっと読む)

(もっと読む)

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

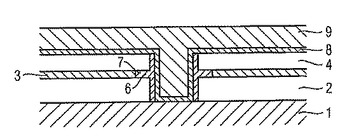

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

トリス(オクタン−2,4−ジオナト)イリジウム、これを含有してなる化学気相成長用原料及び薄膜の製造方法

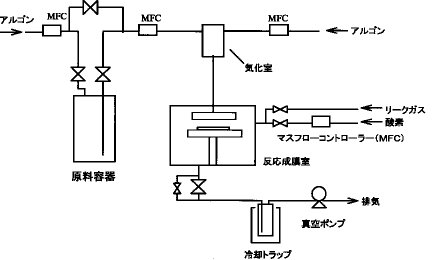

【課題】 CVD法に適する液体イリジウム化合物、これを用いたCVD用原料、及び該CVD用原料を用いたイリジウム薄膜の製造方法を提供すること。

【解決手段】 トリス(オクタン−2,4−ジオナト)イリジウム。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

有機タンタル化合物及びこれを含む有機金属化学蒸着用原料並びにこれから作られるタンタル含有薄膜

【課題】 MOCVD法に適した有機タンタル化合物及びこれを用いて形成される高誘電体薄膜又は強誘電体薄膜として優れたタンタル含有薄膜を得る。均一で安定した気化が行われ、高い成膜速度で高純度の所望のSBT薄膜が得られる。

【解決手段】 次の一般式(2)で示される有機金属化学蒸着用の有機タンタル化合物単体からなるか、又は前記有機タンタル化合物を有機溶媒に溶解してなる有機金属化学蒸着用原料である。

【化9】

有機溶媒としては炭素数4〜10の直鎖状、分岐状又は環状の有機化合物が挙げられる。

(もっと読む)

341 - 352 / 352

[ Back to top ]