Fターム[5F083GA25]の内容

Fターム[5F083GA25]に分類される特許

581 - 600 / 686

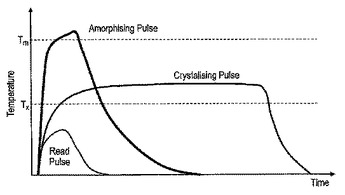

相変化メモリ材料、デバイスおよび方法

Gaと、ランタノイドと、カルコゲニドとからなる化合物に基づく新しい種類の相変化材料を発見した。これにはGaとLaとSからなる化合物(GLS)に加えて、SをO、Se、および/またはTeによって置換した関連化合物が含まれる。またLaを他のランタン系列元素によって置換できる。この種類の材料は低エネルギで切換えられることが実証された。たとえばGLS材料によって、相変化メモリとして標準的なGeSbTe(GST)材料の消去性よりも3〜5dB高い消去性を有する光記録媒体を提供できる。  (もっと読む)

(もっと読む)

EEPROM及びその製造方法

【課題】EEPROM及びその製造方法を提供する。

【解決手段】メモリトランジスタ領域及び選択トランジスタ領域を含む半導体基板の所定領域に活性領域を定義する素子分離膜パターンを形成し、活性領域上にトンネル領域を有するゲート絶縁膜を形成し、ゲート絶縁膜が形成された結果物上に第1導電膜を形成した後、第1導電膜をパターニングして素子分離膜パターンの上部面を露出させる開口部を形成する段階を含む。この時、開口部とこれに隣接する活性領域との間の距離を選択された開口部の下の素子分離膜パターンの幅によって変えるように形成する。

(もっと読む)

強誘電体メモリ、及び強誘電体メモリの製造方法

【課題】金属配線と層間絶縁膜との接触による水素の発生を防止することで、強誘電体キャパシタの劣化を防止した、強誘電体メモリ、及び該強誘電体メモリの製造方法を提供する。

【解決手段】下部電極8及び上部電極10とこれら一対の電極間に挟持された強誘電体層9とからなる強誘電体キャパシタ2と、層間絶縁膜25,14中に設けられる金属配線33とを備えた強誘電体メモリ1である。金属配線33は、層間絶縁膜25,14に接する部位が拡散防止膜30によって覆われている。また、拡散防止膜30は、水素バリア性を有する水素バリア膜としての機能も備えている。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜上に平坦なバリア膜を形成する場合であっても、導体プラグを良好に形成し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上及び強誘電体キャパシタ42上に第1の絶縁膜48を形成する工程と、第1の配線56a〜56cを形成する工程と、第2の絶縁膜60を形成する工程と、第2の絶縁膜の表面を平坦化する工程と、熱処理炉を用いて熱処理を行うことにより第2の絶縁膜中から水分を除去する工程と、N2Oガス又はN2ガスを用いて生成されたプラズマ雰囲気中にて熱処理を行うことにより、第2の絶縁膜中から水分を除去するとともに第2の絶縁膜の表面を窒化する工程と、第2の絶縁膜上にバリア膜62を形成する工程と、バリア膜及び第2の絶縁膜にコンタクトホール68を形成する工程と、コンタクトホール内に導体プラグ70を埋め込む工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置に使用されるキャパシタにおいて酸素透過性の低いアルミナやアルミネート膜を誘電体として使用した場合には、誘電体膜と下部電極の多結晶シリコンとの界面が改質されないでリーク電流が発生するという問題がある。

【解決手段】下部電極の多結晶シリコンへの不純物の導入と、窒化シリコン膜の形成を連続して行う。窒化シリコン膜を酸化処理し、ALD法によりアルミナ膜を形成する。アルミナの形成前に酸化処理し窒化シリコン膜を改質することで、キャパシタのリーク電流を抑制するとともに、さらに形成されるアルミナ膜質が向上する。誘電体膜質が向上することで、大きな容量値を有する、信頼性の高いキャパシタを備えた半導体装置が得られる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】フローティングゲート間の容量を低減して、選択されたメモリセルのしきい値電圧が変動することを抑制すると共に、空隙部の両端部を閉塞することにより、空隙部内に洗浄液等が浸入することを抑制することができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】メモリセル領域RMCと、周辺回路領域RTとを有する不揮発性半導体記憶装置100であって、半導体基板1と、第1絶縁膜を介して形成された第1および第2フローティングゲートFGと、第2絶縁膜を介して形成された第1および第2コントロールゲートCGと、第1コントロールゲートCG上に形成された第3絶縁膜と、第2コントロールゲートCG上に形成された第4絶縁膜と、第1フローティングゲートFGと第2フローティングゲートFGとの間に形成された空隙部GAと、第1および第2コントロールゲートCGの端部側にて、空隙部を閉塞する第5絶縁膜とを備える。

(もっと読む)

強誘電体メモリの製造方法

【課題】強誘電体層の劣化防止とトランジスタへの水素シンター処理による効果とを両立させることのできる、強誘電体メモリの製造方法を提供する。

【解決手段】半導体基板4に駆動トランジスタ3を形成する工程と、駆動トランジスタ3を覆って半導体基板4上に第1層間絶縁膜6を形成する工程と、第1層間絶縁膜6上に第1水素バリア膜7を形成する工程と、第1水素バリア膜7上に、駆動トランジスタ3に電気的に接続する強誘電体キャパシタ2を形成する工程と、を備えた強誘電体メモリ1の製造方法である。駆動トランジスタ3を形成する工程と第1水素バリア膜7を形成する工程との間に、水素シンター処理を行う工程を有している。

(もっと読む)

メモリ

【課題】メモリセルから読み出される信号の強度を向上させることが可能なメモリを提供する。

【解決手段】このメモリは、第1電極膜と、第1電極膜上に形成され、記憶部と、記憶部の厚みよりも小さく、かつ、平均値で記憶部の厚みの15%以上の厚みを有する薄膜部とを有する記憶材料膜と、記憶材料膜の記憶部上に形成された第2電極膜と、第1電極膜、記憶材料膜および第2電極膜を有する単純マトリックス型の複数のメモリセルを含むメモリセルアレイ領域と、平面的に見てメモリセルアレイ領域とは異なる領域に形成され、トランジスタを含む周辺回路領域と、メモリセルアレイ領域のメモリセルが形成される領域の実質的に全面を覆うように形成されるとともに、トランジスタを含む周辺回路領域には形成されない水素の拡散を抑制する絶縁膜とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】金属不純物捕獲能力の向上を図ることができ、且つ、素子分離構造のエッチングによる形状変化(片落ち)を抑制する。

【解決手段】シリコン酸化膜よりなる素子分離構造2が形成されたシリコン基板1上に、熱燐酸によりウェットエッチングに対するエッチング選択比が素子分離構造2に比較して高いシリコン窒化膜3を金属不純物捕獲膜として形成する。イオン注入後、熱燐酸によりウェットエッチングによりシリコン窒化膜3を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】下部水素バリア膜を形成して上部水素バリア膜とで形成される密閉構造内に密封した強誘電体キャパシタの強誘電体の分極特性の劣化を防止すると共に、強誘電体キャパシタの総電荷量を確保する手段を提供する。

【解決手段】半導体装置が、拡散層を有するMOSFETと、MOSFETを覆う層間絶縁膜と、層間絶縁膜上に形成した下部水素バリア膜と、下部水素バリア膜上に形成したシリコン酸化膜と、層間絶縁膜と下部水素バリア膜とシリコン酸化膜とを貫通し、MOSFETの一方の拡散層に電気的に接続するコンタクトプラグと、シリコン酸化膜上に形成され、コンタクトプラグに電気的に接続する下部電極と、この下部電極上に強誘電体と上部電極とを順に積層して形成した強誘電体キャパシタと、強誘電体キャパシタおよびシリコン酸化膜を覆い、下部水素バリア膜に接続する上部水素バリア膜とを備える。

(もっと読む)

半導体装置

【課題】素子が微細化された場合においても、強誘電体キャパシタの特性劣化を抑制し、あるいは、その特性を向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の上方に設けられた強誘電体キャパシタと、強誘電体キャパシタの側面を被覆する絶縁性の保護膜と、保護膜を介して強誘電体キャパシタの側面に設けられ、強誘電体キャパシタにかかる電界方向へ該強誘電体キャパシタに引張応力を与える側壁膜とを備え、側壁膜はシリコン窒化膜からなる。

(もっと読む)

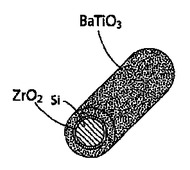

ナノスケールワイヤベースのデータ格納装置

本発明は、ナノテクノロジーおよび回路網において使用され得るサブマイクロ電子デバイスに関し、一部の場合において、ナノスケールワイヤおよびデータを符号化することが可能なナノ構造に関する。本発明の一局面は、ナノスケールワイヤまたは電気的に分極可能な領域を有する他のナノ構造を提供する。一部の場合において、電気的に分極可能な領域は、外部に電界が存在しなくても、分極状態を維持することが可能である。電気的に分極可能な領域の全てまたは一部分のみが、例えば1ビット以上のデータを符号化するために分極され得る。実施形態の1つのセットにおいて、電気的に分極可能な領域は、機能性酸化物、または強誘電率の酸化材料を含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110(プラグを構成する導電物は例えばタングステン(W))との間に、シリサイド膜111を形成する。ここでは、導電プラグ110の下地膜をシリサイド膜111とする場合を例示する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】多層配線にダマシン構造を採用しながら、強誘電体キャパシタのチャージングダメージを抑制し、良好な強誘電体特性を実現して素子特性の向上をはかる。

【解決手段】半導体基板100上に、強誘電体膜112を下部電極111と上部電極113で挟んで形成された強誘電体キャパシタ12とスイッチング用トランジスタ11からなるメモリセルを、有する半導体記憶装置であって、強誘電体キャパシタ12の上部電極113に接続される第1配線121aは、配線材料を堆積後に加工することにより形成され、且つ第1配線121a上にダマシンプロセスによる第2配線124aが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 不揮発性メモリ素子のデトラップ・リテンション特性の劣化を防止することができる技術を提供する。

【解決手段】 プラグ16を形成した絶縁膜14上にシリコンリッチな酸化膜よりなる層間絶縁膜17およびTEOS膜よりなる層間絶縁膜18を形成する。そして、層間絶縁膜17および層間絶縁膜18を貫通する溝19を設け、この溝19内へ埋め込むように配線20aを形成する。すなわち、第1配線層を層間絶縁膜17および層間絶縁膜18に埋め込んだ埋め込み配線とする。さらに、第1配線層を構成する配線20a〜20cと同層の層間絶縁膜17として水や水素などの不純物を捕獲する性質を有するシリコンリッチな酸化膜とする。

(もっと読む)

半導体装置

【課題】 強誘電体層の還元を効果的に防止することができ、絶縁性および強誘電体特性に優れた強誘電体層を有する半導体装置を提供する。

【解決手段】 半導体装置100は、基板10と、基板10の上方に設けられた第1電極32と、第1電極32の上方に設けられた強誘電体層34と、強誘電体層34の上方に設けられた第2電極36と、第1電極32の上方に設けられ、かつ、少なくとも強誘電体層34の側面に設けられた絶縁性のサイドスペーサ14と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の低抵抗化とトランジスタの特性安定化を両立させる半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板と、前記半導体基板上に第1の絶縁膜を介して形成された電荷蓄積層と、前記電荷蓄積層上に第2の絶縁膜を介して形成された導電体層とを含む複数のゲート電極と、前記導電体層上部に設けられた第2の導電体層と、前記ゲート電極間に設けられ、前記ゲート電極とは側面のみで接するバリア絶縁膜と、前記第2の導電体層の上面に接して設けられた層間絶縁膜と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】 還元性雰囲気からキャパシタ誘電体膜を効果的に保護できる半導体装置の製造方法を提供すること。

【解決手段】 シリコン基板1上に第1絶縁膜11を形成する工程と、第1絶縁膜11上に、下部電極15a、強誘電体材料で構成されるキャパシタ誘電体膜16a、及び上部電極17aを順に積層してなるキャパシタQを形成する工程と、キャパシタQと第1絶縁膜11とを覆う第1キャパシタ保護絶縁膜19として、触媒CVD法により窒化シリコン膜を形成する工程と、第1キャパシタ保護絶縁膜19の上に第2絶縁膜20を形成する工程と、を有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 チタンを含む金属膜のドライエッチにフッ素系ガスを使用する際に形成される側壁を除去する際に析出異物が生成されることがなく、短絡不良の発生を確実に防止することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 半導体基板上に形成されたチタンを含む金属膜17上にエッチングマスク23を形成し、エッチングマスク23を介して、金属膜17をドライエッチングする。当該ドライエッチング後に、エッチングマスク23を除去し、金属膜17の表面に水分子の透過を阻害する防水膜32を形成する。そして、前記ドライエッチングの過程でエッチング部位18の内側面に形成された反応生成物からなる側壁31の、金属膜17の上面より上方に突出する突出部を、フッ素元素を含むガスを用いたプラズマ処理により行うこと除去する。

(もっと読む)

強誘電体メモリ及びその製造方法

【課題】 本発明の目的は、微細化及び高密度化に対応し、かつ製造プロセスの容易化を図ることのできる、強誘電体メモリ及びその製造方法を提供することにある。

【解決手段】 強誘電体メモリは、基板10と、基板10の上方に形成された少なくとも1層よりなる層間絶縁層30,34と、層間絶縁層30,34の上方に形成された複数の強誘電体キャパシタC11,C22と、複数の強誘電体キャパシタC11,C22を被覆する被覆層70と、複数の強誘電体キャパシタC11,C22の間に設けられた第1の開口部72と、第1の開口部72と連通するとともに被覆層70及び層間絶縁層34に形成された第2の開口部74と、第1及び第2の開口部72,74内に一体的に設けられた導電層82と、を含む。

(もっと読む)

581 - 600 / 686

[ Back to top ]