Fターム[5F083HA07]の内容

Fターム[5F083HA07]に分類される特許

1 - 20 / 120

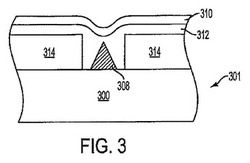

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

不揮発性メモリ装置

【課題】 パストランジスタ間の空間確保が可能な不揮発性メモリ装置を提供する

【解決手段】 不揮発性メモリ装置100が備える行デコーダ120は、パストランジスタ部123_L、123_Rを含む。パストランジスタ部123_L、123_Rは、メモリブロック110の左右に配列される。ブロック選択信号BLKWL1によって共通ゲートを形成するパストランジスタ端Pass TR 0とパストランジスタ端Pass TR 8とは、選択的に活性化される第1駆動信号ラインSI1及び第2駆動信号ラインSI2によって独立して駆動される。互に異なるブロック選択信号BLKWLによって駆動されるパストランジスタは、1つの活性領域の上に形成され得る。これにより、1つの活性領域の上に2つのパストランジスタを形成する場合、パストランジスタ部123_L、123_Rのチャンネル方向の大きさを減らすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

不揮発性半導体メモリ

【課題】新たなコンセプトに基づく不揮発性半導体メモリを提供する。

【解決手段】本開示の不揮発性半導体メモリは、半導体基板11上の半導体層12と、半導体層12を貫通する複数のコントロールゲートCG11〜CG17と、第1方向の2つの端部における半導体層12内にそれぞれ配置される2つの第1導電型拡散層14と、半導体層12上で第1方向に延びる複数のセレクトゲート線SG1〜SG5と、複数のセレクトゲート線SG1〜SG5上で第2方向に延びる複数のワード線WL1〜WL7とを備える。複数のセレクトゲート線SG1〜SG5の各々は、第1方向に並ぶ複数のコントロールゲートCG11〜CG17と複数のワード線WL1〜WL7との間に接続される複数のセレクトトランジスタに共有されるセレクトゲートとして機能する。半導体層12及び複数のコントロールゲートCG11〜CG17は、メモリセルアレイを構成する。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】共通ゲートを有する複数のトランジスタセルをアレー状に配置する構成を持つ不揮発性半導体集積回路装置において、STI領域のパターニング工程でのパターンの変形を防ぐ製造方法を提供する。

【解決手段】半導体メモリ等のメモリセルアレー等の露光において、矩形形状のSTI溝領域エッチング用単位開口を行列状に配置したSTI溝領域エッチング用単位開口群をネガ型レジスト膜28上に露光するに際して、列方向に延びる第1の線状開口群を有する第1の光学マスクを用いた第1の露光ステップと、行方向に延びる第2の線状開口群を有する第2の光学マスクを用いた第2の露光ステップとを含む多重露光を適用する。直行する2方向において、それぞれの方向に対してマスクを用いて露光を行うことで、矩形形状48の端部における近接効果を回避することができ、矩形形状48の端部が丸みを帯びるのを回避することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】半導体基板SUBの表面に、ソース領域SOおよびドレイン領域DRを有する高耐圧横型MOSトランジスタが完成される。そのトランジスタを平面視において取り囲む溝DTRが半導体基板SUBの表面に形成される。そのトランジスタ上を覆うように、かつ溝DTR内に中空SPを形成するようにトランジスタ上および溝DTR内に絶縁膜IIAが形成される。層間絶縁膜IIにトランジスタのソース領域SOおよびドレイン領域DRの各々に達するコンタクトホールCHが形成される。

(もっと読む)

電荷を非対称に捕獲する多値メモリセル

【課題】高メモリ密度、低電力消費、及び高信頼性を達成可能なNAND型多値メモリセルを提供する。

【解決手段】NAND型多値メモリセルは、2つのドレイン/ソース領域を基板に有する。2つのドレイン/ソース領域の間における基板の上方には、酸化物−窒化物−酸化物構造体が形成される。このうち窒化物層は、電荷を非対称に捕獲する層として機能する。酸化物−窒化物−酸化物構造体の上方には、制御ゲートが配置される。ドレイン/ソース領域に非対称のバイアスをかけることで、ドレイン/ソース領域に高い電圧が生じ、これによってドレイン/ソース領域の略近傍における電荷捕獲層にGIDL(ゲートに起因するドレインでの電流漏れ)正孔注入処理を行い、正孔を非対称な分布で注入する。

(もっと読む)

犠牲材を使用してダマシンダイオードを作る方法

半導体デバイスを作る方法は、下位層の上にシード材を備える第1の層を形成することと、シード材とは異なる犠牲材を備える第2の層を第1の層の上に形成することと、第1の層および第2の層を複数の分離したフィーチャとなるようにパターニングすることと、複数の分離したフィーチャの間に絶縁充填材を形成することと、絶縁充填材の中に複数の開口部を形成して、複数の開口部の中でシード材を露出させるため、分離したフィーチャから犠牲材を除去することと、複数の開口部の中で露出されたシード材の上に半導体材を成長させることと、を含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】第1導電型の半導体層とトンネルウィンドウが対向する第2導電型の不純物拡散領域との高い接合耐圧を得ることができる、半導体装置を提供する。

【解決手段】各メモリセルにおいて、半導体基板2の表層部には、N型の第1不純物拡散領域3が形成されている。また、半導体基板2の表層部には、第1不純物拡散領域3に対して所定方向の一方側に、第1不純物拡散領域3と間隔を空けて、N型の第2不純物拡散領域4が形成されている。半導体基板2上には、第1絶縁膜6が形成されている。第1絶縁膜6には、第1厚膜部8が形成されており、第2不純物拡散領域4の全周縁は、第1厚膜部8の直下に位置している。

(もっと読む)

離間された導電配線に電気的接続を提供する方法

集積回路及び形成方法は、少なくとも1つの直線的に延在する導電配線の斜端に形成されたコンタクト領域を提供する。実施形態では、コンタクトランディングパッドを有する導電配線は、マスク材料に配線をパターン化することと、材料配線の延在方向に対して角度を形成するために少なくとも1つの材料配線を切断することと、マスク材料の斜端面から拡張部を形成することと、前記材料配線及び拡張部をマスクとして用いてエッチングすることによって基本的な半導体をパターン化することとによって形成される。他の実施形態では、少なくとも1つの導電配線は、斜端面を作るように導電配線の延在方向に対して角度を付けて切断されるとともに、電気的コンタクトランディングパッドは、斜端面にコンタクトして形成される。 (もっと読む)

半導体記憶装置

【課題】モリセルトランジスタ素子以外の周辺回路の特性を低減させることなく、書込み特性の劣化を抑制した半導体記憶装置を提供すること。

【解決手段】ホットエレクトロン注入による書込み方式の半導体記憶装置101において、例えば、P+半導体基板10と、P+半導体基板10上に形成されるP−エピ層(半導体層)であって、P+半導体基板10よりも高い抵抗を持つP−エピ層11(半導体層)と、P−エピ層11に形成されたメモリセルトランジスタ素子20と、メモリセルトランジスタ素子20の下方のP−エピ層11内に、底部がP+半導体基板10に到達する深さで形成されたP+不純物拡散領域12であって、P−エピ層11よりも低い抵抗を持つP+不純物拡散領域12と、を備える半導体記憶装置である。

(もっと読む)

非プレーナ型トランジスタを用いた半導体装置および製造方法

【課題】より速い駆動電流およびより小さな短チャネル効果を備え、微細化されたスタティック・ランダム・アクセス・メモリ・セルを提供する。

【解決手段】スタティック・ランダム・アクセス・メモリ・セル300は、半導体基板上の1つ以上のフィンを備える2つの非プレーナ型パスゲート・トランジスタを備える。2つの非プレーナ型プルアップ・トランジスタは、半導体基板上の1つ以上のフィンを備える。2つの非プレーナ型プルダウン・トランジスタは、半導体基板上の1つ以上のフィンを備える。半導体基板上の2つのアシスト・バー314、316は、非プレーナ型プルアップ・トランジスタのフィンの一部と非プレーナ型プルダウン・トランジスタのフィンの一部とを電気的に接続する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

マルチドットフラッシュメモリ及びその製造方法

【課題】マルチドットフラッシメモリの新しいセルアレイアーキテクチャーを提案する。

【解決手段】本発明の例に係わるマルチドットフラッシュメモリは、半導体基板に平行な第一方向に並んで配置され、第一方向に交差する半導体基板に平行な第二方向に延びるアクティブエリアAAと、アクティブエリアAA上に配置され、第一方向に並んで配置されるフローティングゲートFGと、フローティングゲートFG上に配置され、第一方向に延びるワード線WLと、フローティングゲートFG間に配置され、第二方向に延びるビット線BLs、BLrとを備える。フローティングゲートFGの各々は、第一方向の二つの側面の形状が異なり、かつ、第一方向に隣接する二つのフローティングゲートFGは、互いに対向する二つの側面の形状が対称的である。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】不揮発性メモリ素子及びその製造方法が提供される。本発明の不揮発性メモリ素子は、基板と、互いに対向するように垂直伸張する第1部及び第2部と、前記第1部及び第2部を連結する底部とを前記基板上に含む半導体構造物と、前記半導体構造物の前記第1部及び第2部に沿って離隔配置されて互いに直列に連結された複数のメモリセルと、を含む。本発明の不揮発性メモリ素子の製造方法は、互いに対向するように垂直伸張する第1部及び第2部と、前記第1部及び第2部を連結する底部と、を基板上に含む半導体構造物を前記基板上に形成する段階と、前記半導体構造物の前記第1部及び第2部に沿って離隔配置され、互いに直列に連結された複数のメモリセルを形成する段階と、を含む。

(もっと読む)

半導体装置の製造方法およびフォトマスク

【課題】極微細なパターンを有するSRAM領域のフィンと周辺回路領域の活性領域とを低コストかつ正確なデザインで形成することのできる半導体装置の製造方法、およびその製造方法に用いられるフォトマスクを提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、第1および第2の領域を有する半導体基板上にマスク材を形成する工程と、前記第1の領域の前記マスク材上に芯材をパターン形成する工程と、前記芯材の両側面に側壁マスクを形成した後、前記芯材を除去する工程と、前記芯材を除去した後、前記第1の領域の前記マスク材に前記側壁マスクのパターンを転写する工程と、前記第1の領域の前記側壁マスクのパターンを転写された前記マスク材のトリミングと、前記第2の領域の前記マスク材への所定のパターンの形成とを同時に行う工程と、を含む。

(もっと読む)

1 - 20 / 120

[ Back to top ]