Fターム[5F083JA51]の内容

半導体メモリ (164,393) | 材料 (39,186) | 電極材料、配線材料、バリア材料 (24,756) | 化合物半導体(III−V族,II−VI族) (27)

Fターム[5F083JA51]に分類される特許

1 - 20 / 27

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

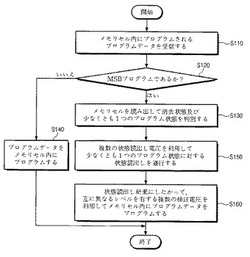

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

光不揮発性メモリ

【課題】光信号を直接不揮発的に記憶する光不揮発性メモリを提供すること。

【解決手段】第1導電型を有する第1半導体層12と、前記第1導電型とは異なる第2導電型を有する第2半導体層16と、前記第1半導体層と前記第2半導体層とに挟まれ、逆バイアスが印加されることにより受光し、順バイアスが印加されることにより発光する活性層14と、前記活性層の受光する光の強さによって磁化方向が変化する強磁性体層20と、を具備する光不揮発性メモリ。

(もっと読む)

半導体装置の製造方法

【課題】複数のサポート膜間における開口の位置ずれ発生を抑制できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に、第1の犠牲膜、第1のサポート膜、第2の犠牲膜及び第2のサポート膜を順次形成し、これらの膜を貫通するホールを形成し、ホールの内表面を覆い、かつ第2のサポート膜及び第1のサポート膜に接続される王冠型電極を形成し、王冠型電極と第2のサポート膜との接続を少なくとも一部分維持する第1のパターンで、第2のサポート膜に第1の開口を形成し、第1の開口を通じて第2の犠牲膜の一部又は全部を除去し、第1の開口を利用して第1のサポート膜に第2の開口を形成し、第2の開口を通じて第1の犠牲膜を全て除去する、ことを特徴とする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】半導体記憶装置におけるトランジスタの特性向上と、キャパシタのリーク電流特性の両方を改善し、高信頼、高歩留のデバイスを提供する。

【解決手段】窒化チタンからなる下部電極102上に酸化ジルコニウムを主成分とする誘電体膜103を有するキャパシタにおいて、微結晶状態の酸化ジルコニウムを主成分とする誘電体膜を成膜し、2次的な結晶粒成長を伴わない条件でチタン化合物を主成分とする第一の保護膜110を形成し、その後、上部電極111を形成することで、上部電極形成時に伴う熱処理を行っても、またトランジスタの界面準位を低減する水素アニールを行っても、リーク電流の増大を抑制できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ソース線と、ビット線と、信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセル1100と、ソース線及びビット線とスイッチング素子を介して電気的に接続された第1の駆動回路1111と、ソース線とスイッチング素子を介して電気的に接続された第2の駆動回路1112と、信号線と電気的に接続された第3の駆動回路1113と、ワード線と電気的に接続された第4の駆動回路1114と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含む。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース−ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース−ビット線の間に接続されたメモリセルと、を有し、メモリセルは、第1のトランジスタと、第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含んで構成され、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方と、容量素子の電極の一方とは、電気的に接続され、ソース−ビット線と、第1のトランジスタのソース電極とは、電気的に接続され、該ソース−ビット線と隣り合うソース−ビット線と、第1のトランジスタのドレイン電極とは、電気的に接続された半導体装置。

(もっと読む)

抵抗変化メモリ

【課題】p-i-nダイオードをその特性の劣化なしに薄くする。

【解決手段】本発明の例に係わる抵抗変化メモリは、第一方向に延びる第一導電線L2(i)と、第一方向に交差する第二方向に延びる第二導電線L3(j)と、第一導電線と第二導電線との間に直列接続されるメモリ素子17及び整流素子13,14,15から構成されるセルユニットCU2とを備える。メモリ素子の抵抗値は、メモリ素子に印加される電圧を制御することにより、少なくとも第一値と第二値との間で可逆変化させる。整流素子は、p型半導体層、n型半導体層及びこれらの間の真性半導体層から構成されるp-i-nダイオードである。p-i-nダイオードは、少なくともp型半導体層の真性半導体層側の端部及びn型半導体層の真性半導体層側の端部に拡散防止領域を有する。

(もっと読む)

メモリデバイス、トランジスタデバイスおよび関連する方法

メモリデバイスならびにメモリデバイスを製造する方法。メモリデバイスは基板表面におけるストレージトランジスタを含む。ストレージトランジスタは、第一および第二のソース/ドレイン領域間のボディ部分を含み、ソース/ドレイン領域は第一の導電型の領域である。ストレージトランジスタは、少なくとも二つの平面でボディ部分を少なくとも部分的に包囲するゲート構造をも含む。ビット線は第一のソース/ドレイン領域に接続され、ワード線はゲート構造に接続される。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】高耐圧トランジスタのオフ時のリーク電流を抑制し、周辺回路内部の電圧を安定化することが可能な、NAND型フラッシュメモリ等に適用される半導体記憶装置を提供する。

【解決手段】周辺回路領域PRにおいて、シリコン基板11の一部にシリコンよりバンドギャップの広いSiCやGaN等の半導体層14が形成されている。メモリセル13は、シリコン基板11内に形成されている。周辺回路を構成するトランジスタ15は半導体層14内に形成されている。半導体層14のバンドギャップは、シリコンのバンドギャップより広いため、トランジスタ15がオフ状態において、トンネル電子が発生しない。このため、GIDLの発生を抑制することができる。

(もっと読む)

円偏光発光性ナノ微粒子

【課題】円偏光発光特性を示す化合物半導体ナノ微粒子を提供する。

【解決手段】籠状タンパク質であるフェリチンのコア内で調整したCdSが高い円偏光発光(CPL)を示す。また、この円偏光発光(CPL)の波長は、レーザ照射により調整することができ、これによりバイオナノテクノロジー分野における化合物半導体のナノ微粒子の利用として、WORM(Write-Once Read-Many times)メモリの創成など利用可能となる。なお、籠状タンパク質は、空洞が形成されたタンパク質であり、アポフェリチンなどのフェリチンタンパク質ファミリーやその組み換え体を用いることができる。

(もっと読む)

シリコン−ゲルマニウムナノワイヤ構造およびその形成方法

【解決手段】 支持基板上に配設されるシリコン−ゲルマニウムナノワイヤ構造が提供される。当該シリコンゲルマニウムナノワイヤ構造は、支持基板上に配設されている少なくとも1つのゲルマニウム含有支持部と、支持基板の上方に設けられており、少なくとも1つのゲルマニウム含有支持部に隣接して配設されている少なくとも1つのゲルマニウム含有ナノワイヤとを備え、少なくとも1つのゲルマニウム含有ナノワイヤは、ゲルマニウム濃度が少なくとも1つのゲルマニウム含有支持部よりも高い。さらに、支持基板上に配設されているシリコン−ゲルマニウムナノワイヤ構造を備えるトランジスタが提供される。さらに、支持基板上に配設されているシリコン−ゲルマニウムナノワイヤ構造を形成する方法、および、支持基板上に配設されているシリコン−ゲルマニウムナノワイヤ構造を形成する方法を備えるトランジスタを形成する方法が提供される。 (もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、メモリセルを3次元的に積層した構造であって、製造コストを抑えた不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置10は、電気的に書き換え可能な複数のメモリセルが直列に接続された複数のメモリストリングスMSを有する。メモリストリングスMSは、基板Baに対して垂直方向に延びる柱状半導体CLmnと、柱状半導体CLmnに接し且つ電荷を蓄積するトラップ膜(電荷蓄積層)21と、トラップ膜21に接するブロック絶縁膜22と、ブロック絶縁膜22と接するワード線WLとを備える。トラップ膜21は、シリコン窒化膜(SiN)である。

(もっと読む)

半導体集積回路構造を形成する方法

【課題】所定面積に対して一層大きいキャパシタ容量を得る。

【解決手段】全般的に云うと、この発明は電子サイクロトロン共鳴(ECR)の様な乾式プラズマ・エッチング方法を利用して、DRAM記憶セルに勾配つき側壁を作る。この方法によって作られた下側電極の丸くした角により、高級誘電体材料を実質的なひび割れなしにデポジットすることができ、更に、この高級誘電体層を作る時の一様性により、静電容量を厳密に予測し、且つ制御することができる。この発明の一実施例は、主面を持つ支持層(例えばSi基板30)と、支持層の主面に重なる下側電極と、下側電極の上面に重なる誘電率の高い材料の層(例えばBST 44)とを有する微小電子回路構造を作る方法である。下側電極が障壁層(例えばTiN 36)及び非反応性の層(例えばPt 42)を有する。

(もっと読む)

ナノスケールワイヤ及び関連デバイス

【課題】

ナノテクノロジー、特にナノスケールでのエレクトロニクス用途に適したナノスケールワイヤ及び関連デバイスをを提供することを目的とする。

【解決手段】

少なくとも1012バイト/cm2の密度をもつメモリ素子のアレイを含み、

少なくともひとつのメモリ素子は、自立型バルクドープ半導体を含む物品を含み、該自立型バルクドープ半導体は、500ナノメートル未満の最小幅をもつ少なくとも一つの部分

を含む、

デバイスを使用する。

(もっと読む)

記憶素子

【課題】より長い素子寿命を備えた新たな記憶素子を提供する。

【解決手段】基板101と、基板101の上に形成された支持層102と、支持層102の上に形成された記憶層103とを備えている。記憶層103は、下層の支持層102に接触している領域では、支持層102に対して圧縮歪みを備えて形成されている。例えば、基板101は、GaAsから構成され、支持層102は、基板101の上に結晶成長により形成された単結晶Al0.7Ga0.3Asから構成され、記憶層103は、InxGa1-xAsから構成されていればよい。加えて、記憶層103は、開口領域132を備え、開口領域132の対向する辺の間に、架設された梁構造体131を備えている。また、開口領域132に対応して支持層102にも開口部121が形成され、梁構造体131の基板101側が下層より離間した状態とされている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ゲート電極から電荷蓄積層に正孔を注入する不揮発性メモリにおいて、電荷保持特性を低下させることなく、正孔注入の高効率化を実現する。

【解決手段】電荷蓄積層を構成する窒化シリコン膜920に電子および正孔を注入し、トータルの電荷量を変えることによって書き込み・消去を行う不揮発性メモリにおいて、ゲート電極500からの正孔注入を高効率で行うために、メモリセルのゲート電極500を、不純物濃度が異なる複数のポリシリコン膜の積層構造、例えば低不純物濃度のp型ポリシリコン膜とその上部に堆積した高不純物濃度のp+型ポリシリコン膜とからなる2層膜で構成する。

(もっと読む)

1 - 20 / 27

[ Back to top ]