Fターム[5F083KA17]の内容

Fターム[5F083KA17]の下位に属するFターム

アドレス選択線 (50)

プレート線 (113)

多層化配線(WL、BLを除く) (150)

Fターム[5F083KA17]に分類される特許

41 - 60 / 107

区分データ線を有するメモリシステム

記憶システムは、複数のブロックにグループ分けされた複数層の不揮発性記憶素子群を有する3次元メモリアレイを備える。ブロックは複数のベイにグループ分けされている。

記憶システムは、記憶素子と通信する第1タイプのアレイ線と、記憶素子と通信する第2タイプのアレイ線と、センスアンプを含む。各ブロックは、2個のセンスアンプと地理的に関連付けられており、特定ベイの全ブロックは、その特定ベイのブロックに関連付けられたセンスアンプのグループを共有する。システムは、3次元メモリアレイの下方に位置する1以上のルーティング金属層内のローカルデータ線の複数セットと、3次元メモリアレイの上方に位置する1以上の最上位金属層内のグローバルデータ線の複数セットを含む。1以上のブロックの各セットは、ローカルデータ線の一セットを含む。各ベイは、夫々のベイのブロックに関連付けられたセンスアンプのグループに接続するグローバルデータ線の一セットを含む。各ブロックは、第1タイプのアレイ線のサブセットを夫々のローカルデータ線と選択的にカップリングするための第1選択回路のサブセットを含む。各ブロックは、夫々のローカルデータ線のサブセットを夫々のベイに関連付けられたグローバルデータ線と選択的にカップリングするための第2選択回路のサブセットを含む。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】占有面積を縮小化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、電気的に書き換え可能であり且つ直列に接続されたメモリセルMCを有するメモリセルアレイ層400と、メモリセルアレイ層400の下層に位置し且つメモリセルMCに印加する電圧を制御する制御回路層200と、制御回路層200とメモリセルアレイ層400とを電気的に接続する接続配線部500とを備える。メモリセルアレイ層400は、メモリセルMCを有する第1メモリセル領域40Aと、接続配線部500が設けられた接続領域40Cとを備える。第1メモリセル領域40Aは、ロウ方向に第1のピッチをもって繰り返し形成されている。接続領域40Cは、ロウ方向に隣り合う第1メモリセル領域40Aの間においてカラム方向に第2のピッチをもって繰り返し形成されている。

(もっと読む)

記憶素子及び記憶装置

【課題】圧電素子を用いずに印加された圧力を記憶することができる記憶素子及び記憶装置を提供する。

【解決手段】複数の記憶素子が縦横に並べて配置されている。各記憶素子には、抵抗変化素子を備えた抵抗変化部1、及び印加された圧力に応じて流れる電流が変化する電流変化部2が設けられている。電流変化部2には、定電圧が供給される。抵抗変化部1と電流変化部2との間にはビット線BLが接続され、抵抗変化部1の他端にはトランジスタ3のソース・ドレインの一方が接続されている。トランジスタ3の他方のソース・ドレインは信号線SLに接続され、トランジスタ3のゲートはワード線WLに接続されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】電荷蓄積層の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板11上に、絶縁膜及び電極膜14を交互に積層し、その上にX方向に延びる複数本の選択ゲート電極17及びY方向に延びる複数本のビット線BLを設ける。また、電極膜14及び選択ゲート電極17を貫き、上端部がビット線BLに接続された複数本のシリコンピラー31と、斜め位置にある一対のシリコンピラー31の下端部同士を接続する接続部材32とからなるU字シリコン部材33を設ける。そして、各層の電極膜14を選択ゲート電極17毎に分断し、接続部材32を介して相互に接続された一対のシリコンピラー31に、相互に異なる電極膜14及び相互に異なる選択ゲート電極17を貫かせ、1本のビット線BLに共通接続されたU字シリコン部材33の全てを、他の1本のビット線BLに共通接続させる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】製造が容易な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置1において、シリコン基板11上に積層体ML1、ML2、ML3をこの順に形成する。積層体ML1には下部選択ゲートLSGを設け、積層体ML3には上部選択ゲートUSGを設ける。また、積層体MLにはZ方向に延びる貫通ホール17を形成し、その内部にシリコンピラーSPを埋設する。下部選択ゲートLSGとシリコンピラーSPとの間、及び上部選択ゲートUSGとシリコンピラーSPとの間には、ゲート絶縁膜GDを設ける。そして、このゲート絶縁膜GDを、ボロンを含有したシリコン窒化物により形成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作電圧種が少なく周辺回路の回路規模を小さくできるメモリセルを有する不揮発性半導体記憶装置を提供すること。

【解決手段】半導体基板1のチャネルの両側にソース/ドレイン3を有するとともに、チャネル上に厚ゲート絶縁膜4を介してゲート電極6を有する選択トランジスタ8と、選択トランジスタ8と隣接する領域の半導体基板1上に形成された素子分離領域2と、素子分離領域2に隣接するとともに、半導体基板1上に下部電極27が形成され、素子分離領域2と下部電極27の間の領域の半導体基板1上に薄ゲート絶縁膜5を介して上部電極7を有するアンチフューズ9と、ソース3と上部電極7の間を電気的に接続するとともに、ソース3及び上部電極7と接触する接続コンタクト28と、を備える。

(もっと読む)

半導体装置

【課題】セルサイズのさらなる縮小を図ることができる、半導体装置を提供すること。

【解決手段】半導体層2に、トレンチ5が形成されている。半導体層2の表層部には、第1拡散領域3およびドレイン領域が形成されている。第1拡散領域3は、トレンチ5に対して所定方向の一方側に形成され、トレンチ5に隣接している。第2拡散領域6は、所定方向においてトレンチ5に対して第1拡散領域3と反対側に形成され、トレンチ5に隣接している。トレンチ5の底面および側面上には、第1絶縁膜8が形成されている。第1絶縁膜8上には、フローティングゲート11が設けられている。フローティングゲート11は、第1絶縁膜8を挟んで、トレンチ5の底面および側面と対向している。フローティングゲート11上には、第2絶縁膜12が形成されている。第2絶縁膜12上には、コントロールゲート13が設けられている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】個々のメモリセルの電荷蓄積量が多い不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板11上に、それぞれ複数の絶縁膜12及び電極膜13を交互に積層して積層体14を形成する。次に、積層体14を積層方向に貫通する貫通孔15を形成する。このとき、貫通孔15における電極膜13内に位置する部分の側面15aを、貫通孔15の中心軸15cを含む断面において、貫通孔15の内側から見て凹状に湾曲させる。その後、貫通孔15の側面上に電荷蓄積層26を形成し、貫通孔15の内部に半導体ピラー17を形成する。

(もっと読む)

半導体装置およびその製造方法およびその駆動方法

【課題】サイリスタ動作時に、寄生バイポーラトランジスタを作らせず、書き込みのディスターブの発生を防止して、誤書き込みを防止することを可能にするSRAM型の半導体装置とその製造方法を提供する。

【解決手段】半導体基板11に形成されたサイリスタ形成領域21を分離する素子分離領域12と、サイリスタ形成領域21に形成されていて、p型の第1領域(第1p型領域)p1と、n型の第2領域(第1n型領域)n1と、p型の第3領域(第2p型領域)p2と、n型の第4領域(第2n型領域)n2とが順に接合されたサイリスタT1、T2と、第2p型領域p2の下部に形成されたn型の第5領域(第1ウエル領域)31を有する半導体装置1において、第5領域31の底部および素子分離領域12の下部に接合するp型の第6領域(第2ウエル領域)32を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置において、読み出し速度と消去速度を向上させること。

【解決手段】不揮発性半導体記憶装置は、半導体基板1と、半導体基板1中のチャネル領域CNL上のゲート絶縁膜上に並んで形成された選択ゲートSLG及び浮遊ゲートFGを備える。不揮発性半導体記憶装置は更に、浮遊ゲートFGの上面より下方に位置し、浮遊ゲートFGの下面の端部と対向する消去ゲートEGを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作特性を向上させるNAND型フラッシュメモリ半導体記憶装置、及び、活性領域側壁への不純物打ち込みに関するその製造方法を提供する。

【解決手段】メモリMOSトランジスタが配置される第1活性領域と、周辺MOSトランジスタが配置される第2活性領域と、半導体基板10中に形成され、側壁において第1活性領域が露出される第1トレンチ43と、第1トレンチ43内を埋め込む絶縁膜を備え、隣接する第1活性領域間を電気的に分離する第1素子分離領域と、半導体基板10中に形成され、側壁において第2活性領域が露出される第2トレンチ43と、第2トレンチ43内を埋め込む絶縁膜27を備え、隣接する第2活性領域間を電気的に分離する第2素子分離領域35とを具備し、第2活性領域の不純物濃度は中心部より高く、第1活性領域AAの不純物濃度は中心部と等しい。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安価に高集積化された不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、電気的に書き換え可能な複数のメモリトランジスタが直列に接続された複数のメモリストリングスを有する。メモリストリングスは、半導体基板Baに対して垂直方向に延び且つ上端から下方に延びる中空を有するメモリ柱状半導体層37と、メモリ柱状半導体層37の外壁に接して形成されたトンネル絶縁層36cと、中空に面するメモリ柱状半導体層37の内壁に形成されたメモリホール第1の絶縁層38aと、メモリ柱状半導体層37と共にトンネル絶縁層36cを挟むように形成された第1〜第4ワード線導電層32a〜32dとを備える。第1〜第4ワード線導電層32a〜32dは、メモリトランジスタの制御電極として機能する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】Fin型構造を採用した半導体記憶装置においてカップリング比の各メモリセル間のバラつきを抑制する。また複数のアクティブエリア間のリーク電流を抑制する。

【解決手段】シリコン基板2の主表面高さは均一に形成されていると共にシリコン酸化膜3の上面高さは均一に形成されている。シリコン酸化膜3がSIMOX法により形成され、アクティブエリアSaがシリコン酸化膜3の上面上まで達する素子分離溝2gによって複数に分断されている。したがって、素子分離溝2gの深さおよびアクティブエリアSaの高さを各メモリセル間でほぼ等しい高さに調整でき、隣り合うアクティブエリアSa−Sa間がシリコン酸化膜3によって互いに電気的に絶縁状態に保たれる。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲート型フラッシュメモリにおいて、導電膜の段差部分に絶縁膜等の残渣が残り、シリサイド化されない部分が発生することを防止する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板20の上に、第1の方向に配列された複数の第1の導電膜25aを含む第1の導電膜群が形成されている。第1の方向に、第1の導電膜群に近接して段差緩和パターンが設けられている。段差緩和パターンの上面は、第1の導電膜群に対向する側とは反対側に向かって、階段状または連続的に低くなっている。複数の第1の導電膜25a及び段差緩和パターンを、第1の絶縁膜が覆う。第1の絶縁膜の上に、第1の方向に延在する第2の導電膜が形成されている。

(もっと読む)

半導体装置

【課題】横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制されたフローティングゲート電極を有する不揮発性メモリの半導体装置を提供する。

【解決手段】メモリセルの周囲に設けられた第1遮光壁50により画定された第1被遮光領域10Aと、メモリセルの周囲に設けられた第2遮光壁により画定された第2被遮光領域10A´と、第1遮光壁50に設けられた第1開孔52と、第2遮光壁に設けられ第1開孔52と対向して位置する第2開孔52´と、メモリセルと接続され、第1開孔52から第1被遮光領域10Aの外側に引き出された第1配線層24a,24b,24cと、メモリセルと接続され、第2開孔52´から第2被遮光領域10A´の外側に引き出された第2配線層24a´,24b´,24c´と、少なくとも、第1被遮光領域10Aと第2被遮光領域10A´とに挟まれた領域の上方に設けられた遮光膜と、を含む。

(もっと読む)

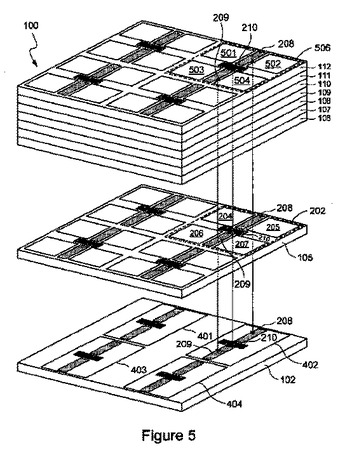

3次元メモリモジュールアーキテクチャ

本発明の様々な実施形態は、スタックされたメモリモジュールに向けられている。本発明の一実施形態において、メモリモジュール(100,600,1200,1400)は、少なくとも1つのメモリ層がスタックされた少なくとも1つのメモリコントローラ層(102,602,1204,1402)を備える。ファインピッチのスルー複数バイア(例えば、スルーシリコン複数バイア)(114,116)が、前記少なくとも1つのメモリコントローラ(401〜404)と、前記少なくとも1つのメモリ層との間の電気的な伝達を提供する前記スタックを通じて、前記少なくとも1つのメモリコントローラの表面に対してほぼ垂直に延在する。追加的には、前記メモリコントローラ層は、前記メモリモジュールに対して双方向にデータを伝達するよう構成された少なくとも1つの外部インターフェースを含む。更にまた、前記メモリモジュールには、光学層(602,1202)を含めることができる。該光学層を、前記スタック内に含めることができ、及び、該光学層は、前記少なくとも1つのメモリコントローラに対して双方向にデータを伝達するバス導波路を有する。前記外部インターフェースは、前記光学層とインターフェースする光学的な外部インターフェースとすることができる。  (もっと読む)

(もっと読む)

半導体素子のコンタクトプラグ製造方法

【課題】ナンドフラッシュメモリ等のソース/ドレインコンタクトプラグを形成する半導体素子のコンタクトプラグ製造方法を提供する。

【解決手段】選択ラインSSLとワードラインWL0,WL1間の露出された半導体基板102に接合領域114a、114bを形成する段階と、選択ラインSSLとワードラインWL0,WL1上に第1の保護膜120を形成する段階と、第1の保護膜120上に絶縁層122を形成する段階と、選択ラインSSL間の第1の保護膜120が露出されるように選択ラインSSL間の絶縁層122にコンタクトホールAを形成する段階と、コンタクトホール側壁に露出された第1の保護膜上に第2の保護膜124を形成する段階と、コンタクトホールA底面の第1の保護膜120を除去する段階、及びコンタクトホールAに導電物質を形成して接合領域114a、114bと連結されるコンタクトプラグを形成する段階とを含む。

(もっと読む)

半導体装置、その製造方法及び駆動方法

【課題】FEOLプロセスにおける拡散工程中のチャージアップから正負とも低電圧の範囲からメモリ素子を保護し、且つ製造工程完了後は、メモリ素子の駆動に必要な正負両極性の高電圧をメモリ素子に印加することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板11に形成された被保護素子と、第2導電型ウェル14に形成された第1の保護トランジスタ41と、第1導電型ウェル13に形成された第2の保護トランジスタ42とを備えている。第2の保護トランジスタ42の第4のソース・ドレイン拡散層22Bは第2の拡散層27と接し、第3のソース・ドレイン拡散層22Aは、第2導電型ウェル14において第1の保護トランジスタ41の第2のソース・ドレイン拡散層21Bと接している。第1の保護トランジスタ41の第1のソース・ドレイン拡散層21Aは、被保護素子電極32と接する第1の拡散層26と接している。

(もっと読む)

相変化型不揮発性メモリ及び半導体装置

【課題】プロセス限界を超えてIresetの低減を図ることができる相変化型不揮発性メモリを提供する。

【解決手段】下部電極11と、下部電極11上に形成された層間絶縁層12と、層間絶縁層12を貫通する孔部13に埋め込まれた不純物拡散層14と、層間絶縁層12上に形成された相変化記録層15と、相変化記録層15上に形成された上部電極16と、不純物拡散層14が埋め込まれた孔部13の側面に配置されたサイドゲート電極24と、サイドゲート電極24と不純物拡散層14との間に配置されたサイドゲート絶縁膜25とを備え、サイドゲート電極24がサイドゲート絶縁膜25を介して不純物拡散層14に電界を印加する。これにより、孔部13に埋め込まれた不純物拡散層14を空乏層化させて、この不純物拡散層14の実効的な径φを孔部13の径よりも小さくすることができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル間の容量結合を低減して浮遊ゲート間干渉を抑制することができる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板10、半導体基板10上に形成された第1の絶縁膜11、半導体基板10上に第1の絶縁膜11を介して形成された浮遊ゲート12、この浮遊ゲート12上に形成された第2の絶縁膜13及び浮遊ゲート上に第2の絶縁膜13を介して形成された制御ゲート14を有する複数のメモリセルMCと、半導体基板10に形成されゲート幅方向に隣接するメモリセルMC間を分離するゲート長方向に延びる素子分離絶縁膜17と、素子分離絶縁膜17の上で且つゲート幅方向に隣接する浮遊ゲート12間に形成された空隙部22とを有する。

(もっと読む)

41 - 60 / 107

[ Back to top ]