Fターム[5F083KA17]の内容

Fターム[5F083KA17]の下位に属するFターム

アドレス選択線 (50)

プレート線 (113)

多層化配線(WL、BLを除く) (150)

Fターム[5F083KA17]に分類される特許

21 - 40 / 107

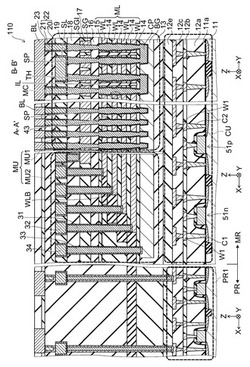

不揮発性半導体記憶装置及びその製造方法

【課題】回路部の上部にメモリ部を形成し、回路部が高温にさらされても回路部の配線層やコンタクトが劣化しない不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板11と、メモリ部MUと、半導体基板とメモリ部との間の回路部CUと、を備える。メモリ部は、半導体基板の主面11aに垂直な第1方向に交互に積層された複数の電極膜WLと複数の絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜と半導体ピラーとの交差部に対応して設けられた記憶部43と、を有す。回路部は、それぞれ第1、第2導電型のソース/ドレイン領域を有する第1、第2トランジスタ51n、51pと、シリサイドを含む第1配線W1と、ソース/ドレイン領域と同じ導電型のポリシリコンからなるコンタクトプラグC1、C2と、を有す。

(もっと読む)

半導体装置の製造方法

【課題】多段キャパシタの形成およびキャパシタシリンダを支えるサポート絶縁膜の周辺回路領域における除去を工程数を増大させることなく達成する、キャパシタシリンダが多段に積層されたキャパシタを有する半導体装置の製造方法を提供する。

【解決手段】容量絶縁膜および上部電極の形成工程をそれぞれ1回の成膜工程で行うと共に、周辺回路領域のスルーホールエッチングや水素アニールの妨害となるサポート絶縁膜について、周辺回路領域の残すべき層間絶縁膜の最上層のみ、容量絶縁膜および上部電極形成時に一括して除去し、それより下層の周辺回路領域のサポート絶縁膜がある場合は、メモリセル領域のコア絶縁膜除去のための開口形成と同時に除去する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】MONOS型メモリにおいて、コンタクトホール形成時に発生する紫外線の影響を抑制し、ビット線コンタクト部近傍に配置されるメモリセルの初期しきい値電圧の上昇を防止する。

【解決手段】半導体記憶装置は、ビット線拡散層11と、ビット線絶縁膜12と、ONO絶縁膜4と、第2ゲート電極6と、コンタクト拡散層13と、層間絶縁膜9と、コンタクト電極8と、紫外線遮光膜22と、紫外線遮光膜21とを備える。紫外線遮光膜22は、コンタクト電極8に最も近い第2ゲート電極6におけるコンタクト電極8に近い側の側面を覆っており、紫外線遮光膜22上における少なくとも一部と紫外線遮光膜21とは、平面的に見て、重なっている。

(もっと読む)

半導体記憶装置

【課題】消費電力の低減と安定した動作を実現できるようにした半導体記憶装置を提供する。

【解決手段】SOI層に形成されたメモリーセル50を備え、このメモリーセルは、部分空乏型の第1トランジスター10と、第2トランジスター20とを有する。第1トランジスター10は、SOI層上に絶縁膜を介して形成されたゲート電極14と、ゲート電極14の両側下のSOI層に形成されたN型のソース15a又はドレイン15bとを有する。また、第2トランジスター20は、SOI層上に絶縁膜を介して形成されたゲート電極24と、ゲート電極24の両側下のSOI層に形成されたP型のソース25a又はドレイン25bとを有する。さらに、第1トランジスター10のボディ領域にソース25aが電気的に接続されている。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】電気ヒューズの切断状態を良好に保つ。

【解決手段】電気ヒューズと他の素子を持つ半導体装置において、電気ヒューズと他の素子は、それぞれ、上層配線と下層配線と、それらを層間配線で接続するビアを有する。このとき、切断状態を正常にするために、電気ヒューズのビア径が、上層配線の断面積や、他の素子のビア径よりも小さい状態となるように、ビアや上層配線を設けるとともに、ビアや上層配線の寸法を換え、断面積比を最適化する。

(もっと読む)

半導体記憶装置

【課題】メモリセルのコントロールゲートとして機能する電極層の電位が他領域に影響するのを抑制することができる半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、半導体基板11上におけるメモリセル領域及び周辺回路領域にわたって設けられ複数の電極層WL1〜WL5と複数の絶縁層24とが交互に積層された積層体と、メモリセル領域における積層体を貫通して形成されたホールの内部に設けられ積層体の積層方向に延びる半導体層21と、半導体層21と電極層WL1〜WL5との間に設けられた電荷蓄積層17と、周辺回路領域における積層体の下に設けられ、電極層WL1〜WL5に電位を転送する転送トランジスタと、転送トランジスタと最下層の電極層WL1との間に設けられ、転送トランジスタの拡散層の電位に応じたシールド電位が与えられる下部シールド配線層SL1とを備えている。

(もっと読む)

半導体記憶装置

【課題】配置密度を高めたり、素子特性を安定化したりしつつ、ビット線とキャパシタコンタクトの重ね合わせマージンを確保する。

【解決手段】半導体記憶装置100は、平面視で第1の活性領域106a上に形成された第1のビット線126aおよび第2のビット線126bと、第1の活性領域106a上に形成された第1のセルコンタクト122aと、第1のセルコンタクト122a上に形成されるとともにキャパシタ(不図示)に接続された第1のキャパシタコンタクト128aとを含むDRAMを含む。平面視において、第1のセルコンタクト122aは、第1のビット線126aよりも第2のビット線126bに近い位置に設けられ、第1のキャパシタコンタクト128aは、第1のセルコンタクト122aに対して第1のビット線126aに近づく方向にずらして形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチングストッパ膜を有し、配線間容量の増大を抑制可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板11と、半導体基板11の表面上部に配設された層間絶縁膜29と、層間絶縁膜29に埋め込まれ、半導体基板11に対向する上面が層間絶縁膜29の上面と面一に配設され、互いに離間して配置された複数のビアプラグ31と、層間絶縁膜29及びビアプラグ31の表面上部に配設された層間絶縁膜39と、層間絶縁膜39によって分離され、ビアプラグ31と接続され、ビアプラグ31に対向する上面が層間絶縁膜39の上面と面一に配設され、層間絶縁膜39を挟んで相対向する側面に、層間絶縁膜29の側から順に、層間絶縁膜29とはエッチング性が異なり且つ層間絶縁膜39より比誘電率の高い側壁絶縁膜35、及び側壁絶縁膜35とはエッチング性が異なる側壁絶縁膜37を有する複数の第2配線33とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】MONOS型のメモリセルに対するデータの消去速度を改善させる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板18と、半導体基板18中に埋め込み領域として形成された第1導電型のジャンクションリーク発生層21と、半導体基板18中に形成され、ジャンクションリーク発生層21を挟む第1導電型とは逆の第2導電型のウェル領域20,22と、半導体基板18の表面に近いウェル領域22上に一定の間隔をおいて形成された第1導電型の2つの不純物拡散層23と、2つの不純物拡散層23の間のウェル領域22上に形成されたトンネル絶縁膜24と、トンネル絶縁膜24上に形成されたチャージトラップ型の電荷蓄積層25と、電荷蓄積層25上に形成されたブロック絶縁膜26と、ブロック絶縁膜26上に形成されるコントロールゲート電極28により構成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】強誘電体キャパシタの下部電極の凹凸形成の制御性を向上させた半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、複数の突出部20を有するように形成された下部電極LEと、下部電極上に形成された強誘電体膜FEと、強誘電体膜上に形成された上部電極UEとを含む強誘電体キャパシタFCを備えている。

(もっと読む)

不揮発性半導体メモリ

【課題】微細化に伴うメモリセルの素子特性の劣化を抑制できるNAND型フラッシュメモリを提供する。

【解決手段】不揮発性半導体メモリは、素子分離絶縁膜10によって区画された素子領域1と、2つの拡散層間の素子領域1表面上に設けられるトンネル絶縁膜2Aと、フローティングゲート電極3Aの上面上に設けられる絶縁体4Aと、フローティングゲート電極3Aの側面上に設けられた電極間絶縁膜5Aと、フローティングゲート電極3Aの上面上に設けられる第1の絶縁体4Aと、絶縁体4A及び電極間絶縁膜5Aを介して、フローティングゲート電極3A上に設けられるコントロールゲート電極5Aとを具備し、絶縁体4Aの膜厚T1は電極間絶縁膜5Aの膜厚T2よりも厚く、電極間絶縁膜5Aは絶縁体4A上又は素子分離絶縁膜10上のうち少なくともいずれか一方に、スリットを有している。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

半導体装置の製造方法

【課題】周辺トランジスタやメモリセルを構成するnMISトランジスタの駆動特性の劣化を抑制することができる半導体装置の製造方法を提供する。

【解決手段】n型の電界効果型トランジスタを含む半導体装置の製造方法において、半導体基板に対してp型不純物となる元素を有するp型不純物元素含有ガスを含むエッチングガスを用いて、半導体基板に素子分離溝を形成するとともに、素子分離溝の内面に、p型不純物を含む不純物層を形成する素子分離溝形成工程と、素子分離溝内に塗布型絶縁膜を埋め込んで素子分離絶縁膜を形成する素子分離絶縁膜形成工程と、を含む。

(もっと読む)

半導体記憶装置

【課題】メモリセル面積を拡大させることなく、メモリセルにおける単位面積あたりの容量値を増やした半導体記憶装置を実現する。

【解決手段】メモリセル100は、トランジスタ101と、メモリ素子104と、第1の容量102と、第2の容量103と、を有する。第1の容量102は、トランジスタ101を構成する半導体膜108、ゲート絶縁膜114およびゲート電極109で構成され、トランジスタ101と同時に形成される。第2の容量103は、メモリ素子104を構成する電極107ならびに電極107上に形成した絶縁膜113および電極111から構成される。また、第2の容量103は、第1の容量102の直上に形成する。このように、メモリ素子104と並列に接続する、第1の容量102および第2の容量103を形成する。

(もっと読む)

半導体メモリ装置及びその製造方法

【課題】周辺回路領域のトランジスタを電源電圧の急激な変動を防止するためのパワーデカップリングキャパシタとして使用することによって半導体メモリ装置の集積度及び信頼性を向上させることのできる半導体メモリ装置及びその製造方法を提供する。

【解決手段】コア領域と周辺回路領域とに分割される基板上に形成される半導体メモリ装置において、前記コア領域及び前記周辺回路領域にかけて拡張されるキャパシタ構造を含み、前記キャパシタ構造の各部分は、前記コア領域ではメモリセルキャパシタとして機能し、前記周辺回路領域では第1及び第2キャパシタとして機能し、前記第1及び第2キャパシタの組み合わせは、第1パワーデカップリングキャパシタ(power decoupling capacitor)として機能し、前記周辺回路領域に配置されるトランジスタは、第2パワーデカップリングキャパシタとして機能することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、寸法誤差を抑制したパターンを有する半導体装置の製造方法を提供する。

【解決手段】被加工膜6上に周期パターン12と非周期パターン13を含む第一のパターン11を形成し、第一のパターン11を覆うように被加工膜6上に第二の膜14を形成し、

被加工膜6を露出するように第二の膜14を加工して、第一のパターン11の側壁部に第二の側壁パターン15を形成し、第一のパターン11のうちの周期パターン12を選択的に除去し、第一のパターン11及び第二の側壁パターン16をマスクに被加工膜6を加工することにより、周期パターン2と非周期パターン3を形成すると同時に、周期パターン2と周期パターンの両端部に隣接する非周期パターン3との間に、周期パターン2との間で一定の周期を形成するようにダミーパターン4を形成する半導体装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置

【課題】占有面積の増大を抑制したNAND型フラッシュメモリの不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングMSは、各々のメモリブロックMB毎に、カラム方向にm列配列されている。ワード線導電層31a〜31dは、n層積層されている。ワード接続層51は、カラム方向に配列され、ワード線導電層31a〜31dのロウ方向の一端近傍へと片側から延びるように形成され、ワード線導電層31a〜31dにコンタクトプラグ511を介して接続され,(数式1)の関係を満たす。m≧n・・・(数式1)

(もっと読む)

半導体記憶装置

【課題】水素による強誘電体キャパシタの特性劣化を抑制するメモリを提供する。

【解決手段】メモリは、第1の層間膜を貫通して半導体基板上のトランジスタに接続された第1、第2のプラグと、第1のプラグ上の強誘電体キャパシタの側面を被覆する第2の層間膜と、第2のプラグと上部電極とを接続するローカル配線とを備え、第2のプラグ上で隣接する強誘電体キャパシタの上部電極はローカル配線で第2のプラグに接続され、第1のプラグ上で隣接する強誘電体キャパシタの下部電極は第1のプラグに接続され、第1、第2のプラグで接続される強誘電体キャパシタを含むセルブロックが配列され、隣接するセルブロックはローカル配線の半ピッチずれて配置され、第2のプラグの両側で隣接する強誘電体キャパシタ間の第1の間隔は第2の層間膜の堆積膜厚の2倍よりも大きく、隣接するセルブロック間の第2の間隔は第2の層間膜の堆積膜厚の2倍よりも小さい。

(もっと読む)

不揮発性半導体記憶装置

【課題】高い信頼性を有し且つ安価な不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングは、基板Baに対して垂直方向に延びる一対の柱状部、及び一対の柱状部の下端を連結させるように形成された連結部を有するU字状半導体層35と、柱状部の側面を取り囲むように形成されたメモリゲート絶縁層34と、柱状部の側面及びメモリゲート絶縁層34を取り囲むように形成され、メモリトランジスタの制御電極として機能するワード線導電層31a〜31eとを備える。ソース側選択トランジスタは、柱状部の上面から上方に延びるソース側柱状半導体層44aと、その側面を取り囲むように空隙Ag2を介して形成され、ソース側選択トランジスタの制御電極として機能すソース側導電層41aとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】露光条件が最適化される領域の配線と異なる方向の配線を必要とする領域の露光マージン不足を回避する。

【解決手段】半導体基板と、

前記半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜上の第1の領域において、第1のデザインルールを適用して形成された、特定方向に沿って走る、複数の第1の配線と、

前記層間絶縁膜上の第2の領域において、前記第1のデザインルールと同じ第2のデザインルールを適用して形成された、前記特定方向に沿って走る、複数の第2の配線と、

前記層間絶縁膜中に形成され、同一電位となるべき少なくとも2つの前記第2の配線を電気的に接続して所望の配線パターンを形成する、接続部材と、

を備える。

(もっと読む)

21 - 40 / 107

[ Back to top ]