Fターム[5F083LA05]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | ローデコーダ(ワード線昇圧回路等を含む) (888)

Fターム[5F083LA05]に分類される特許

761 - 780 / 888

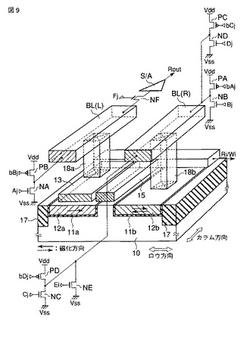

スピン注入FET

【課題】熱的安定性に優れ、素子破壊もないスピン注入FETを提供する。

【解決手段】本発明の例に関わるスピン注入FETは、磁化方向が固定される第1強磁性体11aと、スピン注入電流により磁化方向が変化する第2強磁性体11bと、第1及び第2強磁性体11a,11b間のチャネル上に形成されるゲート電極15と、チャネルに流れるスピン注入電流の向きを制御し、第2強磁性体11bの磁化方向を決定する第1ドライバ/シンカーPA,PB,NA,NBと、第2強磁性体11bの磁化容易軸方向の磁場を発生させるアシスト電流を流す配線BL(R)と、配線BL(R)を流れるアシスト電流の向きを制御する第2ドライバ/シンカーPC,PD,NC,NDとを備える。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】参照セルのリカバーに要する時間を短くする。

【解決手段】本発明の例に関わる磁気ランダムアクセスメモリは、第1及び第2参照セル列を含み、行列状に配置された複数の磁気抵抗効果素子12を有するメモリセルアレイ11と、第1参照セル列に共有される第1リファレンスビット線BLref0と、第2参照セル列に共有される第2リファレンスビット線BLref1と、第1書き込み電流を流すための第1ドライバ・シンカー17,18と、第2書き込み電流を流すための第2ドライバ・シンカー17,18と、第1及び第2参照セル列に記憶されたデータを一行ずつチェックし、データの破壊の発見に続けて、一軸書き込み方式により、第1及び第2参照セル列に対して一括してデータ書き込みを実行する制御回路22とを備える。

(もっと読む)

不揮発性半導体メモリ

【課題】バイト単位の書き換えが可能な不揮発性半導体メモリを提供する。

【解決手段】メモリセルアレイは、1個のメモリセルとこれを挟み込む2個のセレクトトランジスタとから構成されるユニットを有する。1ブロックには、1本のコントロールゲート線が配置され、1本のコントロールゲート線に接続されるメモリセルにより1ページが構成される。ビット線には、ラッチ機能を持つセンスアンプが接続される。データ書き換えは、まず、1ページ分のメモリセルのデータをセンスアンプに読み出し、センスアンプでデータの上書きを行い、ページ消去を行った後、センスアンプのデータを1ページ分のメモリセルに書き込む。センスアンプにおけるデータの上書きによりバイト単位のデータ書き換えが可能となる。

(もっと読む)

結合の補償を含む不揮発性記憶のための読み出し動作

不揮発性メモリセルのフローティングゲート(又は他の電荷蓄積要素)上に蓄積される見かけの電荷内のシフトは、隣接フローティングゲート(又は他の隣接電荷蓄積要素)内に蓄積される電荷に基づく電界の結合のために発生する可能性がある。この問題は、異なる時間にプログラムされる隣接メモリセルの集合の間で最も顕著に発生する。この結合を補償するために、所定のメモリセル用の読み出し処理は、隣接メモリセルのプログラムされた状態を考慮することができる。  (もっと読む)

(もっと読む)

異なるメモリセルに対する同時読み取りおよび書き込み

不揮発性メモリアレイは、ワードラインWL1,..,WL6とビットラインBL1,..,BL8のグリッドを含む。複数のメモリセル210の各メモリセルが、ワードラインのうちの1つとビットラインのうちの1つの交点領域に位置する。複数のビットを含むデータワードを読み取る/書き込むための読み取り/書き込み回路280は、データワードの連続するビットの各ペアを、異なるワードラインと異なるビットラインの交点領域に位置するメモリセルの各ペアにマップするように動作する。  (もっと読む)

(もっと読む)

不揮発性記憶内の結合の補償

不揮発性メモリセルのフローティングゲート(又は他の電荷蓄積要素)上に蓄積される見かけの電荷内のシフトは、隣接フローティングゲート(又は他の隣接電荷蓄積要素)内に蓄積される電荷に基づく電界の結合のために発生する可能性がある。この問題は、異なる時間にプログラムされる隣接メモリセルの集合の間で最も顕著に発生する。この結合を補償するために、所定のメモリセル用の読み出し処理は、隣接メモリセルのプログラムされた状態を考慮することができる。  (もっと読む)

(もっと読む)

メモリラインドライバのノンバイナリグループ用のデコーディング回路

【解決手段】 メモリラインドライバのノンバイナリグループ用のデコーディング回路が開示されている。或る実施形態では、バイナリデコーダと、ノンバイナリ演算を実行するための回路と、を備えている集積回路であって、ノンバイナリ演算の結果がバイナリデコーダへ入力として提供される、集積回路が開示されている。他の実施形態では、複数のアレイラインを備えているメモリアレイと、2の整数乗ではないアレイラインドライバ回路と、アレイラインドライバ回路の1つを選択するように構成されている制御回路と、を備えている集積回路が開示されている。この制御回路は、バイナリデコーダと、ノンバイナリ演算を実行する前置デコーダ部分と、を備えている。ここで説明する概念は、単独で或いは組み合わせて使用することができる。 (もっと読む)

不揮発性メモリの読み出し動作中の結合の補償

不揮発性メモリセルのフローティングゲート(又は他の電荷蓄積要素)上に蓄積される見かけの電荷内のシフトは、隣接フローティングゲート(又は他の隣接電荷蓄積要素)内に蓄積される電荷に基づく電界の結合のために発生する可能性がある。この問題は、異なる時間にプログラムされる隣接メモリセルの集合の間で最も顕著に発生する。この結合を補償するために、所定のメモリセルの読み出し処理は、隣接メモリセルのプログラムされた状態を考慮することができる。  (もっと読む)

(もっと読む)

複数メモリ層の部分的実現を伴うデコード互換性を含む集積回路メモリアレイ構成

3次元メモリアレイを有する集積回路は、所与の数のメモリ面のための準備はあるが(図15)、マスクを省略し、省略されるメモリ面に関連する処理ステップを省略することによって、他のメモリ面または装置の残りの部分のための他の製作マスクのいずれをも変えることなく、またアレイの読出しまたは読出し/書込みパスにルーチングまたは他の構成の変更を要することなく、より少ない数のメモリ面を含むように製作され得る。ある層選択回路を選択的にイネーブルするための制御回路は、実現されたメモリ層のそれぞれのアレイ線を、実現されるメモリ面の数にかかわらず、各それぞれのI/Oバス線に結合するよう構成可能であって、層選択回路はそのように適切に配置される。  (もっと読む)

(もっと読む)

パルス電流による磁壁移動に基づいた磁気抵抗効果素子および高速磁気記録装置

【課題】高速磁化反転が可能で、臨界電流密度の低い磁気抵抗素子および固体メモリを実現すること。

【解決手段】第1の磁化固定層、磁化自由層、第2の磁化固定層からなり、前記第1の磁化固定層と前記第2の磁化固定層とを略反平行とし、前記第1磁化固定層と前記磁化自由層間、あるいは前記第2磁化固定層と前記磁化自由層間の両方の遷移領域が磁壁をトラップでき、かつ、どちらか一方に磁壁が存在する構造を備え、前記第1、第2磁化固定層の間に、1nsのパルス幅の直流電流密度が106A/cm2を超えない値のパルス電流を供給する。

(もっと読む)

タイトピッチのメモリアレイ線のためのトランジスタレイアウト構成

複数ヘッドのワード線ドライバ回路は、曲がったゲートトランジスタを組み込み、別の方法で緊密なピッチのアレイ線とインターフェイスするのに達成可能なピッチを減少させる。いくつかの例示的な実施形態では、3次元メモリアレイは、少なくとも1つのメモリブロックを水平方向に横断する複数のメモリブロックおよびアレイ線を含む。垂直のアクティブ領域ストライプは、第1のメモリブロックの下に配置され、複数の曲がったゲート電極はそれぞれ、各々のアクティブ領域ストライプと交差して、個々のソース/ドレイン領域を画定する。1つおきのソース/ドレイン領域は、アクティブ領域ストライプのためのバイアスノードと結合され、残りのソース/ドレイン領域は、第1のメモリブロックと関連するそれぞれのアレイ線とそれぞれ結合され、それによって、それぞれのアレイ線のそれぞれの第1のドライバトランジスタを形成する。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】階層ワード線構造のDRAM等において、ワード線選択時の低消費電力化を図りつつ、DRAM等の高集積化を図る。

【解決手段】半導体集積回路装置は、メインワード線及び複数のサブワード線と、複数のビット線と、メモリセルアレイと、センスアンプ列と、メインワード線駆動信号生成回路と、サブワード線駆動信号生成回路と、サブワード線非選択信号生成回路と、サブワード線駆動部とを備えている。1つのサブワード線駆動部には、N型拡散領域の複数の列に含まれる複数のN型拡散領域が存在し、各N型拡散領域上に各々ゲート電極を有する複数のMOSトランジスタが配置されており、1つのサブワード線非選択信号回路から延びるサブワード線非選択信号用の配線が、その両側のサブワード線駆動部で共通の列に属するN型拡散領域の上のゲート電極に接続されている。

(もっと読む)

半導体記憶回路、半導体記憶回路の構成方法、及び、半導体記憶回路のレイアウト生成方法

【課題】 システムLSIに含まれる半導体記憶回路のレイアウト面積を小さくすることによってシステムLSIをより小型化できる、半導体記憶回路及び半導体記憶回路の構成方法に関する。

【解決手段】 メモリマクロセル1は、第1及び第2のメモリセルアレイ10a及び10bとその周辺回路とを備える。周辺回路は、ロウデコーダブロック20、制御ブロック50、並びに、第1及び第2の入出力回路ブロック80a及び80bを備える。プリデコード信号配線ブロック30に形成された電源配線は、第1及び第2のロウデコーダ回路ブロックで共用される。また、制御ブロック50形成された書込パルス発生回路と遅延回路は、第1及び第2のメモリセルアレイ10a及び10bで共用される。また、制御回路ブロック70では、一つのクロック信号によってタイミング制御が行われる。

(もっと読む)

記憶装置および半導体装置

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の記憶装置及びそれを有する半導体装置を提供することを課題とする。また、信頼性が高く、安価な不揮発の記憶装置及び半導体装置の提供を課題とする。

【解決手段】絶縁表面上に形成される第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層に挟持される第1の絶縁層と、第1の導電層の一部を覆う第2の絶縁層とを有し、第1の絶縁層は第1の導電層の端部、絶縁表面、及び第2の絶縁層を覆うことを特徴とする記憶装置である。

(もっと読む)

半導体メモリ

【課題】 ダミービット線が原因となるスタンバイ電流を削減し、半導体メモリの歩留を向上する

【解決手段】 リアルメモリセルに接続されるリアルビット線が、隣接する回路要素とショートしやすいことが判明した場合、ダミービット線は、その回路要素に供給される電圧線に接続される。例えば、ダミービット線は、接続配線を介して負電圧線に直接接続される。あるいは、ダミービット線は、内部電圧線のいずれかに選択的に接続される。本発明の適用により、ダミービット線が隣接する回路要素とショートした場合にも、ダミービット線と回路要素間で発生するリークを防止できる。リークを防止できるため、内部電圧の生成回路が不必要に動作することを防止でき、スタンバイ電流が増加することを防止できる。この結果、半導体メモリの歩留を向上できる。

(もっと読む)

磁気記憶装置

【課題】高集積化が可能な磁気記憶装置を提供する。

【解決手段】磁気記憶装置は、第1ノードと第2ノードとの間に並列に接続され、かつ記憶する情報により抵抗値が変化する複数の可変抵抗素子Rと、第1ノードに接続され、複数の可変抵抗素子Rを選択する選択トランジスタ14と、第2ノードに接続されたビット線BLとを具備し、第1ノードと第2ノードとの間で可変抵抗素子Rを含む複数の電流経路は、抵抗値が異なる。

(もっと読む)

抵抗ヒステリシス素子を備えるメモリマトリックスの制御

2以上のアイドル回路状態、全列更新回路状態及び列選択的更新状態の間の、回路状態遷移を用いる書込み処理を規定するために用いられる、メモリマトリックス用の制御回路(1、11)。また、アクセス中に、制御回路は、列選択的更新指令の実行中には、第一アイドル状態(I1)から列選択的更新状態(W)に交互に切り替わり、全列更新指令の実行中には、第二アイドル状態(I2)から全列更新状態(E)に交互に切り替わる。制御回路(1、11)は、連続する列選択的更新指令及び全列更新指令の実行の間には、第二及び第一アイドル状態(I2、I1)に切り替わることなく、それぞれ第一及び第二状態(I1、I2)にとどまる。 (もっと読む)

半導体集積回路装置の製造方法

【課題】MISFETの微細化を推進する。

【解決手段】窒化シリコン膜14とサイドウォールスペーサ16とをマスクにしたドライエッチングによって、素子分離領域の基板1に溝2aを形成した後、窒化シリコン膜14の側壁のサイドウォールスペーサ16を除去し、次いで、基板1を熱酸化することによって、活性領域の周辺部の基板1の表面をラウンド加工し、凸状の丸みが付いた断面形状とする。これにより、活性領域の寸法を減少させることなく、その周辺部をラウンド加工することができる。

(もっと読む)

256Megダイナミックランダムアクセスメモリ

【課題】ピンの配置に制約が有る中でのチップの最適レイアウトの実現と、最短の時間でデバイスが適切な動作を行える電源アーキテクチャの提供。

【解決手段】本発明は、複数のアレイブロックと、複数のアレイブロックの中央に配置された複数のパッドとを具えるダイナミックランダムアクセスメモリ用の電源であって、複数のパッドの近傍に配置され、複数のアレイブロックへの供給電圧を生成するための複数の電圧源を具えている。複数の電圧源は、複数の電力増幅器を有する電圧レギュレータを具えており、少なくとも1つの電力増幅器は、複数のアレイブロックの各々と関連付けられている。複数の電圧源は、設定された出力電力レベルを達成するために、別個の又は同時の何れかの動作を行なうために複数のグループに分割された複数の電圧ポンプ回路を有する電圧ポンプを含んでいる。

(もっと読む)

抵抗ヒステリシス素子を備えるメモリマトリックスの駆動

セルの行及び列を備え、各セルは、セル(20)の行端子及び列端子の間に直列につながれた抵抗ヒステリシス素子(24)と閾値素子(22)とを備えるメモリマトリックス(10)。 抵抗ヒステリシス素子(24)は、相互に反対の極性の、上位及び下位それぞれのヒステリシス閾値を有する。選択された行のセル(20)の列端子及び行端子の間に電位差を加え、読出し動作を実行する。この電位差は読出し極性を有し、セル(20)にかかる電圧は上位ヒステリシス閾値に対応する方向にある。 選択された行のセル(20)の列端子及び行端子の間に電位差を加え、削除動作を実行し、選択された行の全てのセル(20)は削除動作でまとめて削除される。削除動作に対する電位差は読出し極性を有する。さらに選択された行のセル(20)の列端子及び行端子の間に電位差を加え、書込み動作を実行する。書込み動作への電位差は、下位ヒステリシス閾値の極性に対応した書込み極性を有し、書込みデータに応じて選択されたセルを更新する。 (もっと読む)

761 - 780 / 888

[ Back to top ]