Fターム[5F083LA05]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | ローデコーダ(ワード線昇圧回路等を含む) (888)

Fターム[5F083LA05]に分類される特許

841 - 860 / 888

半導体記憶装置

【課題】レプリカビット線の電荷をダミーセルのリーク電流により早く引き抜いてしまい、所望のセンスアンプ起動タイミングを得ることができない。

【解決手段】 メモリアレイと、センスアンプ回路と、メモリセルと同一の素子を有し、段数に応じたレベルの信号を共通のレプリカビット線に出力する複数のレプリカセル105を含むレプリカ回路と、共通のレプリカビット線に負荷として接続されているダミーセル109Bとを備え、ダミーセル109BのドライブトランジスタND1のソースをHighレベルVDDに接続する。これによりレプリカビット線REPBLからダミーセルへのリーク電流を抑え、最適な起動タイミングをセンスアンプ回路に供給できる。

(もっと読む)

情報を格納する方法及びシステム

本発明の一実施例によると、メモリ物質をプログラムする方法及びシステムが提供される。本方法は、メモリ物質を所定の状態にプログラムするため、様々な振幅及び様々な持続時間を有する3つの信号をメモリ物質に印加するステップから構成される。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】ビット線交差方式を採用して隣接ビット線間の容量を低減する効果を維持しつつも、ダミーメモリセルを無くしてメモリセルアレイの面積の増大を回避し得る半導体記憶装置を得る。

【解決手段】第2配線層内には、交差配線18a,18bとシャント配線SL0〜SL2,SL7〜SL9とが形成されている。交差領域TR3,TR4は、第X3〜X6行に属している。シャント配線SL0〜SL2,SL7〜SL9は、交差領域TR3,TR4が属さない第X0〜X2,X7〜X9行にそれぞれ属している。第4配線層内には、シャント配線SL3〜SL6が形成されている。シャント配線SL3〜SL6は、交差領域TR3,TR4が属する第X3〜X6行にそれぞれ属している。

(もっと読む)

半導体メモリ装置及びリード動作方法

【課題】リード動作の時に漏洩電流を補償することができる相変化メモリ装置を提供する。

【解決手段】ワードラインとビットラインとの交差点に位置する複数個のメモリセルと、ダミービットラインに連結された複数個のダミーセルと、前記ダミービットラインに連結され漏洩補償電流を前記ビットラインに出力する漏洩補償回路と、第1制御信号に応じてリード動作時に必要なリード電流を前記ビットラインに出力する理度電流供給回路と、を備える。

(もっと読む)

不揮発性半導体記憶装置及び不揮発性半導体記憶装置の製造方法

【課題】 メモリセルトランジスタのショートチャネル効果を低減可能な不揮発性半導体記憶装置を提供する。

【解決手段】 絶縁層1と、絶縁層1上に複数のメモリセルトランジスタがマトリクス状に配置された不揮発性半導体記憶装置であって、メモリセルトランジスタM11は、絶縁層1上に配置された対向する第1導電型(n+型)のソース及びドレイン領域421,422と、ソース及びドレイン領域421,422に挟まれたソース及びドレイン領域421,422より不純物密度の低い第1導電型(n型)のチャネル領域411と、チャネル領域411上に絶縁されて配置された浮遊ゲート電極13と、浮遊ゲート電極13上に絶縁されて配置された制御ゲート電極15とを備えるデプレッション型のMISトランジスタである。

(もっと読む)

混合原子価導電性酸化物を用いたメモリ

【課題】

【解決手段】混合原子価導電性酸化物を用いたメモリが開示されている。そのメモリは、酸素欠乏状態で導電性が下がる混合原子価導電性酸化物と、酸素に対する電解質であり、酸素イオンの移動を引き起こすのに有効な電場を促進する電解質トンネル障壁と、を備える。

(もっと読む)

半導体装置、及びその製造方法

【課題】 単層ポリシコンゲートから成る不揮発性メモリのセル面積を低減し、かつ超低消費電力で動作させる。

【解決手段】 フローティングゲート6端下部のN型ウエル4の基板表面に、ゲート酸化膜5を介在させて設けられたP型不純物領域8と、前記N型ウエル4が構成する接合に−5Vのような逆バイアス電圧を印加して、バンド間トンネル現象によって発生するホットエレクトロンを前記フローティングゲート6へ注入して書込みを行う。書込み時間はおおよそ10μs、書込み動作時の前記接合の漏洩電流は100nA程度に設計できるため、書込みに要するエネルギーは5pJまで低減され、従来のスタックド・ゲート型メモリセルのチャンネルホットエレクトロン注入を用いた書込みのエネルギーに比較して1/100以下に低減できる。

(もっと読む)

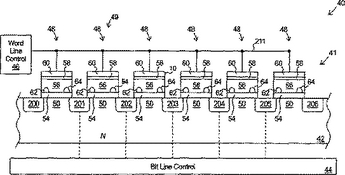

不揮発性メモリセルをプログラミングするための改良システム

デュアルビット誘電体メモリセル(48)のアレイ(40)は複数のビット線を有している。第1ビット線(201)はアレイ(40)内のメモリセルの列内の複数のメモリセル(38)のそれぞれにソース領域を形成する。第2ビット線(202)は列内の複数のメモリセル(38)のそれぞれにドレイン領域を形成する。第1ビット線(201)と第2ビット線(202)間には、逆の導電性のチャネル領域(50)が設けられており、それぞれと接合を形成している。選択ワード線(211)がチャネル領域(50)の上部に設けられており、また、同じ行内の複数のメモリセル(48)のそれぞれの上部にゲート(60)を形成している。複数の非選択ワード線(210、212)はそれぞれ選択ワード線(211)に並列であり、またそれぞれが複数のメモリセル(49)から選択されたメモリセル以外の列内の複数のメモリセル(48)の1つの上部にゲート(60)を形成している。ワード線制御回路(46)は選択ワード線(211)に正のプログラミング電圧(220)を印加し、また同時にビット線制御回路(44)はドレインビット線(202)に正のドレイン電圧を印加し、正のドレイン電圧よりも小さい正のソース電圧をソースビット線(201)に印加する。  (もっと読む)

(もっと読む)

半導体回路

【課題】 高速のスイッチング特性と小サブスレッショルド電流特性とが両立可能なMOS−FETで構成される半導体回路を提供する。

【解決手段】 MOS−FETQ1,Q2により構成される論理回路1を有した半導体回路において、MOS−FETQ1,Q2のバックゲートバイアス電圧Vcc,VSSとは異なる電圧Vpp,Vbbを供給する電圧供給手段15,13と、MOS−FETQ1,Q2のバックゲートバイアス電圧を、電圧Vcc,VSSと電圧Vcc,VSSとは異なる電圧Vpp,Vbbとに切り換えるスイッチング手段10とを備えた構成となっている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 第3ゲートを有する半導体集積回路装置において、微細化と動作速度向上を図るとともに絶縁膜の欠陥密度低減を図る。

【解決手段】 半導体基板100中に形成された第1導電型のウェル101と、ウェル101中の第2導電型のソース/ドレイン拡散層領域105と、半導体基板100上に絶縁膜102を介して形成された浮遊ゲート103bと、浮遊ゲート103bと絶縁膜110aを介して形成された制御ゲート111aと、前記制御ゲートを接続して形成されたワード線と、前記半導体基板、浮遊ゲート、制御ゲートと絶縁膜を介して形成され、浮遊ゲート及び制御ゲートとは異なる第3のゲート107aを有する半導体集積回路装置において、上記第3のゲートがワード線及びチャネルと垂直な方向に存在する浮遊ゲートの隙間に埋込まれて存在するように配置する。

(もっと読む)

半導体集積回路装置の動作方法

【課題】 第3ゲートを有する半導体集積回路装置において、微細化と動作速度向上を図るとともに絶縁膜の欠陥密度低減を図る。

【解決手段】 半導体基板100中に形成された第1導電型のウェル101と、ウェル101中の第2導電型のソース/ドレイン拡散層領域105と、半導体基板100上に絶縁膜102を介して形成された浮遊ゲート103bと、浮遊ゲート103bと絶縁膜110aを介して形成された制御ゲート111aと、前記制御ゲートを接続して形成されたワード線と、前記半導体基板、浮遊ゲート、制御ゲートと絶縁膜を介して形成され、浮遊ゲート及び制御ゲートとは異なる第3のゲート107aを有する半導体集積回路装置において、上記第3のゲートがワード線及びチャネルと垂直な方向に存在する浮遊ゲートの隙間に埋込まれて存在するように配置する。

(もっと読む)

不揮発性半導体記憶装置及び読み出し方法

【課題】 メモリセルアレイの読み出し時にメモリセルに印加される電圧パルスによってメモリセルに含まれる可変抵抗素子の抵抗値が変化して読み出し不良に陥るのを防止した不揮発性半導体記憶装置を提供する。

【解決手段】 メモリセルアレイ15の中からメモリセルを行単位、列単位、または、メモリセル単位で選択するメモリセル選択回路17と、メモリセル選択回路17により選択された選択メモリセルの可変抵抗素子に読み出し電圧を印加する読み出し電圧印加回路22aと、選択メモリセルの内の読み出し対象メモリセルに対し当該可変抵抗素子の抵抗値に応じて流れる読み出し電流の大小を検知して、読み出し対象メモリセルに記憶されている情報を読み出す読み出し回路23とを備え、読み出し電圧印加回路22aは、読み出し電圧とは逆極性のダミー読み出し電圧を選択メモリセルの可変抵抗素子に印加する。

(もっと読む)

半導体装置

【課題】本発明は、NAND型フラッシュメモリにおいて、光近接効果による影響を減少でき、ピッチ変換を含む配線の引き回しを容易に可能とするものである。

【解決手段】たとえば、メモリセルアレイ11とこのセルアレイ11を制御するロウデコーダ回路部13とを有するフラッシュメモリ10において、配線ピッチの異なる、上記メモリセルアレイ11側の配線22aと上記ロウデコーダ回路部13側の配線22bとの間を、配線22aに対する配線入射角P’が30度とされた30度斜め引き出し配線22cにより接続する。こうして、メモリセルアレイ11とロウデコーダ回路部13との間に、30度斜め引き出し配線22cによって配線22a,22bの相互間を接続してなる配線層22を引き回す構成となっている。

(もっと読む)

半導体記憶装置

【課題】

メモリブロック端においてワード線ピッチの周期が乱れることに起因したワード線の倒れや加工精度の低下によって発生する不良を防ぐことができる半導体記憶装置を提供することを目的としている。

【解決手段】

メモリブロック端にダミーワード線を複数本設置し、前記ダミーワード線に対してワードドライバを設置して、ダミーワード線の下に形成されるダミーメモリセルのしきい値状態を制御すると共に、外部からのデータを格納するメモリ領域を動作させる際にも、ダミーワード線に対してバイアスを印加することを特徴とする。メモリブロック端においてワード線ピッチの周期が乱れることに起因したワード線の倒れや加工精度の低下によって発生する不良を防ぎ、歩留まりが高くかつ信頼性の高い動作を実現できる。

(もっと読む)

メモリ・デバイスのワードラインのための方法及び装置

【課題】 製造プロセスへの負担を増すことなく、メモリ・デバイスへの適切なアクセス速度を提供すること。

【解決手段】 メモリ・デバイスにおけるワードラインの速度を改善する方法及び装置において、ワードライン構造は、主ワードライン信号を選択的に分配する主ワードライン610と、主ワードラインに選択的に結合される複数のワードライン678−684とを備える。各ワードラインは、複数の切り換え素子700−714のうちの選択された1つを介して低抵抗の共有相互接続線690、692に選択的に結合される。各切り換え素子は、共有相互接続線の一端に共通に結合され且つ複数のワードラインの対向端に個別に結合される。各切り換え素子は、主ワードライン信号が複数のワードラインのうちの1つと選択的に結合されるとき複数のワードラインのうちの1つを共有相互接続線に結合するよう選択的に活性化される。

(もっと読む)

半導体装置

【課題】フィールド反転の発生を防止し、微細化に有利な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板21の主表面上にマトリクス状に設けられ、それぞれがゲート電極TGと、前記ゲート電極上に設けられたゲート電極コンタクト26と、ゲート幅方向に隣接する前記ゲート電極コンタクト上に設けられゲート幅方向の前記ゲート電極を電気的に接続する配線層27とを備えた複数の高耐圧系絶縁ゲート型電界効果トランジスタTRと、ゲート長方向およびゲート幅方向において隣接する前記トランジスタ間の素子分離領域STI上に設けられ、前記トランジスタの電流経路がオンとなるためにゲートに印加される電位と異なる導電型の電位または基準電位を前記素子分離領域に印加するシールド用ゲート31とを具備している。

(もっと読む)

フラッシュメモリユニット、およびフラッシュメモリ素子のプログラミング方法

フラッシュメモリユニット(12)およびフラッシュメモリ素子(28)をプログラミングする方法を開示する。プログラミング方法は、メモリ素子の制御ゲート(32)およびドレイン(42)にそれぞれのプログラミング電圧を印加することを含み得る。ソースバイアス電位は、メモリ素子のソース(38)に印加され得る。ソースバイアス電位の印加は、プログラミング電圧のうちの1つをソースバイアス切換素子(44)に選択的に印加することで制御され得る。  (もっと読む)

(もっと読む)

磁気抵抗効果素子の製造方法および製造装置

【課題】面積抵抗RAの大幅な増大を招くことなく、高いMR変化率を有する磁気抵抗効果素子を製造できる方法を提供する。

【解決手段】磁化固着層と、磁化自由層と、前記磁化固着層と前記磁化自由層との間に設けられた絶縁層と前記絶縁層を貫通する電流パスを含むスペーサ層とを有する磁気抵抗効果素子の製造方法において、前記スペーサ層を形成するにあたり、前記電流パスを形成する第1の金属層を成膜し、前記第1の金属層上に、前記絶縁層に変換される第2の金属層を成膜し、前記第2の金属層に希ガスのイオンビームまたはRFプラズマを照射して前記第2の金属層中に前記第1の金属層の一部を侵入させる前処理を行い、酸化ガスまたは窒化ガスを供給して、前記第2の金属層を前記絶縁層に変換するとともに前記絶縁層を貫通する前記電流パスを形成する。

(もっと読む)

不揮発性メモリ

【課題】 記憶情報に対する書き込み性能を向上させることができる不揮発性メモリを提供することにある。

【解決手段】 第1の制御トランジスタ20、メモリトランジスタ21、第2の制御トランジスタ22及びメモリトランジスタ21の順に繰り返し直列された回路を有し、制御トランジスタはオンされることにより前記直列方向とは交差する方向に反転層23を形成し、第1の制御トランジスタによる反転層と読み出し書き込み回路50との接続を選択回路51で選択する。メモリトランジスタに隣接する両側の制御トランジスタをオンさせて読出しを行い、第2の制御トランジスタの左右両側の第1の制御トランジスタをオンさせて左右一方のメモリトランジスタを介して他方のメモリトランジスタに書き込みを行なう。選択回路は同じメモリトランジスタに対する読出しと書き込みには同じ読出し書き込み回路を使用するように読出し書き込み回路と反転層を接続する。

(もっと読む)

半導体集積回路装置

【課題】 リーク電流を低減させたROMを備えた半導体集積回路装置を提供する。

【解決手段】 ワード線とビット線の交点に設けられ、記憶情報に対応して上記ビット線に選択的にメモリ電流を流すようにされたMOSFETからなる複数のメモリセルと、アドレス信号に従って1つのワード線を選択するアドレス選択回路とを備えたROMにおいて、ゲート電圧制御回路又はアドレス選択回路とワード線との間にスイッチ素子を設け、スタンバイ状態のとき上記ゲート電圧制御回路により全ワード線を非選択レベルにし、又は上記スイッチ素子をオフ状態にして全ワード線をフローティング状態にする。

(もっと読む)

841 - 860 / 888

[ Back to top ]