Fターム[5F083LA05]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | ローデコーダ(ワード線昇圧回路等を含む) (888)

Fターム[5F083LA05]に分類される特許

801 - 820 / 888

半導体記憶装置

【課題】 データ・セットアップタイムをメモリセルアレイの記憶容量によらずに一定の値とすることができる半導体記憶装置を提供する。

【解決手段】 この半導体記憶装置は、メモリセルアレイ10と、アドレス信号をデコードしてメモリセルアレイの行方向の制御を行う行デコーダ40と、アドレス信号をデコードしてメモリセルアレイの列方向の制御を行う列デコーダ50と、クロック信号に基づいてデータ制御信号を生成する制御部20と、データ制御信号に同期して複数ビットの入力データをラッチして列デコーダにそれぞれ出力する複数のラッチ回路を含むデータ入出力部61と、データ制御信号を伝送する配線の浮遊容量をビットラインの数に応じて調整するために、データ制御信号を伝送する第1の配線パターンの両側に隣接して設けられた複数の第2の配線パターンとを具備する。

(もっと読む)

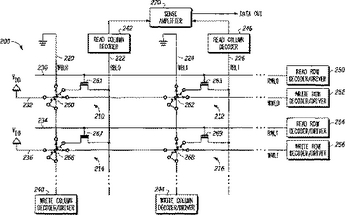

接地された書き込みビット・ライン及び電気的に絶縁された読み出しビット・ラインを有するMRAMアーキテクチャ

磁気抵抗ランダム・アクセス・メモリ(MRAM)アレイ(200)の各メモリ・セル(260、262、266、268)は、磁気抵抗トンネル接合部(MTJ)と、MTJに連結されたトランジスタ(261)とを有する。書き込みは、アレイの行及び列に沿う書き込みライン(220、232)により行なわれる。1組の書き込みライン(232、236)が、トランジスタに接続されていないMTJの端部に接続されている。従って、これらの書き込みラインは、MTJに近く、そのため、MTJに対する良好な磁気結合を有する。これは、書き込み電流を低く維持する上で重要である。これらの書き込みラインは、一方の端部において、ドライバ(240、252)によって駆動される。他方で、MTJに接続されていないメモリ・セルのトランジスタの端部に接続された読み出しビット・ライン(222)において、検出が行なわれる。書き込みドライバからの異なるライン上にセンス・アンプ(270)を有しているので、書き込みドライバ(240、252)のキャパシタンスによって検出に遅れが生じることはない。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】微細化されたMISFETのしきい値電圧のばらつきを低減する。

【解決手段】MISFET(Q1)のゲート電極9aは、素子分離溝2によって周囲を規定されたアクティブ領域Lの基板1上に形成され、アクティブ領域Lを横切ってその一端から他端に延在している。このゲート電極9aは、アクティブ領域Lと素子分離溝2との境界領域におけるゲート長がアクティブ領域Lの中央部におけるゲート長よりも大きく、全体としてH形の平面パターンで構成されている。また、このゲート電極9aは、アクティブ領域Lと素子分離溝2との境界領域のゲート長方向に沿った一辺の全体とゲート幅方向に沿った二辺の一部とを覆っている。

(もっと読む)

半導体集積回路装置の設計方法

【課題】 メモリアレイに接続された周辺回路を構成するトランジスタにおけるゲート酸化膜の膜厚を最適化し、FNストレスによるデバイス劣化を大幅に低減する。

【解決手段】 シミュレーションによって、MGドライバのトランジスタにおけるゲート印加電圧を算出し、設定されたゲート酸化膜厚と算出したゲート印加電圧から、ゲート酸化膜印加電界を計算する(ステップS101)。算出したゲート酸化膜印加電界とゲート酸化膜厚との関係から、FN劣化発生臨界電界線以上のトランジスタがあるかを検出し(ステップS102)、FN劣化発生臨界電界以上のトランジスタがある場合には、ゲート印加電圧を再設計してゲート酸化膜印加電界を再計算し(ステップS103)、FN劣化発生臨界電界以上のトランジスタがあるか検出し(ステップS104)、FN劣化発生臨界電界以上のトランジスタがない場合には、トランジスタの設計が終了となる。

(もっと読む)

半導体記憶装置及びメモリカード

【課題】 行選択回路における高耐圧のトランジスタの数を削減することにより、回路面積の縮小化を図った半導体記憶装置を提供する。

【解決手段】 半導体記憶装置は、複数のメモリブロックを有するメモリセルアレイであって、各メモリブロックに複数のメモリセルがマトリックス状に配置されているとともに、1又は複数のメモリセルを選択するための複数の第1選択ゲートトランジスタを有する、メモリセルアレイと、前記第1選択ゲートトランジスタの導通/非導通を制御する制御信号を、前記第1選択ゲートトランジスタのゲートに入力するための選択ゲート線であって、隣接する2つのメモリブロックで共有された、選択ゲート線と、入力されたアドレス信号で指定された行のメモリブロックを選択する、行選択回路と、を備える。

(もっと読む)

半導体装置およびその作製方法

【課題】製造時以外にデータの追記が可能であり、書き換えによる偽造等を防止可能な不揮発の有機メモリおよび当該有機メモリを有する半導体装置を提供することを目的とする。また、信頼性が高く、安価な半導体装置の提供を課題とする。

【解決手段】第1の方向に延びた複数のビット線と、第1の方向と垂直な第2の方向に延びた複数のワード線と、記憶素子部を備えたメモリセルと、複数のメモリセルからなるメモリセルアレイとを有し、記憶素子部は、ビット線を構成する導電層とワード線を構成する導電層との間に設けられた有機化合物層を有し、当該有機化合物層に、無機化合物と有機化合物とを混合して設けられた層を設けることを特徴としている。

(もっと読む)

半導体記憶装置

【課題】ソフトエラーフリーで、かつ高集積度のDRAMを安定して動作させる。

【解決手段】DRAMをSOI基板上に形成する。DRAMのセンスアンプ20、プリチャージ回路23、ビット線選択回路26A,26B、メモリセル27、ダミーセル28およびコラム選択回路29におけるトランジスタQn1,Qn2,Qp1,Qp2,Qpc,Qe,Qb,Qd,Qm,Qioのボディ領域を電気的に固定した。

(もっと読む)

磁気メモリデバイス用書込回路および磁気メモリデバイス

【課題】大きな抵抗値の書込線に対しても規定値の書込電流を供給する。

【解決手段】線路3a,3bを有する書込ビット線3の書込電流Iw1を定電流制御する電流制御回路51と、線路3a,3bの各開放側端部から書込電流Iw1を供給するトランジスタQ1,Q2と、各開放側端部から書込電流Iw1を電流制御回路51に出力するトランジスタQ3,Q4と、トランジスタQ3のオン時にトランジスタQ5,Q6をオフ、オンにしてトランジスタQ1,Q2をオフ、オンにし、トランジスタQ4のオン時にトランジスタQ5,Q6,Q1,Q2をそれぞれ逆の状態にする差動増幅回路61と、線路3aの開放側端部とトランジスタQ5のベースとの間に配設されたダイオードD1と、線路3bの開放側端部とトランジスタQ6のベースとの間に配設されたダイオードD2とを備えた。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】0.3μm未満の幅を有する素子分離領域によって電気的に分離された電界効果トランジスタの信頼性を向上させることのできる技術を提供する。

【解決手段】マスクROM領域のゲート長方向に隣接する電界効果トランジスタを電気的に分離する素子分離領域を、その電界効果トランジスタのゲート電極と同時に形成されるフィールドプレート分離によって構成する。これにより、素子分離領域の分離幅を0.3μm未満と相対的に狭くした場合でも、素子分離領域に挟まれた活性領域ACTに発生する応力を相対的に小さくすることができるので、応力を起因とする結晶欠陥の発生が緩和または抑制できて、電界効果トランジスタのソースとドレインとの間に所望しないリーク電流が具合を低減することができる。

(もっと読む)

磁気メモリデバイス

【課題】より低い電源電圧であっても情報の読み出しを行い得る磁気メモリデバイスを提供する。

【解決手段】(i+1)行(j+1)列(i,jは1以上の整数)で二次元状に配列された複数の記憶セル1を備えた磁気メモリデバイスであって、各記憶セル1には、2つの磁気抵抗効果発現体2a,2bがそれぞれ配設され、磁気抵抗効果発現体2a,2bの抵抗値を感知するための電流Ib1,Ib2を供給する前段回路41と、磁気抵抗効果発現体2a,2bに電流Iw1,Iw2を供給するX方向アドレスデコーダ回路32と、電流Ib1と電流Iw1との合計値、および電流Iw2と電流Ib2との合計値をそれぞれ一定に制御する電流制御回路(定電流回路25n)とを備えている。

(もっと読む)

半導体記憶装置

【課題】 本発明は、メモリセルから読み出されるデータの判定を正確に行うと共に、消費電力を低減することができる半導体記憶装置を提供することを目的とする。

【解決手段】 半導体基板20上に形成された埋め込み電極30と、埋め込み電極30上に埋め込み絶縁膜40を介して形成された半導体層45と、半導体層45上に絶縁膜60を介して形成された表面電極70と、半導体層45の両端部に所定間隔を空けて形成されたソース領域80及びドレイン領域90と、ソース領域80及びドレイン領域90の間に形成されたフローティングボディ50とを有し、フローティングボディ50にホールが蓄積されているか否かによってデータを記憶することを特徴とする。

(もっと読む)

半導体記憶装置

【課題】書き込み電流の低減を図る事が可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1の方向に延在された第1の延在部と、第1の延在部と一端がつながりかつ第1の方向に対して第1の斜め方向に延在された第1の斜め延在部20と、第1の斜め延在部の他端と一端がつながりかつ第1の方向に延在された第2の延在部とを有する第1の書き込み配線と、第1の方向と異なる第2の方向に延在された第4の延在部と、第4の延在部と一端がつながりかつ第2の方向に対して第3の斜め方向に延在された第3の斜め延在部30と、第3の斜め延在部の他端と一端がつながりかつ第2の方向に延在された第5の延在部とを有する第2の書き込み配線と、少なくとも一部が第1及び第3の斜め延在部20,30に挟まれて配置された磁気抵抗素子10とを具備する。

(もっと読む)

表示装置及びそれを用いた電子機器

【課題】不揮発性であって、データの追記が可能で、作製工程が増加することがない記憶回路を有する表示装置、表示装置を用いた電子機器の提供を課題とする。

【解決手段】一対の導電層間に有機化合物層が挟まれた簡単な構造の記憶素子からなる記憶回路を有する表示装置を提供する。上記構成を有することにより、不揮発性であって、データの追記が可能で、作製工程が増加することがない記憶回路を有する表示装置を提供することができる。

(もっと読む)

基準磁気抵抗を有する磁気ランダムアクセスメモリ及びその読出し方法

【課題】 基準磁気抵抗を有する磁気ランダムアクセスメモリを提供すること。

【解決手段】 磁気ランダムアクセスメモリは、反強磁性層(12)とその上に形成されたピン層(13)とその上に形成されたトンネルバリア層(14)とその上に形成された自由層(15)を備える少なくとも一つの磁気メモリセルを含む。ピン層(13)と自由層(15)は、基準磁気抵抗状態を形成するように直交配置される。提供されたMRAM構造によって、アクセス精度が大幅に増加され且つアクセス速度が加速される。

(もっと読む)

強誘電体メモリ装置

【課題】非破壊読み出しであって、高速化、高集積化、長寿命化を実現できる強誘電体メモリ装置の提供。

【解決手段】この発明は、メモリセルを有する強誘電体メモリ装置であり、そのメモリセルは、埋め込み酸化膜層を有するシリコン・オン・インシュレータ基板に形成された電界効果型トランジスタからなる。その電界効果型トランジスタの1対のソース・ドレインに挟まれたチャネル領域と制御用ゲート電極との間には、強誘電体薄膜102が配置されている。かつ、その電界効果型トランジスタのボディ105の電位を制御するボディプレート線106を備えている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置、例えば、SRAMのメモリセルのソフトエラーを低減させた高性能の半導体集積回路装置を提供する。

【解決手段】それぞれのゲート電極とドレインとが交差接続された一対のnチャネル型MISFETを有するSRAMメモリセルの、交差接続部の配線MD2の表面を酸化シリコン膜21の表面より突出した形状とし、この配線MD2上に、容量絶縁膜となる窒化シリコン膜23と、上部電極24を形成する。この配線MD2、窒化シリコン膜23および上部電極24とで容量Cを形成することができ、α線によるソフトエラーを低減することができる。また、配線MD2側壁にも容量を形成することができるため、容量の増加を図ることができる。

(もっと読む)

半導体記憶装置

【課題】 従来の半導体記憶装置においてダミービット線を複数用いて構成するレプリカ回路では、半導体製造技術の微細化によりトランジスタのオフリーク電流が増加したため、ダミービット線を充電する際にオフリーク電流により所望の電位に充電できなくなった。この結果、ダミービット線への充電時間あるいは放電時間も所望の時間とは異なるため、最適な動作タイミングの設定が出来ない。

【解決手段】 ダミーメモリセルアレイにおいて、第1のダミービット線25はドレイン領域21とダミービット線25とを接続するため、コンタクトおよびビアホール28〜30とメタル電極23,24を介して接続され、第2のダミービット線46はドレイン領域47とコンタクトしない構成とする。

(もっと読む)

半導体チップ

【課題】半導体チップのソフトエラー免疫セル構造を提供する。

【解決手段】ディープNウェル領域107中にメモリデバイスが形成される。メモリデバイスはメモリセルを含む。メモリセルは第1の記憶ノードおよび第2の記憶ノードを含む。メモリセルは、それぞれ第1の記憶ノードおよび第2の記憶ノードと電気的に結合された第1の抵抗および第2の抵抗を含む。メモリセルは、それぞれ第1の記憶ノードおよび第2の記憶ノードと電気的に結合された第1のキャパシタおよび第2のキャパシタを含む。ILD層219はメモリデバイス上に形成される。ILD層219は少なくともホウ素を含まない誘電体材料を含む。IMD層221はILD層219上に形成される。IMD層221の誘電率は3より小さい。ポリイミド(Polyimide)層240はIMD層221上に形成される。ポリイミド層の厚みは20μmより小さい。

(もっと読む)

半導体記憶装置

【課題】 本発明は、歩留まりを向上させることができる半導体記憶装置を提供することを目的とする。

【解決手段】 メモリセルアレイにおけるロウ方向に沿って配置され、不良メモリセルを救済するためのリダンダンシーメモリセルからなる少なくとも1つのリダンダンシーワード線と、外部から与えられたロウアドレスと、内部に予め格納されている不良メモリセルアドレスのロウアドレスとを比較し、両者が一致すると判定した場合には、リダンダンシーロウデコーダを活性化すると共に、ロウアドレスに所定のアドレス変換を施して出力するリダンダンシー判定回路と、リダンダンシー判定回路から与えられたロウアドレスに基づいて、所望のリダンダンシーワード線を選択するリダンダンシーロウデコーダとを備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】消去セルの閾値電圧の変化を抑制することが困難であった。

【解決手段】メモリセルアレイ1は、第1、第2乃至第nの状態からなるn値(nは2以上の自然数)を記憶する複数のメモリセルがマトリックス状に配置されている。制御回路7は、メモリセルアレイ1のj値(j<n)のデータが記憶されている第1メモリセルに、次の少なくとも1値のデータを記憶する前に、第1メモリセルに隣接する少なくとも1つの第2メモリセルが第1の状態であり、第1の閾値電圧に達していない場合、第1の閾値電圧まで書き込み動作を行なう。

(もっと読む)

801 - 820 / 888

[ Back to top ]