Fターム[5F083LA11]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019)

Fターム[5F083LA11]の下位に属するFターム

Fターム[5F083LA11]に分類される特許

221 - 222 / 222

半導体装置

【課題】 サージ耐量が大きな半導体装置を提供する。

【解決手段】 このDRAMでは、シリコン基板20の表面に、内部保護回路9の抵抗素子であるn+ 型拡散抵抗領域8に近接してその周囲にn型ウェル領域NWを形成し、n型ウェル領域NWの表面にn+ 型拡散領域33を形成し、n+ 型拡散領域33に接地電位GNDを与える。したがって、n+ 型拡散抵抗領域8からシリコン基板20中に漏れたサージ電流をn+ 型拡散領域33に吸収させることができるので、サージ電流を吸収する能力が向上する。

(もっと読む)

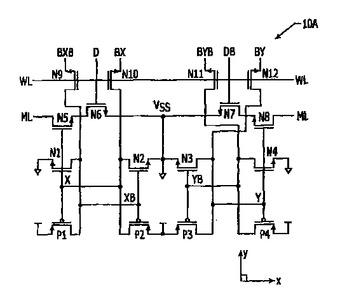

小さいフットプリントおよび効率的なレイアウトアスペクト比を有するターナリ検索機能付きメモリ(TCAM)セル

スケーラビリティを高める効率的なレイアウトアスペクト比および極めて小さいレイアウトフットプリントサイズを有するターナリCAMセルが提供される。また、セルは、ビット線、データ線、マッチ線に対する高い歩留りの相互接続を容易にする高度の対称性も有している。16TターナリCAMセルは、セルの第1の側に隣接して延びる第1および第2の対のアクセストランジスタと、セルの第2の側に隣接して延びる第1および第2の対の交差結合インバータとを有している。また、4T比較回路の第1及び第2の半分部位も設けられている。4T比較回路の第1の半分部位は、第1の対のアクセストランジスタと第1の対の交差結合インバータとの間で延びるように位置されている。同様に、4T比較回路の第2の半分部位は、第2の対のアクセストランジスタと第2の対の交差結合インバータとの間で延びるように位置されている。

(もっと読む)

(もっと読む)

221 - 222 / 222

[ Back to top ]