Fターム[5F083LA11]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019)

Fターム[5F083LA11]の下位に属するFターム

Fターム[5F083LA11]に分類される特許

161 - 180 / 222

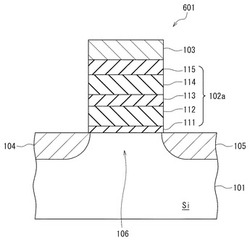

MOS型半導体メモリ装置

【課題】優れたデータ保持特性と、高速でのデータ書換え性能と、低消費電力での動作性能と、高い信頼性と、を同時に兼ね備えた不揮発性MOS型半導体メモリ装置を提供する。

【解決手段】MOS型半導体メモリ装置601は、大きなバンドギャップを持つ第1の絶縁膜111および第5の絶縁膜と、最も小さなバンドギャップを持つ第3の絶縁膜113との間に、両者の中間の大きさのバンドギャップを持つ第2の絶縁膜112および第4の絶縁膜114を備えている。このようなエネルギーバンド構造を有することにより、データ書き込み時には第1の絶縁膜111を介した電荷の移動が起こりやすく、書き込み動作速度を高速化することが可能で、かつ絶縁膜積層体に電荷を注入するために必要な書き込み電圧を小さく抑えることができる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】補助パターンでダミーコンタクトが形成されてもゲート電極SGとの間で短絡不良が発生するのを防止できるNAND型フラッシュメモリ装置等の半導体記憶装置を提供する。

【解決手段】ビット線コンタクト4a(CB)の形成時にマスクパターンに補助パターン4b、4cを形成する場合に、メモリセル領域MAから延長して形成される補助パターン4bの端部に位置する補助パターン4cの対応領域について、ビット線コンタクト4a(CB)を形成する領域のスペーサを除去するのと同時にその部分のスペーサを除去する。ゲート電極SLG−SLGの間のパターンニングに余裕を持たせることができ(オフセットを確保することができ)、解像した補助パターン4cの部分でダミーコンタクトホールが形成された場合でも、両脇のゲート電極SLGとの間で短絡不良が発生するのを防止することが出来る。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル間の容量結合を低減して浮遊ゲート間干渉を抑制することができる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体基板10、半導体基板10上に形成された第1の絶縁膜11、半導体基板10上に第1の絶縁膜11を介して形成された浮遊ゲート12、この浮遊ゲート12上に形成された第2の絶縁膜13及び浮遊ゲート上に第2の絶縁膜13を介して形成された制御ゲート14を有する複数のメモリセルMCと、半導体基板10に形成されゲート幅方向に隣接するメモリセルMC間を分離するゲート長方向に延びる素子分離絶縁膜17と、素子分離絶縁膜17の上で且つゲート幅方向に隣接する浮遊ゲート12間に形成された空隙部22とを有する。

(もっと読む)

不揮発性メモリ素子及びその動作方法

【課題】NOR型フラッシュメモリのドレイン外乱と過消去を防止する不揮発性メモリ素子及びその動作方法を提供する。

【解決手段】半導体基板105と、半導体基板105上の第1制御ゲート電極135と、半導体基板105と第1制御ゲート電極135との間に介在された第1電荷保存層125と、第1制御ゲート電極135の一側の半導体基板105に画定されたソース領域140と、第1制御ゲート電極135の他側に配され、半導体基板105の内部にリセスされて形成された第1補助ゲート電極115と、第1制御ゲート電極135の反対側の第1補助ゲート電極115の一側の半導体基板105に画定された第1ドレイン領域145と、第1ドレイン領域145に連結されたビットライン160と、を備える不揮発性メモリ素子である。

(もっと読む)

プログラムボリュームの間に位置する熱的伝導体を含むメモリ装置

【課題】セル間の熱的干渉を減少させるメモリ装置を提供する。

【解決手段】第1方向に延長された複数のビット線BL0〜BL3と、第1方向と交差する第2方向に延長された複数のワード線WL0,WL1と、ビット線とワード線の間に電気的に連結された、データを書き込むことができる領域であるプログラムボリュームの配列からなるアレイ152と、アレイを構成するプログラムボリュームの間に位置し、第1方向および第2方向の少なくとも一つの方向に延長された、熱的伝導性を有し、ストライプ状の形態を有する、熱的伝導性ストライプパターン172と、を含む。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】低いビットラインコンタクト抵抗を有する不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】第1及び第2フィン105a,105bを備え、第1導電型を有する半導体基板と、第1及び第2フィンの一端を連結する共通ビットライン電極160a,160bと、第1及び第2フィン105a,105bの一側面を覆い、第1及び第2フィン上を横切って延びる複数の制御ゲート電極150と、共通ビットライン電極160a,160bと複数の制御ゲート電極150との間に配置され、第1及び第2フィン105a,105bの一側面を覆い、第1及び第2フィン上を横切って延びる第1ストリング選択ゲート電極155aと、第1ストリング選択ゲート電極と複数の制御ゲート電極との間に配置され、第1及び第2フィンの一側面を覆い、第1及び第2フィン上を横切って延びる第2ストリング選択ゲート電極155bと、を備える不揮発性メモリ素子である。

(もっと読む)

不揮発性記憶素子の形成方法

【課題】セル特性の分散を減少させることができるNAND型フラッシュメモリ不揮発性記憶素子の形成方法を提供する。

【解決手段】広い間隔で配列された第1マスクパターン120d、120c、120sを形成した後に、間隔調節膜130をコンフォーマルに形成し、間隔調節膜130により第1マスクパターン120d、120c、120sの間に各々定義される溝132、134を充填する第2マスクパターン140c、140gを形成する。これにより、接地選択ゲートライン140g、セルゲートライン140c及びストリング選択ゲートライン120sが全て等間隔で配列されるように形成することができる。

(もっと読む)

不揮発性メモリ素子及びその動作方法

【課題】動作信頼性が高くて高集積化が可能である不揮発性メモリ素子及びその動作方法を提供する。

【解決手段】不揮発性メモリ素子は半導体基板110aを含み、電荷保存層120は、半導体基板上110aに提供され、例えばポリシリコン、金属、シリコン窒化膜、量子ドット、またはナノクリスタルを含むことができ、制御ゲート電極140は、電荷保存層140上に提供され、第1補助ゲート電極130aと第2補助ゲート電極130bは、電荷保存層140の一側に離隔配置され、半導体基板110aから絶縁される。この不揮発性メモリ素子によれば、メモリトランジスタ内部にソース及びドレイン領域が省略され、代わりに第1補助ゲート電極130a及び第2補助ゲート電極130bが配され、不純物ドーピングによるソース及びドレイン領域より微細線幅に形成され、従って不揮発性メモリ素子の集積度向上に寄与できる。

(もっと読む)

半導体記憶装置

【課題】従来のメモリセルプレート及び周辺回路のレイアウトにおいて、カラム選択信号線の配線パターンを変えることにより、メモリセルプレート上で隣接するビット線同士の干渉を防ぐことのできる半導体記憶装置を提供すること。

【解決手段】メモリセルプレート11上において、カラム選択信号線20によって選択され同時に動作するビット線対BL0,/BL0,BL2,/BL2の間に別のカラム選択信号線21に対応するビット線対BL5,/BL5(BL0,/BL0,BL2,/BL2とは同時動作しないもの)が配置されるようにカラム選択信号線20,21の配線レイアウトを規定することで、隣接ビット線間の線間容量による容量カップリングの影響を防ぎ、書き込み特性を向上させることを可能とした。

(もっと読む)

不揮発性メモリ素子及びその動作方法

【課題】電荷保存層を利用してデータを保存しうる、立体型構造を有する不揮発性メモリ素子及びその動作方法を提供する。

【解決手段】不揮発性メモリ素子は、半導体層105と、半導体層105上に配列された複数の上部制御ゲート電極130aと、半導体層105の下に配列され、複数の上部制御ゲート電極130aと交互に配置された複数の下部制御ゲート電極130bと、半導体層105と上部制御ゲート電極130aとの間にそれぞれ介在された複数の上部電荷保存層120aと、半導体層105と下部制御ゲート電極130bとの間にそれぞれ介在された複数の下部電荷保存層120bと、を備える。

(もっと読む)

半導体記憶装置

【課題】複数のメモリセルと、前記メモリセルとビット線を介して接続されるローカル読出データ増幅回路とを備えるSRAMにおいて、複数のメモリセルと、ローカル読出データ増幅回路との間にMWELL分離領域や個別の基板コンタクト領域などを設けると、面積が大きくなる。一方、プロセスの微細化が進むに従って、ローカル読出増幅回路のレイアウトと、メモリセルアレイとが光学ダミー領域や基板コンタクト領域を超えて、露光工程で相互に干渉し、デバイスのバラつきが大きくなり、歩留まり低下を引き起こす。

【解決手段】複数のメモリセルと、前記メモリセルとビット線を介して接続されるローカル読出データ増幅回路との境界に存在するMWELL分離領域や、基板コンタクト部を共有し、ゲート電極の配置方向をメモリセルと同一にすることで、省面積化や製造工程での歩留まり低下を抑制する。

(もっと読む)

半導体記憶装置

【課題】チップの中央に周辺回路が集中配置されたフロアプランを有する半導体記憶装置において、入出力データ幅による回路特性の変化を抑制する。

【解決手段】バス領域121,122と、中心線Aに沿って配置された第3のバス領域123と、辺101とバス領域121との間に配置されたセル領域111と、辺102とバス領域122との間に配置されたセル領域112と、バス領域121,122間に配置され、バス領域123から見て辺103,104側にそれぞれ配置されたセル領域113,114と、バス領域123に沿って配置されたデータ入出力パッド列DQ0〜DQ15とを備える。本発明によれば、入出力データ幅を変更してもデータ入出力バスの遠近端差はほとんど変化しない。したがって、選択された入出力データ幅によって特性が変化しにくく、優れた回路特性を得ることが可能となる。

(もっと読む)

不揮発性半導体メモリ及びその動作方法

【課題】電荷蓄積層に対するホットホールの注入効率を向上させるNMOSトランジスタ型の不揮発性半導体メモリを提供する。

【解決手段】NMOSトランジスタ型の不揮発性半導体メモリは、P型シリコン層20中にソース/ドレインとして形成された第1及び第2N型拡散層21,22と、第1及び第2N型拡散層21,22に挟まれたチャネル領域CNL上に絶縁膜30を介して形成されたゲート電極50と、その絶縁膜30中に形成された電荷蓄積層40とを備える。第1N型拡散層21から第2N型拡散層22へ向かう方向は、P型シリコン層20の結晶方位<100>である。データ書き換え時、ホットホールが絶縁膜30のポテンシャル障壁を超えて電荷蓄積層40に注入される。

(もっと読む)

不揮発性半導体メモリ及びその動作方法

【課題】電荷蓄積層に対するホットエレクトロンの注入効率を向上させるPMOSトランジスタ型の不揮発性半導体メモリを提供する。

【解決手段】PMOSトランジスタ型の不揮発性半導体メモリは、N型シリコン層20中にソース/ドレインとして形成された第1及び第2P型拡散層21,22と、ソース21及びドレイン22に挟まれたチャネル領域CNL上に絶縁膜30を介して形成されたゲート電極50と、チャネル領域CNLとゲート電極50との間の絶縁膜30中に形成された電荷蓄積層40とを備える。ソース21からドレイン22へ向かう方向は、N型シリコン層20の結晶方位<100>である。

(もっと読む)

半導体集積装置

【課題】SOI基板内の埋め込み酸化膜を薄膜化しても、デバイス特性が劣化することがなく、バイポーラトランジスタも形成可能な半導体集積回路を提供する。

【解決手段】SOI基板3内の埋め込み酸化膜2の上面には、FBC4、NFET5およびPFET6が互いに分離して形成されている。FBC4の下方に位置するp支持基板1内には、埋め込み酸化膜2に接してnウェル拡散領域7が形成されている。NFET5の下方に位置するp支持基板1内には、pウェル拡散領域8が形成されている。PFET6の下方に位置するp支持基板1内には、nウェル拡散領域9が形成されている。NFET5とPFET6の形成箇所に合わせて、埋め込み酸化膜2の下面側にそれぞれpウェル拡散領域8とnウェル拡散領域9を形成して、各ウェル拡散領域にそれぞれ所定の電圧を印加するため、NFET5とPFET6にバックチャネルが形成されなくなり、デバイス特性がよくなる。

(もっと読む)

NANDメモリーアレイおよびNANDフラッシュアレイ

【課題】ストラップされたストリング選択ラインを持つフラッシュメモリー装置を提供する。

【解決手段】NANDメモリーアレイは、第1選択ラインに連結された第1選択トランジスターと、第2選択ラインに連結された第2選択トランジスターと、ワードライン等に各々連結され、第1及び第2選択トランジスターの間に直列に連結されたメモリーセル等と、そして、第1選択ラインに電気的に連結されたストラッピングラインを含む。

(もっと読む)

ReRAM

【課題】ReRAMに関し、電極(ビア)及びReRAM素子の配置構造に簡単な改変を加え、微細化すべきメモリセル選択トランジスタアレイには所要の加工ルールを適用して加工し、且つ、ReRAM素子には別の加工ルールを適用して加工することを可能にし、ReRAM素子の間隔がルール違反にならないようにする。

【解決手段】ワード線WL(ゲート)で代表されるメモリセル選択トランジスタ上に形成された多層メタル配線層M1・・・・と、多層メタル配線層M1・・・・の上層に在って且つ素子ピッチPR が前記多層メタル配線層M1・・・・の下層に在る配線のピッチPL に比較して広いピッチで形成されたReRAM素子7を備える。

(もっと読む)

不揮発性記憶装置及びその動作方法

【課題】不揮発性記憶装置及びその動作方法を提供する。

【解決手段】本発明の装置は、n番目のビットラインに連結された第1トランジスターと、n+1番目のビットラインに連結された第2トランジスターとを含む。前記第1トランジスター及び前記第2トランジスターは、n番目のビットラインとn+1番目のビットラインとの間に直列に連結される。記憶セルのソース領域及びドレーン領域の構造が同一または類似の2トランジスター1ビット単位セルを有する不揮発性記憶装置を形成できる。また、2トランジスター2ビット単位セルを有することができるために記憶容量が2倍に増加できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 素子構造の微細化・低駆動電圧化によって顕在化したMOSFETの閾値のバラつきによる、DRAMのリフレッシュ不良を抑制する。

【解決手段】 DRAMにおいて、セルトランジスタのバックゲートに印加するバックバイアス電位の設定値を記録する第1の手段と、第1の手段に記録された前記バックバイアス電位の設定値に基づいてバックバイアス電位を生成して、生成したバックバイアス電位を前記バックゲートに供給する第2の手段とを有し、セルトランジスタと同一構造で且つ同一工程で同時に製作されたMOSFETの閾値が、セルトランジスタが具備すべき目標値より大きい場合に、前記目標値に対するバックバイアス電位より浅い値が第2の手段に記録されてなる。

(もっと読む)

161 - 180 / 222

[ Back to top ]