Fターム[5F083LA11]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019)

Fターム[5F083LA11]の下位に属するFターム

Fターム[5F083LA11]に分類される特許

141 - 160 / 222

半導体装置およびその製造方法

【課題】素子分離領域の深さを抑制しながら耐圧の低下を抑制できるNAND型フラッシュメモリ等の半導体装置を提供する。

【解決手段】ゲート電極PGが、隣り合う素子分離膜間のアクティブエリアAA上にゲート絶縁膜11を介してゲート長方向に離間して並設されている。ゲート電極PGを構成する多結晶シリコン層14は、アクティブエリアAAの片脇に位置する素子分離膜の上面上に張り出す一端部14aと、アクティブエリアAAの逆脇に位置する素子分離膜の上面上に張り出す他端部14bとを備えており、一端部14aの長さL1と一端部14bの長さL2が互いに異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト歩留を向上させる、スタックドコンタクト構造を有する半導体装置を提供する。

【解決手段】NAND型フラッシュメモリのビット線コンタクトには、スタックドコンタクトを構成する第1のコンタクト開口部CH1、第2のコンタクト開口部CH2a、及び第3のコンタクト開口部CH2bが設けられる。下層の第1のコンタクト開口部CH1はビット線コンタクトの中央部に配置され、上層の第2のコンタクト開口部CH2aはビット線コンタクトの左部に配置され、その中心位置がビット線コンタクトの中心位置に対して第2のコンタクト開口部CH2aのズレ量だけ左方向に配置され、上層の第3のコンタクト開口部CH2bはビット線コンタクトの右部に配置され、その中心位置がビット線コンタクトの中心位置に対して第3のコンタクト開口部CH2bのズレ量だけ右方向に配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】歪みの少ないゲート電極を有するEEPROMやNANDフラッシュメモリ等の半導体装置およびその製造方を提供する。

【解決手段】半導体基板11と、半導体基板11の主面に、第1ゲート絶縁膜12を介して形成された第1ゲート電極13と、第1ゲート電極13上に第2ゲート絶縁膜16を介して形成された第2ゲート電極17と、第2ゲート電極17上に形成されるとともに、中央部が外周部より厚く、且つ第2ゲート電極17内に2段凸状に突出したシリサイド膜18と、第1ゲート電極13と、第2ゲート電極17と、シリサイド膜18の側壁にそれぞれ形成された酸化膜21と、第1ゲート電極13および第2ゲート電極17を挟むようにゲート長方向に沿って形成されたソースドレイン不純物層19と、を具備する。

(もっと読む)

半導体記憶装置

【課題】アナログ周辺回路に用いられる抵抗素子の材料などが設計変更されても、他の部分への設計変更が波及しない半導体記憶装置を提供する。

【解決手段】第1の絶縁膜12上に形成された第1の導電体13と、第1の導電体13上に形成され第1の開口19を有する第2の絶縁膜14と、第2の絶縁膜14上に形成され第1の開口19を介して第1の導電体13と導通する第2の導電体20と、第2の導電体20の上に形成された第3の絶縁膜21と、第3の絶縁膜21を貫通し第2の導電体20に導通する第1のコンタクト23と、第3の絶縁膜21と第2の絶縁膜14とを貫通して第1の導電体13と導通する第2のコンタクト22と、を有する抵抗素子を有する。配線の存在する層とは異なる層に存在する第2の絶縁膜14の有する第1の開口19の位置を変更すれば、第1のコンタクト23と第2のコンタクト22との間の抵抗値を変更することができる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】安価に高集積化された不揮発性半導体記憶装置、及び製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板Baに対して垂直方向に延びるメモリ柱状半導体層34と、メモリ柱状半導体層34と絶縁層を挟み形成された第1〜第4ワード線導電層32a〜32dと、メモリ柱状半導体層34の上面に接して形成されたドレイン側柱状半導体層47と、ドレイン側柱状半導体層47からゲート絶縁層46を介して形成されてロウ方向に延びるドレイン側導電層42とを備える。第1〜第4ワード線導電層32a〜32dのロウ方向の端部は、階段状に形成されている。ドレイン側ゲート導電層42の全体は、第4ワード線導電層32dの直上の領域90に形成されている。第1〜第4ワード線導電層32a〜32d及びドレイン側導電層42は、それらに亘って連続して形成された保護絶縁層35にて覆われている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した動作の積層型不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】電気的に書き換え可能なメモリセルが複数形成されるメモリセル領域と、メモリセルを制御する周辺回路を構成するトランジスタが形成される周辺回路領域とを備え、メモリセル領域には、半導体基板11上に対し垂直方向に、ソース側選択トランジスタ層20、メモリトランジスタ層30、及びドレイン側選択トランジスタ層40が積層されて形成される。メモリホール34内には、ブロック絶縁層(第1絶縁層)35、電荷蓄積層(特性変化層)36、トンネル絶縁層37、及びメモリ柱状半導体層38が形成される。周辺回路領域には、p−型領域101Aにプレーナ型トランジスタのソース/ドレイン領域101Bが形成され、メモリセル領域の複数の導電層の各々と同一平面上に形成され、且つ導電層と電気的に分断される複数のダミー配線層100が形成される。

(もっと読む)

フラッシュメモリ及びその製造方法

【課題】30nm以下の微細化に適応できるフラッシュメモリ及びその製造方法を提供する。

【解決手段】基板101に接続された上部にスペーサ絶縁膜116を有するフィン構造のビットラインから形成されたメモリセル部の最小加工寸法をFとするとき、独立に書き込み/消去可能なビットライン2本が対になって4F周期に配置されてメモリセル部が形成され、一対のフィンの上部を覆うように記憶絶縁膜が形成されている。

(もっと読む)

半導体装置およびその製造方法およびその駆動方法

【課題】サイリスタ動作時に、寄生バイポーラトランジスタを作らせず、書き込みのディスターブの発生を防止して、誤書き込みを防止することを可能にするSRAM型の半導体装置とその製造方法を提供する。

【解決手段】半導体基板11に形成されたサイリスタ形成領域21を分離する素子分離領域12と、サイリスタ形成領域21に形成されていて、p型の第1領域(第1p型領域)p1と、n型の第2領域(第1n型領域)n1と、p型の第3領域(第2p型領域)p2と、n型の第4領域(第2n型領域)n2とが順に接合されたサイリスタT1、T2と、第2p型領域p2の下部に形成されたn型の第5領域(第1ウエル領域)31を有する半導体装置1において、第5領域31の底部および素子分離領域12の下部に接合するp型の第6領域(第2ウエル領域)32を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

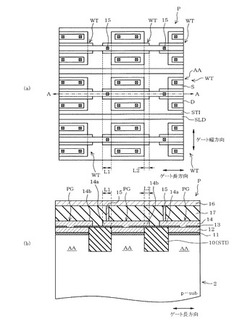

【課題】メモリセルアレイのサイズを縮小することができる不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板1上にx方向を長手方向として形成された素子領域10と素子分離領域20とを備える。また、素子領域10に形成されたセルトランジスタCTとこのセルトランジスタCTを選択するための選択トランジスタSTとを含むメモリセルMCを備える。y方向に並んで配列された複数のメモリセルMCに共通に接続されy方向に延びるように制御ゲート線CGLが配列され、制御ゲート線CGLは素子領域10上では第1の幅D2を有する一方素子分離領域20上では第1の幅D2より広い第2の幅D1を有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作特性を向上させるNAND型フラッシュメモリ半導体記憶装置、及び、活性領域側壁への不純物打ち込みに関するその製造方法を提供する。

【解決手段】メモリMOSトランジスタが配置される第1活性領域と、周辺MOSトランジスタが配置される第2活性領域と、半導体基板10中に形成され、側壁において第1活性領域が露出される第1トレンチ43と、第1トレンチ43内を埋め込む絶縁膜を備え、隣接する第1活性領域間を電気的に分離する第1素子分離領域と、半導体基板10中に形成され、側壁において第2活性領域が露出される第2トレンチ43と、第2トレンチ43内を埋め込む絶縁膜27を備え、隣接する第2活性領域間を電気的に分離する第2素子分離領域35とを具備し、第2活性領域の不純物濃度は中心部より高く、第1活性領域AAの不純物濃度は中心部と等しい。

(もっと読む)

不揮発性半導体記憶装置

【課題】高電圧を支障なく転送することを可能にする。

【解決手段】転送トランジスタQNiのドレイン拡散領域201a、ソース拡散領域201bの上方に位置する配線301aは、短絡配線302によりゲート電極203と短絡されてダミー配線とされている。これにより、転送トランジスタQNiによる高電圧の転送時において、ドレイン拡散領域201a、ソース拡散領域201bの空乏化を防止することができ、高電圧を支障なく転送することが可能になる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】ワード線の間の耐圧性が十分なNAND型EEPROM等の不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板10と、この半導体基板10上に形成された第1の絶縁膜11と、半導体基板10上に前記第1の絶縁膜11を介して形成された浮遊ゲート12と、浮遊ゲート12上に形成された制御ゲート14と、少なくとも前記浮遊ゲート12と制御ゲート14の間、並びに浮遊ゲート12及び制御ゲート14のワード線WLに沿った側面を同一絶縁膜素材によって連続的に被膜されている第2の絶縁膜13とを備えた複数のメモリセルを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】安価に高集積化された且つ信頼性の低下を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、電気的に書き換え可能な複数のメモリセル、及び複数の選択トランジスタが直列に接続された複数のメモリストリングスMSを有する。メモリストリングスMSは、基板Baに対して垂直方向に延びるメモリ柱状半導体層34と、メモリ柱状半導体層34との間に電荷蓄積層36を挟むように形成された第1〜第4ワード線導電層32a〜32dと、メモリ柱状半導体層34の下部に接し且つ基板Baに対して垂直方向に延びるソース側柱状半導体層26と、ソース側柱状半導体層26との間に電荷蓄積層27を挟むように形成されると共にロウ方向に所定ピッチの間隔を設けてライン状に繰り返し設けられたソース側導電層22とを備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】Fin型構造を採用した半導体記憶装置においてカップリング比の各メモリセル間のバラつきを抑制する。また複数のアクティブエリア間のリーク電流を抑制する。

【解決手段】シリコン基板2の主表面高さは均一に形成されていると共にシリコン酸化膜3の上面高さは均一に形成されている。シリコン酸化膜3がSIMOX法により形成され、アクティブエリアSaがシリコン酸化膜3の上面上まで達する素子分離溝2gによって複数に分断されている。したがって、素子分離溝2gの深さおよびアクティブエリアSaの高さを各メモリセル間でほぼ等しい高さに調整でき、隣り合うアクティブエリアSa−Sa間がシリコン酸化膜3によって互いに電気的に絶縁状態に保たれる。

(もっと読む)

半導体記憶装置

【課題】メタルブリッジを用いることなく、面積効率の良い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、強誘電体キャパシタCおよびセルトランジスタTを有するユニットセルMCと、複数のユニットセルを直列に接続したユニット直列構造のうち隣接する2つのユニット直列構造USC間に直列に接続された2つのデプレーション型トランジスタDT1、DT2および2つのエンハンスメント型トランジスタET1、ET2と、エンハンスメント型トランジスタおよびデプレーション型トランジスタの各ゲートに接続された4本の選択線BS1〜BS4と、エンハンスメント型トランジスタまたはデプレーション型トランジスタとビット線との間を接続するビット線コンタクトBLCとを備え、隣接するビット線において、一方のビット線に接続するビット線コンタクトおよび他方のビット線に接続するビット線コンタクトは、1本の選択線に関して互いに反対側に位置する。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の

端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

半導体装置

【課題】横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制されたフローティングゲート電極を有する不揮発性メモリの半導体装置を提供する。

【解決手段】メモリセルの周囲に設けられた第1遮光壁50により画定された第1被遮光領域10Aと、メモリセルの周囲に設けられた第2遮光壁により画定された第2被遮光領域10A´と、第1遮光壁50に設けられた第1開孔52と、第2遮光壁に設けられ第1開孔52と対向して位置する第2開孔52´と、メモリセルと接続され、第1開孔52から第1被遮光領域10Aの外側に引き出された第1配線層24a,24b,24cと、メモリセルと接続され、第2開孔52´から第2被遮光領域10A´の外側に引き出された第2配線層24a´,24b´,24c´と、少なくとも、第1被遮光領域10Aと第2被遮光領域10A´とに挟まれた領域の上方に設けられた遮光膜と、を含む。

(もっと読む)

半導体装置

【課題】ノイズマージンを拡大可能な半導体装置を提供する。

【解決手段】例えば、各メモリセルMCが第1ポート用のワード線WLAと第2ポート用のワード線WLBに接続され、複数のメモリセルMCがマトリクス状に配置されたメモリ領域において、各ワード線を、WLA0、WLB0、WLB1、WLA1、WLA2、…といった順番で配置する。更に、WLA−WLA間およびWLB−WLB間のピッチd2をWLA−WLB間のピッチd1よりも小さくする。このように、あるワード線を基準にその両側の一方にピッチd2で同一ポートのワード線が配置され、他方にピッチd1で異なるポートのワード線が配置されるような構成を用いることで、例えば、WLAとWLBを交互に配置するような場合と比較して、小面積で異なるポート間の干渉を低減でき、ノイズマージンの拡大が可能となる。

(もっと読む)

半導体装置

【課題】ビアホールの位置が大きくシフトした場合でも、層間絶縁膜に形成されるボイドとの接触を確実に防止して、高い信頼性および高い歩留まりを確保できる半導体装置を提供する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜の下側に配置された下側配線層と、層間絶縁膜の上側に配置された上側配線層と、層間絶縁膜を貫通して、下側配線層に属する配線と上側配線層に属する配線を電気接続するためのビアホールとを備える。下側配線層において、所定の方向に沿って延びる複数の配線ラインと、少なくとも2つの配線ラインの部分的連結によって形成され、ビアホールと接触するためのコンタクト領域とが設けられる。互いに隣接した配線ライン間に位置する層間絶縁膜には、ボイドが存在しており、一方、コンタクト領域におけるビアホールの接触部分と、コンタクト領域に隣接する配線ラインとの間に位置する層間絶縁膜にはボイドが存在していない。

(もっと読む)

半導体記憶装置

【課題】チップ面積の増大を抑えてパッドから離れた回路に十分な電源を供給することが可能な半導体記憶装置を提供する。

【解決手段】メモリセルアレイは、複数のメモリセルが行及び列に配置され、行にワード線が配置され、列にビット線が配置されている。メモリセルアレイのビット線方向両側に第1、第2のセンスアンプがそれぞれ配置されている。複数のパッドが配列されたパッド列は、メモリセルアレイのビット線方向一方側に配置されている。第1のソース線及び電源配線は、半導体基板の最上層に形成され、パッド列側の第1のセンスアンプから第2のセンスアンプ側に配置されている。

(もっと読む)

141 - 160 / 222

[ Back to top ]