Fターム[5F083LA18]の内容

半導体メモリ (164,393) | レイアウト・回路設計(平面図中心) (10,937) | 配線レイアウト (4,019) | 接地線 (134)

Fターム[5F083LA18]に分類される特許

1 - 20 / 134

半導体記憶素子及び半導体記憶装置

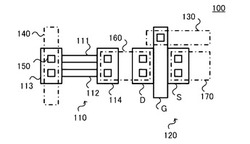

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体記憶装置

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

記憶素子、信号処理回路および記憶素子の駆動方法

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を位相反転素子の入力あるいは出力に接続し、他方の電極をスイッチング素子に接続する。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体装置

【課題】配線層の空きスペースを利用して電源補償容量を形成する。

【解決手段】Y方向に配列された複数のメモリマットMATと、Y方向に隣接するメモリマットMAT間にそれぞれ配置されたセンス領域SAと、カラム選択信号を生成するカラムデコーダ13と、複数のメモリマットMAT上をY方向に延在し、カラム選択信号をカラムデコーダ13から複数のセンス領域SAに供給するカラム選択線YSと、カラムデコーダ13からみて最も遠いメモリマットMATa上に設けられた電源補償容量30とを備える。電源補償容量30は、容量電極として機能する電源配線VL1,VL2を含み、その少なくとも一方がカラム選択線YSと同じ配線層に形成されている。本発明によれば、カラム選択線YSを形成する必要のないメモリマットMATa上に電源補償容量30を設けていることから、チップ面積を縮小することが可能となる。

(もっと読む)

半導体記憶装置

【課題】セル面積増大を抑制しつつゲート形成時のパターンずれによる特性低化を有効に防止し、さらに電源電圧供給線を低抵抗化する。

【解決手段】第1の電源電圧供給線VDDと第2の電源電圧供給線VSSとの間に電気的に直列接続されてゲートが共通に接続された第1導電型の駆動トランジスタQn1,Qn2と第2導電型の負荷トランジスタQp1,Qp2とからそれぞれが構成され、入力と出力が交叉して接続された2つのインバータをメモリセルごとに有する。第1の電源電圧供給線VSSと第2の電源電圧供給線VSSの少なくとも一方が、層間絶縁層の貫通溝内を導電材料で埋め込んだ溝配線からなる。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体記憶装置

【課題】SRAMのゲート配線形成にあたって、ゲート形状を複雑に変形させることなく転写及び加工マージンを確保する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1組及び第2組のドライバトランジスタ11、ロードトランジスタ12及びアクセストランジスタ13とを備えたメモリセルが半導体基板上に2次元配列されたメモリセルアレーと、複数のワードラインと、複数のビットラインと、第1組のドライバトランジスタ11とロードトランジスタ12とを接続し、直線状の側辺を有する長方形状の第1ゲート配線3aと、アクセストランジスタ13と接続され、直線状の側辺を有する長方形状の第2ゲート配線3cと、第1ゲート配線3aと、第2組のドライバトランジスタ11とロードトランジスタ12とを接続する第1コネクタ5aと、第2ゲート配線3cとワードラインとを接続する第2コネクタ5cとを備える。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定かつ高速に動作する半導体記憶装置を実現する。

【解決手段】メモリセル列ごとにアレイ電源線(ARVD)およびダウン電源線(DWVD)を配置する。ダウン電源線は、読出し時に接地に結合され、書込み時にフローティング状態とされる。書込み時、選択列のアレイ電源線への電源電圧の供給を停止するとともに該アレイ電源線を対応のダウン電源線に接続する。電源系統を複雑化することなく、低電源電圧下においても安定にデータの書込/読出を行うことのできる半導体記憶装置を実現することができる。

(もっと読む)

半導体記憶装置

【課題】給電セルのレイアウト面積を縮小することによりメモリアレイ全体のレイアウト面積をさらに縮小することが可能な半導体記憶装置を提供する。

【解決手段】第1の金属配線層に、Nウェル電圧VDDBを供給するメタル312を設ける。メタル312は、共有コンタクト216および219によりNウェル領域に設けられた活性層300と電気的に結合され、Nウェル領域に対してNウェル電圧VDDBが供給される。第3の金属配線層にPウェル電圧VSSBを供給するメタル332,333を設ける。Nウェル電圧VDDBを供給するメタル312は、第1の金属配線層のメタルを用いた構成としているため下層へのくい打ち領域を必要とせず、Pウェル電圧VSSBのメタル332,333の下層へのくい打ち領域のみ確保すればよい。したがって、給電セルPMCのY方向の長さを縮小して、給電セルのレイアウト面積を縮小することができる。

(もっと読む)

半導体装置

【課題】CMOSインバータを含むメモリセルにおいて、リーク電流によるゲート配線の制約やデザインルールの制約を起因とするメモリセルの面積の増大を抑える。

【解決手段】第1のインバータIV1と第2のインバータIV2を含むメモリセル1Aの第1の金属層として、第1の配線FL1及び第2の配線FL2が配置されている。第1の配線FL1は、第1のインバータIV1の2つのドレインDと第2のインバータIV2の第2のゲート配線GL2と接続している。第2の配線FL2は、第2のインバータIV2の2つのドレインDと第1のインバータIV1の第1のゲート配線GL1と接続している。第1の配線FL1は第2のゲート配線GL2と重畳し、第2の配線FL2は第1のゲート配線GL1と重畳して配置される。第1の金属層よりも上層には、第2の金属層と、その上層の第3の金属層が配置されている。

(もっと読む)

半導体記憶装置の製造方法及び半導体記憶装置

【課題】メモリセルアレイの保持内容に起因するリーク電流による誤読み出しを抑制可能な半導体記憶装置を製造する。

【解決手段】接地電位制御要否判定部3が、設計対象のメモリセルアレイの保持内容から、メモリセルのトランジスタの接地電位の制御の要否を判定し、接地電位の制御が必要と判定された場合、接地電位制御回路生成部4が、読み出し動作時に非選択となるトランジスタの接地電位を引き上げる接地電位制御回路を生成する。

(もっと読む)

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体装置

【課題】高集積なCMOS型SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体137と第1の第2導電型半導体104との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、第1の第1導電型半導体137の上下に配置された第1の第2導電型高濃度半導体182と、第2の第2導電型高濃度半導体141と、第1の第2導電型半導体104の上下に配置された第1の第1導電型高濃度半導体186と、第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート導電体167と、を有するインバータを用いてSRAMを構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】周辺回路部内に配置する上層配線の本数を削減することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】基板表面にメモリセル部及びセンスアンプが設けられた基板100と、センスアンプ下の基板内に形成された第2素子分離領域及び第2素子領域201,202と、第2素子領域上に順に形成されたゲート絶縁膜及びゲート電極を含み、センスアンプ内に配置された周辺トランジスタ(ゲート電極)206と、同じ層に配置された複数の配線208と、メモリセル部内にて基板上に配置され、メモリセル部とセンスアンプとを電気的に接続する複数のビット線BLとを備え、第2素子領域は、帯状の形状を有する第1及び第2の帯状部211と、第1の帯状部と第2の帯状部とを接続するよう形成された接続部212とを含み、更に、第2素子領域の接続部上に形成され、いずれか1つの配線と電気的に接続されたソースコンタクト(CS1,CS2)を備える。

(もっと読む)

半導体装置

【課題】SRAMを有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に形成された6つのnチャネル型トランジスタQNA1,QNA2,QNA3,QNA4,QND1,QND2と、2つのpチャネル型トランジスタQPL1,QPL2とによって構成されるメモリセルMC1を有する半導体装置である。シリコン基板1上には、行方向に見て、順に、第1pウェルPW1、第1nウェルNW1、第2pウェルPW2、第2nウェルNW2、および、第3pウェルPW3が配置されている。第1および第2正相アクセストランジスタQNA1,QNA2は第1pウェルPW1に配置され、第1および第2ドライバトランジスタQND1,QND2は第2pウェルPW2に配置され、第1および第2逆相アクセストランジスタQNA3,QNA4は第3pウェルPW3に配置されている。

(もっと読む)

1 - 20 / 134

[ Back to top ]