Fターム[5F083PR03]の内容

Fターム[5F083PR03]に分類される特許

161 - 180 / 1,171

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

半導体装置の製造方法

【課題】エッチングレートを上昇でき、生産性を向上できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に交互に積層されたシリコン層とシリコン酸化膜とを備える多層膜に対して、一括してエッチングを行う工程を含み、前記エッチングの際のエッチングガスは、少なくとも2種類以上の第7族元素と、第3族元素,第4族元素,第5族元素,または第6族元素とを含有し、前記エッチング工程の際の前記半導体基板に入射するイオンのエネルギーは、100eV以上であり、前記第7族元素に対する、前記第3族乃至前記7族元素の添加比率は、0.5以上3.0以下である。

(もっと読む)

フラッシュメモリアレイのワード線構造を保護するためのワード線保護装置およびフラッシュメモリアレイのためのワード線構造

【課題】製造中に、プロセスに関連する帯電からフラッシュメモリのワード線およびメモリセルを保護するための方法と構造とを与える。

【解決手段】ドープされたポリシリコンのワード線110aの端部にドープされていないポリシリコン110bが形成され、抵抗110bが生成される。これを通じて、プロセスにより生じる電荷が、基板に結合された、ドープされたポリシリコン放電構造110cへ放電される。ワード線抵抗110b、および、放電構造110cは、単一のパターニングされたポリシリコン構造として形成される。ワード線110aおよび放電部分110cは導電性になるように選択的にドープされ、また、抵抗部分110bは、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。

(もっと読む)

半導体装置及びその製造方法

【課題】フローティングゲートとコントロールゲートとが積層されたスタック構造のゲート電極を有する半導体装置に関し、隣接メモリセル間やメモリセルとビット線との間における短絡不良を防止しうる半導体装置及びその製造方法を提供する。

【解決手段】トンネルゲート絶縁膜22上に、第1の幅を有する導電膜24、ONO膜28、コントロールゲート40を形成する。コントロールゲート40をマスクとして導電膜24をエッチングしてフローティングゲート26を形成した後、層間絶縁膜80を形成し、第1の方向の幅が第1の幅よりも広いコンタクトホール84を形成する。その後、コンタクトホール84の内壁に、サイドウォールスペーサ88を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 メモリセルアレイ領域と周辺回路領域との配線溝の深さを最適化する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、レジストパターンをマスクとして芯材膜を加工する工程と、前記芯材膜上に被加工膜とエッチング選択比がある側壁膜を形成する工程と、前記側壁膜を異方性エッチング工程により加工する工程と、前記芯材膜を前記側壁膜と選択的に除去する工程と、第1領域の前記側壁膜上および前記被加工膜上に絶縁膜を第1の膜厚を有するように形成し、第2領域の前記被加工膜上に前記絶縁膜を第2の膜厚を有するように形成する工程と、を備えている。さらに、前記第2領域においてフォトリソグラフィ工程によりレジストパターンを形成する工程と、前記第1領域における前記側壁膜と前記第2領域における前記レジストパターンとをマスクとして前記絶縁膜および前記被加工膜を加工し、前記被加工膜に配線溝を形成する工程と、を備えている。

(もっと読む)

二端子抵抗性スイッチングデバイス構造及びその製造方法

【課題】二端子デバイスを形成する方法を提供する。

【解決手段】基板302の表面領域に重なる第1誘電体材料402を形成し、下部配線材料602は、第1誘電体材料に重なるように形成され、スイッチング材料902は、下部配線材料に重なるように堆積される。下部配線材料及びスイッチング材料に対して第1パターニング及びエッチングプロセスを行い、上部表面領域及びサイド領域を有する第1構造1102を形成する。第2誘電体材料1202は、スイッチング素子の露出領域を含む第1構造1102に重なるように形成される。第2誘電体層1202の部分に開口領域1402を形成して、スイッチング素子の上部表面領域の部分を露出させる。上部配線材料1602は、導電性材料がスイッチング素子と直接接触するように、開口領域1402に重なるように形成される導電性材料を含む。第2エッチングプロセスは、上部配線構造を形成するために実行される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、コンタクトプラグと埋め込み型のゲート電極との間に配置される絶縁膜の厚さを十分に確保可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート絶縁膜16を介して、半導体基板11に形成された凹部14の凹部14の一部を埋め込むゲート電極41と、ゲート電極41の上端面41aを覆うように凹部14内を埋め込む絶縁膜18と、凹部14の一方の側面14a側に位置する半導体基板11の主面11aに形成された不純物拡散領域43と、不純物拡散領域43の上面43aを覆うシリコン層21と、半導体基板11の主面11aに形成された第1及び第2の層間絶縁膜23,31に内設され、シリコン層21の上面21aと接触し、かつ下端34bがシリコン層21の上面21aと絶縁膜18の上面18aとの間に配置されたコンタクトプラグ34と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】側壁接合領域を有した半導体装置の製造方法を提供する。

【解決手段】基板をエッチングしてトレンチを形成するステップと、前記トレンチ底面の基板内に接合領域を形成するステップと、前記トレンチ底面を一定の深さエッチングして側壁接合領域を形成するステップと、前記側壁接合領域に接続するビットラインを形成するステップと、を含む半導体装置の製造方法。

(もっと読む)

半導体素子のパターン形成方法

【課題】互いに異なる幅のパターンを同一層で形成するにあたり、パターン間の間隔の均一度を改善することができる半導体素子のパターン形成方法を提供する。

【解決手段】セル領域及びセレクトトランジスタ領域を含む下部膜上に補助膜を形成する段階と、前記セレクトトランジスタ領域の前記補助膜上部に第1保護膜を形成する段階と、前記セレクトトランジスタ領域の前記第1保護膜上部には、前記第1保護膜の幅より狭い第1フォトレジストパターンが、前記セル領域の前記補助膜上部には前記第1フォトレジストパターンの幅より狭い第2フォトレジストパターンが形成され、前記第1及び第2フォトレジストパターン間の間隔を前記第2フォトレジストパターン間の間隔と同一に形成する段階と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】不揮発性記憶装置の特性を向上させ、微細化を図る。

【解決手段】第1の配線と第2の配線とに接続された記憶セルを有する不揮発性記憶装置の製造方法であって、前記第1の配線の上に、第1の電極膜を形成する工程と、前記第1の電極膜の上に、複数のカーボンナノチューブが絶縁材中に分散され、前記複数のカーボンナノチューブのうちの少なくとも1つのカーボンナノチューブが前記絶縁材の表面から表出した層を形成する工程と、前記層の上に、第2の電極膜を形成する工程と、前記第2の電極膜の上に、前記第2の配線を形成する工程と、を備えたことを特徴とする不揮発性記憶装置の製造方法が提供される。

(もっと読む)

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板10上に第1絶縁膜13を介在して形成された電荷蓄積層14と、電荷蓄積層14上に第2絶縁膜15を介在して形成された制御ゲート16とを具備し、制御ゲート16は、その少なくとも一部領域16−2において、その側面が外側に向かって膨らんだ形状を有し、制御ゲート16において側面が膨らみ始める部分から該制御ゲート16の頂上までの高さH1は、膨らみ始める部分より上の領域における制御ゲート16の最大幅W2_max2よりも大きい。

(もっと読む)

半導体装置

【課題】ゲートコンタクトプラグ形成のためのコンタクトホールの深さを適切に制御可能とする。

【解決手段】半導体装置1は、活性領域ARを囲む第1の絶縁体ピラー21と、第1の絶縁体ピラー21の活性領域AR側の側面21sとy方向に相対向する側面22sを有する第2の絶縁体ピラー22と、第1及び第2の絶縁体ピラー21,22の上面を覆う絶縁膜31と、第1のゲート電極16と電気的に接続し、かつ少なくとも側面21s,22sを覆う第2のゲート電極23と、底面に絶縁膜31及び第2のゲート電極23が露出したコンタクトホールの内部に設けられ、かつ第2のゲート電極23の上面と電気的に接続するゲートコンタクトプラグ42とを備え、側面21s,22s間の距離は、ゲートコンタクトプラグ42のx方向の長さより短く、ゲートコンタクトプラグ42は側面21s,22s間の領域で第2のゲート電極23と電気的に接続する。

(もっと読む)

記憶装置の製造方法

【課題】記憶層を分断加工する際に記憶層の表面酸化を抑えることが可能な記憶装置の製造方法を提供する。

【解決手段】下部電極11が形成された基板2上に、記憶層材料膜13Aと上部電極材料膜12Aとを順に形成する。上部電極材料膜12の上にフォトレジスト膜31を形成する。フォトレジスト膜31をマスクとしたドライエッチングを行うことにより、上部電極材料膜12Aおよび記憶層材料膜13Aをこの順にエッチングし、上部電極12および記憶層13をライン状(線状)に形成する。誘導結合型プラズマまたは磁気中性線放電プラズマを用い、ドライプロセスでフォトレジスト膜31を剥離する。記録層材料膜13Aまたは記憶層13がウェットエッチング用の薬液に触れることがなくなり、記憶層13の表面酸化が抑えられる。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 上部電極の膜減りが生じ難いプレーナ型強誘電体キャパシタの製造方法を提供する。

【解決手段】 半導体基板の上に、下部電極層、強誘電体層、上部電極層を形成する。上部電極層の上に、第1の方向に並ぶハードマスクパターンを形成する。ハードマスクパターンをエッチングマスクとして、上部電極層及び強誘電体層をエッチングすることにより、上部電極及びキャパシタ誘電体膜を形成する。第1の方向に並んだハードマスクパターン及び下部電極層の一部を、連続したレジストパターンで覆う。レジストパターン及びキャパシタ誘電体膜をエッチングマスクとして、下部電極層をエッチングすることにより、下部電極を形成する。下部電極の、第1の方向に延在する両側の縁が、ハードマスクパターンの間の領域において、内側に向かって窪むように、レジストパターン及びハードマスクパターンの形状及び寸法が設定されている。

(もっと読む)

半導体装置の製造方法

【課題】ボーイング形状に形成される深孔をストレート形状にする。

【解決手段】シリコン窒化膜4上に、不純物ドープした第1のシリコン酸化膜5と、不純物非ドープの第2のシリコン酸化膜6の積層構造の層間絶縁膜に、ドライエッチングによりボーイング形状の第1のホール8を形成し、熱リン酸を用いたウエットエッチングによりシリコン窒化膜4と第1のシリコン酸化膜5とを後退させてボーイング部の下部を拡幅した第2のホール9を形成する。

(もっと読む)

半導体装置の製造方法

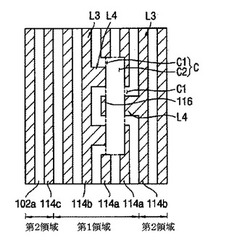

【課題】より一層微細化された半導体装置を製造可能な製造方法を提供する。

【解決手段】半導体基板100にピラーを区画する複数のトレンチ108を設ける工程と、トレンチ108の底部のビット線が形成される領域である第1の領域を覆う埋め込みシリコン酸化膜109aと、埋め込みシリコン酸化膜109aの内部に埋め込まれた埋め込みドープドシリコン膜110bと、第1の領域よりも上方の領域である第2の領域の側面に形成されたシリコン窒化膜113とを有し、第1の領域の側面の一部に埋め込みシリコン酸化膜109aの露出された溝112cを形成する工程と、溝112cの内面にノンドープシリコン膜114を形成して、熱処理を施すことにより埋め込みDOPOS膜110bの上面に新たな埋め込みドープドシリコン膜114aを形成する工程とを備える半導体装置の製造方法とする。

(もっと読む)

161 - 180 / 1,171

[ Back to top ]