Fターム[5F083PR03]の内容

Fターム[5F083PR03]に分類される特許

141 - 160 / 1,171

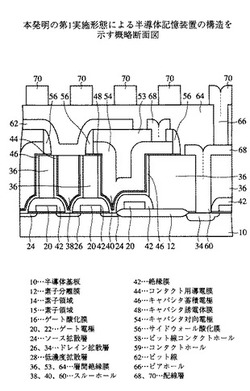

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

エッチング装置およびエッチング方法

【課題】素子分離絶縁膜の上面の高さを、基板上の全面でほぼ均一にできるとともに、素子分離絶縁膜の上面を平坦化することができるエッチング装置を提供する。

【解決手段】実施形態によれば、反応室11と、反応室11とゲートバルブGVを介して接続される真空ポンプ12と、加工対象を保持する保持部19と、エッチングガス供給手段と、加熱部20と、昇華量判定手段と、を備える。エッチングガス供給手段は、加工対象と反応して反応生成物を生成可能なエッチングガスを反応室11内に供給する。加熱部20は、反応生成物が昇華する温度以上に加工対象を加熱する。昇華量判定手段は、加熱部20による昇華処理の経過による反応生成物の昇華の度合いに対応して変化する所定の物理量を昇華量対応変化値としてモニタする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】書き込み特性の向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板10上に、トンネル絶縁膜11を形成し、前記トンネル絶縁膜上に、導電体で構成される電荷蓄積層12を形成し、前記電荷蓄積層、前記トンネル絶縁膜、および前記基板を加工して、前記基板内に、前記電荷蓄積層および前記トンネル絶縁膜を分離する素子分離溝22を形成し、前記素子分離溝内に、上面が前記電荷蓄積層の下面より高く上面より低くなるように素子分離絶縁膜13を埋め込み、前記電荷蓄積層の表面に形成された自然酸化膜30を除去し、前記素子分離絶縁膜および前記電荷蓄積層の表面に、絶縁膜14を形成し、前記自然酸化膜の除去から前記絶縁膜の形成までが、その内部の酸素濃度がコントロールされた製造装置内で行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】 エアギャップ構造を簡易な方法で形成する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、半導体基板上に導電層を含む被加工膜を形成する工程と、前記被加工膜上にダミー膜を形成する工程と、を備えている。さらに、前記ダミー膜を所望の形状にデポ条件の異方性エッチングにより加工する工程と、前記被加工膜を所望の形状に異方性エッチングにより加工する工程と、前記所望の形状に加工された被加工膜上の前記ダミー膜を異方性エッチングにより除去する工程と、前記被加工膜上に上層膜を形成する工程と、を備えている。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】簡単な構成で、複数の積層チップパッケージを積層し互いに電気的に接続することを可能にし、所望の数の半導体チップを含むパッケージを低コストで実現する。

【解決手段】積層チップパッケージ1Sは、本体2を備え、本体2は、主要部分2Mと、主要部分2Mの上面、下面に配置された複数の第1の端子4、第2の端子5を有している。主要部分2Mは、2つの階層部分10S1,10S2と、これらを貫通する複数の貫通電極Tを含んでいる。複数の貫通電極Tは、複数の端子4,5に電気的に接続されている。各階層部分は、第1の面と第2の面を有する半導体チップと、複数の表面電極を含んでいる。階層部分10S1,10S2は、第2の面同士が対向するように接合されている。端子4は階層部分10S1の表面電極を用いて構成され、端子5は階層部分10S2の表面電極を用いて構成されている。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トランジスタの電流駆動能力の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置10は、半導体基板1の表層に第一の方向に延在するように形成された複数の活性領域1aと、前記活性領域1aの表層から深さ方向に形成されたn型不純物拡散層15と、前記複数の活性領域1aを横切り第二の方向に延在するように形成された複数の埋め込みゲート用の溝部13a,bと、ゲート絶縁膜25a,bを介して前記活性領域1a上を跨ぐように前記埋め込みゲート用の溝部13a,bに埋め込まれたゲート電極31およびダミーゲート電極32とを構成すると共に、前記半導体基板1の面上において前記第二の方向に延在する複数のワード配線層と、を具備し、前記ダミーゲート電極32の上面32cが、前記n型不純物拡散層15と前記活性領域1aとの界面よりも下方に位置していることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の歩留まりを向上させること。

【解決手段】シリコン基板20に溝20aを形成する工程と、溝20aに充填材30を充填する工程と、溝20aに充填材30が充填された状態で、シリコン基板20に対してウエット処理を行う工程と、ウエット処理の後、充填材30を除去する工程と、充填材30を除去した後、溝20a内に、キャパシタ誘電体膜45aを介してキャパシタの対向電極50pを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域となるSOI構造を有する半導体線条突出部の形状のばらつきを抑制し、トランジスタ特性のばらつきを減少することができる半導体装置を提供する。

【解決手段】半導体基板1の素子分離用の溝に埋込み絶縁膜が埋め込まれてなる素子分離領域2と、素子分離領域2によって区画されてなり、素子分離用の溝を区画する側壁面と半導体基板の1一面とを有し、かつ側壁面には埋込み絶縁膜に向けて突出した半導体線条突出部1aが素子分離用の溝に沿って設けられてなる活性領域Tと、半導体線条突出部1aを残して活性領域Tを分断するように設けられたゲート電極用のゲート溝3と、ゲート溝3の内面に形成されたゲート絶縁膜4と、ゲート溝3に埋め込まれたゲート電極5と、ゲート電極5のゲート長方向両側の活性領域Tにそれぞれ形成され、半導体線条突出部1aによって連結される不純物拡散領域7と、を具備してなることを特徴とする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】隣接セルとの容量を抑制することが可能な半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態の半導体記憶装置は、第1の方向および前記第1の方向と直交する第2の方向に配置される複数のメモリセルトランジスタを備える。前記メモリセルトランジスタのそれぞれは、半導体基板上に形成される第1の絶縁膜と、前記第1の絶縁膜上に形成される浮遊ゲート電極と、前記浮遊ゲート電極上に形成される第2の絶縁膜と、前記第2の絶縁膜上に形成される制御ゲート電極と、を有する。前記第1および第2の方向に隣接する2つの前記メモリセルトランジスタの前記浮遊ゲート電極は、前記隣接する方向の側面に括れた領域を有する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、電極膜及び絶縁膜が交互に積層され、端部の形状が前記電極膜毎にステップが設けられた階段状である積層体と、前記端部の上方から前記電極膜に接続されたコンタクトと、前記積層体の前記端部以外の部分に設けられ、前記積層体を積層方向に貫く半導体部材と、前記電極膜と前記半導体部材との間に設けられた電荷蓄積層と、前記端部を前記積層方向に貫く貫通部材と、を備える。そして、前記貫通部材には、前記電荷蓄積層を形成する材料と同種の材料が含まれていない。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と周辺回路領域の双方におけるMOSトランジスタの最適化が可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、サイドウォールを側壁に有するゲート電極を含むMOSトランジスタを、半導体基板1上のメモリセル領域及び周辺回路領域に備えた半導体装置の製造方法であって、前記サイドウォールを形成した後に、選択エピタキシャル成長法により、前記半導体基板1上面にシリコン層10を形成する工程を備え、前記シリコン層10を形成した後に、少なくとも前記周辺回路領域をマスク20bで覆い、エッチングにより、前記メモリセル領域内のMOSトランジスタTr1のサイドウォール9cを薄化する工程を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置の製造方法

【課題】マスクの新規な作製技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、第1の膜を形成する工程と、第1の膜上方に、第1マスク膜を形成する工程と、第1マスク膜をパターニングする工程と、パターニングされた第1マスク膜の側部にプラズマ処理を行って、側部を変質層に変換する工程と、プラズマ処理の後、第1マスク膜の上部及び側部を覆う第2マスク膜を形成する工程と、第2マスク膜をエッチングして、側部に形成された第2マスク膜を残存させつつ、第1マスク膜上部に形成された第2マスク膜を除去する工程と、第2マスク膜のエッチングの後、変質層を除去する工程と、変質層を除去した後、残った部分の第1マスク膜、及び第2マスク膜をマスクとして、第1の膜をエッチングする工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

141 - 160 / 1,171

[ Back to top ]