Fターム[5F083PR03]の内容

Fターム[5F083PR03]に分類される特許

121 - 140 / 1,171

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体装置の歩留まりを向上可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】アンモニア水を用いた湿式エッチングにより、エッチングマスク形成用溝の側面を洗浄することで、下部電極及びエッチングマスクの母材となる下部電極形成用金属膜を成膜する前に、異方性ドライエッチング時にエッチングマスク形成用溝の側面に付着したポリマーを除去し、次いで、エッチングマスク形成用溝に、下部電極形成用金属膜を成膜することでエッチングマスクを形成し、その後、湿式エッチングにより、エッチングマスクをマスクとして、メモリセル領域に形成された第4の層間絶縁膜を選択的に除去する。

(もっと読む)

誘電体デバイスの製造方法及びエッチング方法

【課題】強誘電体と電極との間のエッチング選択性を高め、強誘電体を高精度にエッチングすることができる誘電体デバイスの製造方法及びエッチング方法を提供する。

【解決手段】金属からなる第1の電極層2の上に酸化物からなる誘電体層3を形成し、誘電体層3の上にエッチングマスク4を形成し、CHF3を含むエッチングガスのプラズマによってエッチングマスク4を介して誘電体層3をエッチングすることで、前記第1の電極層2を露出させる。

(もっと読む)

半導体装置の製造方法

【課題】基板に電圧を印加して基板にダメージを及ぼすことなく、当該基板における、大型基板において特に顕在化する複雑な態様の反りの発生部位及び発生状態を容易且つ正確に特定する。そして、大型基板でも確実なチャッキングに供することを可能とする。

【解決手段】センサ部2は、搭載面1aの中央部分に設けられた第1のセンサ群11と、第1のセンサ群11を囲む第2のセンサ群12と、第2のセンサ群12を囲む第3のセンサ群13とを有する。第1のセンサ群11は、基板面の中央部分に対応して設けられた1つの静電容量センサ10aから、第2のセンサ群12は、第1のセンサ群11を同心状に囲む複数の静電容量センサ10aから、第3のセンサ群13は、第2のセンサ群12を同心状に囲み、搭載面1aの周縁の近くに設けられた複数の静電容量センサ10aを有する。

(もっと読む)

半導体装置の製造方法及びハードマスクの形成方法

【課題】アモルファスカーボン膜のパターン寸法ばらつきが低減した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にアモルファスカーボン膜を成膜する工程と、アモルファスカーボン膜のパターンを形成する工程と、アモルファスカーボン膜をマスクにして下地膜をエッチングする工程を有する。アモルファスカーボン膜は、アモルファスカーボン膜の表面から下地膜に接する面に向かってその厚み方向を進むにつれて、アモルファスカーボン膜の膜密度を小さくする。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜を薄膜化して低電圧の動作を可能にしつつ、飽和反転電荷量を増大ささせる。

【解決手段】半導体装置は、下部電極41と、強誘電体膜36と、上部電極35とから形成されるキャパシタ42を有する。強誘電体膜36は、PZTから形成され、膜厚方向の中央部分のTiの含有量が他の領域の比べて多くなっている。Tiの分布は、膜厚方向の中央から上下の電極35,41に向けて減少するような分布である。さらに、Srなどのドーパント元素の含有量が、下部電極41との界面で最も多く、上部電極35に向けて減少する分布を有する。

(もっと読む)

半導体記憶装置の製造方法

【課題】製造が容易なNAND型半導体記憶装置の製造方法を提供する。

【解決手段】製造方法は、基板101上に第1絶縁膜105及び第2絶縁膜106を交互に積層して積層体110を形成する工程と、第1絶縁膜105及び第2絶縁膜106の積層方向に延び、積層体110を貫通する貫通孔114を形成する工程と、貫通孔114の内面上に、MONOS116を構成するブロック絶縁膜、チャージトラップ膜及びトンネル誘電体膜の少なくとも一部を形成する工程と、トンネル誘電体膜上にチャネル半導体117を形成する工程と、積層体110にトレンチ121を形成する工程と、トレンチ121を介してエッチングを施すことにより、第2絶縁膜106を除去する工程と、第2絶縁膜106を除去した後の空間内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】コントロールゲートの低抵抗化とボイドの抑制とを両立させることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板の上方に設けられ電荷を蓄積可能なフローティングゲートと、フローティングゲートの上方に設けられ該フローティングゲートに蓄積された電荷量を制御するコントロールゲートとを含むメモリセルを備えている。コントロールゲートは、エッチングで加工可能な金属または金属シリサイドから成る下層コントロールゲート部分と、下層コントロールゲート部分とは異なる材料を用いた上層コントロールゲート部分とを備えている。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】本発明の不揮発性メモリ装置の製造方法は、セル領域及び周辺回路領域を有する基板上に層間絶縁膜及びゲート電極膜が交互に積層されたゲート構造物を形成するステップと、前記セル領域の前記ゲート構造物を選択的にエッチングして、複数層の前記ゲート電極膜を一方向から分離させる第1トレンチを形成するステップと、前記周辺回路領域のコンタクト予定領域に対応する前記ゲート構造物を選択的にエッチングして、第2トレンチを形成するステップと、を含む。

(もっと読む)

記憶素子およびその製造方法、並びに記憶装置

【課題】良好な絶縁耐圧性を有する記憶素子を提供する。

【解決手段】下部電極、記憶層および上部電極をこの順に有し、記憶層は、抵抗変化層とイオン源層とにより構成されている。イオン源層は可動イオンとなる元素を含み、上部電極および下部電極に電圧を印加すると、記憶層の抵抗値が変化して情報を記憶する。抵抗変化層はフッ化マグネシウムなどのフッ化物を含有する。または、下部電極がフッ素またはリンを含有する。これにより、抵抗変化層は電圧印加の影響を受けにくく、抵抗変化層の劣化に起因するメモリ特性の低下が抑制される。

(もっと読む)

半導体装置の製造方法

【課題】金属コンタクトを安定に形成できる半導体装置の製造方法を提供する。

【解決手段】セル領域にストレージノードコンタクトプラグ12を形成するステップと、第1の層間絶縁膜17を形成するステップと、周辺領域の第1の層間絶縁膜上に第1のビットライン20を形成するステップと、第2の層間絶縁膜22を形成するステップと、周辺領域の第2の層間絶縁膜上に第1のビットラインと電気的に接続された第2のビットライン25を形成するステップと、セル領域のストレージノードコンタクトプラグの上面を露出させるステップと、セル領域にストレージノードコンタクトプラグと接するキャパシタを形成するステップと、キャパシタが形成された基板の全面に第3の層間絶縁膜31を形成するステップと、周辺領域の第3の層間絶縁膜を貫通して第2のビットラインに接する金属コンタクト33を形成するステップとを含むことを特徴とする。

(もっと読む)

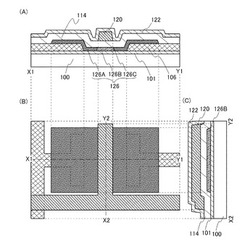

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

集積回路装置の製造方法

【課題】金属部材の劣化を抑えた集積回路装置の製造方法を提供する。

【解決手段】実施形態に係る集積回路装置の製造方法は、ハロゲンを含むガスを用いて金属部材をエッチングする工程と、エッチングされた前記金属部材を大気に曝すことなく、前記金属部材のエッチング面を覆うようにシリコン酸化膜を形成する工程と、前記シリコン酸化膜を除去する工程と、を備える。

(もっと読む)

記憶装置及びその製造方法

【課題】信頼性が高い記憶装置及びその製造方法を提供する。

【解決手段】記憶装置1は、複数の微小導電体が隙間32を介して集合したナノマテリアル集合層23と、隙間32内に配置された絶縁材料25と、を備える。微小導電体はカーボンナノチューブ31であり、カーボンナノチューブ31が延びる方向は、ナノマテリアル集合層23の下面に対して垂直な方向よりも、下面に対して平行な方向に近く、ナノマテリアル集合層23の下面に接した下部電極層22と、ナノマテリアル集合層23の上面に接した上部電極層24と、をさらに備え、下部電極層22及び上部電極層24の双方に接した微小導電体が存在しない。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

3次元半導体素子及びその製造方法

【課題】工程不良を無くして収率を向上させることができる3次元半導体素子及びその製造方法が提供される。

【解決手段】3次元(3D)半導体メモリー素子は、基板に隣接する下段から上段まで伸張して、複数個のメモリーセルと連結された垂直チャンネルと、前記複数個のメモリーセルを有し、前記基板上に配置された階段形構造のゲートスタック形態にアレイされたセルアレイと、を含む。前記ゲートスタックは、前記下段に隣接する下部非メモリートランジスターに連結された下部選択ラインを含む下部膜と、前記上段に隣接する上部非メモリートランジスターに各々連結され、互いに連結されて単一の導電性ピースになって上部選択ラインをなす導電ラインを有する複数個の上部膜と、各々ワードラインを有し、セルトランジスターと連結され、前記下部選択ラインと前記上部選択ラインの間に配置される複数個の中間膜と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

半導体装置

【課題】導電性ブリッジの消去動作時の消去時間のばらつきの最大値を抑えて、メモリ素子の書き換え時間を短縮する。

【解決手段】半導体装置は、第1の面から厚み方向の内側に向かって形成された孔部を有する第1絶縁膜と、第1絶縁膜上に設けられ第1イオン伝導体を含む抵抗変化層と、孔部内壁の側面及び底面を覆うと共に凹部を有するように孔部内に形成され上端を介して抵抗変化層に接する第1電極と、第1電極の凹部内に埋め込まれると共に第1電極よりも大きい電子抵抗を有する埋め込み層と、抵抗変化層上に第1電極の上端及び埋め込み層と共に抵抗変化層を挟むように形成された第2電極とを有する半導体素子、を備える。半導体素子は、抵抗変化層内において、第1電極の上端と第2電極の間に導電性架橋を可逆的に形成することにより第1電極と前記第2電極の間の電子抵抗を変化させる。

(もっと読む)

121 - 140 / 1,171

[ Back to top ]