Fターム[5F083PR03]の内容

Fターム[5F083PR03]に分類される特許

101 - 120 / 1,171

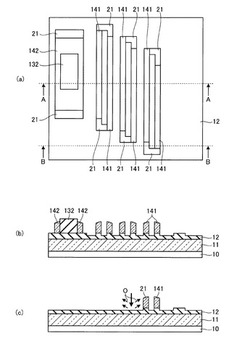

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体装置の製造方法及びコンピュータ記録媒体

【課題】効率良く多段の良好な形状の階段状の構造を形成することのできる半導体装置の製造方法及びコンピュータ記録媒体を提供する。

【解決手段】第1の誘電率の第1の膜と、第1の誘電率とは異なる第2の誘電率の第2の膜とが交互に積層された多層膜と、多層膜の上層に位置しエッチングマスクとして機能するフォトレジスト層とを有する基板をエッチングして、階段状の構造を形成する半導体装置の製造方法であって、フォトレジスト層をマスクとして第1の膜をプラズマエッチングする第1工程と、水素含有プラズマにフォトレジスト層を晒す第2工程と、フォトレジスト層をトリミングする第3工程と、第3工程によってトリミングしたフォトレジスト層及び第1工程でプラズマエッチングした第1の膜をマスクとして第2の膜をエッチングする第4工程とを有し、第1工程乃至第4工程を繰り返して行うことにより、多層膜を階段状の構造とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグと半導体基板の活性領域との間の重ねマージンを十分に確保して、低抵抗且つ接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極19A及びキャップ絶縁膜20Aと、活性領域1Aの上面に設けられたビットコンタクト27A及びビット線27と、半導体基板1上に設けられた絶縁層32,40と、第1容量コンタクトプラグ39Aと、を備え、第1容量コンタクトプラグ39Aは、柱状部39aとこの柱状部39aの下方に設けられた板状部39bとを有し、板状部39bの底面と、素子分離領域及びキャップ絶縁膜20Aによって区画された活性領域1Aの表面1a,1cとが全面で接触するように設けられていることを特徴とする半導体装置を選択する。

(もっと読む)

半導体装置の製造方法

【課題】下部電極の相変化膜接触面と相変化膜の下面との間で位置ずれが発生することを防止する。

【解決手段】本発明による半導体装置1の製造方法は、導電材料を成膜することにより、スルーホール10a内に下部電極HEを形成する工程と、層間絶縁膜10の上面が露出する程度まで表面を平坦化する工程と、下部電極HEの上面の一部を覆うマスク膜をマスクとして用いて下部電極HEをエッチングすることにより、層間絶縁膜10の上面に絶縁膜埋込用溝部を設け、その内部に絶縁膜13aを埋め込む工程と、層間絶縁膜14を形成して表面を平坦化することによりマスク膜の上面を露出させる工程と、マスク膜を除去することにより、層間絶縁膜14の上面に開口部14aを設ける工程と、開口部14a内に相変化材料を成膜することにより、開口部14a内に露出した下部電極HEの上面を相変化膜GSTで覆う工程とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルアレイに用いられる配線の抵抗を低減することができる半導体記憶装置の製造方法を提供する。

【解決手段】一の実施の形態に係る半導体記憶装置の製造方法は、第1配線層を積層する工程と、第1配線層の上方にメモリセル層を積層する工程と、メモリセル層の上方に、後の研磨工程を減速させるためのストッパ膜を積層する工程とを備える。また、製造方法は、ストッパ膜、メモリセル層、及び第1配線層をエッチングする工程と、ストッパ膜、メモリセル層、及び第1配線層を層間絶縁膜により埋め込んだ後、ストッパ膜に達するまで研磨する工程と、ストッパ膜及び層間絶縁膜に窒化処理を実行して、ストッパ膜及び層間絶縁膜の表面にそれぞれ調整膜及びブロック膜を形成する工程とを備える。そして、製造方法は、調整膜の上方に、エッチングされた第1配線層と交差して各交差部にメモリセルが配置されるように、第2配線層を形成する工程を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体記憶装置の製造方法

【課題】高集積化を図ることができる半導体記憶装置の製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、基板上に第1膜と第2膜とを交互に積層して第1積層体を形成する工程と、前記第1積層体上に第3膜と第4膜とを交互に積層して第2積層体を形成する工程と、前記第1膜のエッチング速度よりも前記第3膜のエッチング速度の方が低くなる条件でエッチングを施すことにより、前記第2積層体及び前記第1積層体を貫く貫通ホールを形成する工程と、前記貫通ホールの内面上に電荷蓄積膜を形成する工程と、前記貫通ホール内に半導体部材を形成する工程と、を備える。そして、前記第1膜と前記第2膜とを相互に異なる材料によって形成し、前記第3膜と前記第4膜とを相互に異なる材料によって形成し、前記第1膜と前記第3膜とを相互に異なる材料によって形成する。

(もっと読む)

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ゲートの端部に集中する電界を緩和し、電荷のトラップおよびトンネル絶縁膜の破壊を抑制し、信頼性を向上させる。

【解決手段】半導体記憶装置は、半導体基板上に設けられたアクティブエリアを備えている。素子分離部が、アクティブエリア間に設けられ、絶縁膜で充填されている。データを記憶する複数のメモリセルがアクティブエリアに形成されている。空洞が、アクティブエリアのメモリセルが形成された部分の上端縁部と素子分離部内の絶縁膜との間に設けられている。

(もっと読む)

シリコン構造体、当該シリコン構造体を用いた容量素子および当該シリコン構造体の作製方法

【課題】3次元的に複雑な形状のシリコン構造体を提供する。また、当該シリコン構造体を、自然と秩序が生じて自分自身で秩序的なパターン形成が行われる現象を用いて簡便に作製する方法を提供する。

【解決手段】アモルファスシリコン層に水素雰囲気下でプラズマ処理を行って、当該シリコン層表面に微結晶シリコンを成長させる反応過程と、露出しているアモルファスシリコン層をエッチングする反応過程を並行して進行させ、当該シリコン層上に微結晶状の上部構造体とアモルファス状の下部構造体からなるナノ構造体を形成することにより、3次元的に複雑な形状のシリコン構造体を提供することができる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

101 - 120 / 1,171

[ Back to top ]