Fターム[5F083PR15]の内容

Fターム[5F083PR15]の下位に属するFターム

RTN (63)

Fターム[5F083PR15]に分類される特許

41 - 60 / 259

記憶装置及びその製造方法

【課題】下部電極と下層との接触抵抗を低減することができ、良好なスイッチング特性が得られる、記憶装置を提供する。

【解決手段】メモリセル毎に分離して形成された下部電極13と、この下部電極13の上に形成され、抵抗値の変化により情報を記録することが可能な記憶層14と、この記憶層14の上に形成された上部電極15とを含み、金属から成る第1の層17と、この第1の層17の上に形成された、金属窒化物から成る第2の層18と、第1の層17及び第2の層18の積層により形成され、下層には第1の層17のみが接し、上層の記憶層14には第2の層18のみが接するように形成された、下部電極13と、複数のメモリセルで共通に形成された記憶層14と、複数のメモリセルで共通に形成された上部電極15とを含む、記憶装置を構成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置

【課題】デプレッション型トランジスタを用いて構成される記憶素子を有する半導体装置であっても、正確な情報の保持を可能にすること。

【解決手段】あらかじめ信号保持部への信号の入力を制御するトランジスタのゲート端子に負に帯電させ、且つ電源との接続を物理的に遮断することにより負電荷を保持させる。加えて、一方の端子が当該トランジスタのゲート端子に電気的に接続される容量素子を設け、当該容量素子を介して当該トランジスタのスイッチングを制御する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

単一ステップによる選択的窒化の方法および装置

半導体基板を選択的に1ステップで窒化するための方法および装置が提供される。窒素は、選択的窒化プロセスを利用することにより、シリコン領域および酸化ケイ素領域を有する半導体基板のシリコン領域中に選択的に組み込まれる。窒素含有プラズマを形成し、このプラズマからイオンをフィルタリングまたは除去することにより、基板に窒素含有ラジカルが向けられてもよく、または、選択前駆体を使用する熱窒化プロセスを実施してもよい。遠隔プラズマジェネレータが、1つまたは複数のイオンフィルタ、シャワーヘッド、およびラジカル分配器を任意に備える処理チャンバに結合されてもよく、または、in situプラズマが生成され、1つまたは複数のイオンフィルタもしくはイオンシールドが、チャンバ内においてプラズマ発生ゾーンと基板支持体との間に配設されてもよい。  (もっと読む)

(もっと読む)

半導体装置

【課題】バーズビーク酸化に関する問題を効果的に解決することが可能な半導体装置を提供する。

【解決手段】半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜上に形成された浮遊ゲート電極3と、浮遊ゲート電極上に形成された電極間絶縁膜6と、電極間絶縁膜上に形成された制御ゲート電極7と、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ浮遊ゲート電極のチャネル長方向に平行な一対の側面の下端近傍に形成された一対の酸化膜4aと、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ一対の酸化膜の間に形成された窒化膜2cとを備え、一対の酸化膜はそれぞれ、チャネル幅方向に平行な断面において上から下に向かってしだいに幅が広くなっている楔状の形状を有している。

(もっと読む)

半導体装置

【課題】トランジスタ特性に優れ、ゲート絶縁膜のゲート電極の近傍の領域中で電荷や電界の集中が起こらない半導体装置を提供する。

【解決手段】半導体装置は、トランジスタを備える。トランジスタのゲート絶縁膜は窒素原子及び酸素原子を含有する。ゲート絶縁膜は、半導体層に接する第1の面及びゲート電極に接する第2の面において窒素原子を含有せず、第1の面と第2の面の間に窒素原子濃度のピークを有する。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】高速処理が可能で、かつ電荷保持特性の高いチャージトラップ型フラッシュメモリを得ることができる半導体装置の製造方法を提供する。

【解決手段】基板100の表面を酸化してシリコン酸化膜140を形成するシリコン酸化膜形成工程と、プラズマ状態の窒素含有ガスをシリコン酸化膜140に供給してシリコン酸化膜140の表面近傍に窒素ピーク濃度が20原子%以上60原子%以下の窒化層141を形成する窒化層形成工程と、窒化層141が形成されたシリコン酸化膜140上に電荷保持膜150を形成する電荷保持膜形成工程と、電荷保持膜150上に、絶縁膜160と電極膜170を形成する電極膜形成工程とを有する。

(もっと読む)

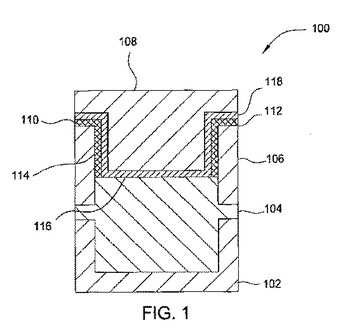

半導体装置,半導体装置の製造方法及び半導体製造装置

【課題】膜厚を増大させることなく,キャパシタ容量の低下を抑制する。

【解決手段】キャパシタ100を有する半導体装置において,キャパシタ100は,下部電極112と上部電極16と,下部電極112と上部電極16とに挟まれた絶縁膜14とを備えている。下部電極112は窒化チタンからなり,当該下部電極112の絶縁膜14側の表面がさらに窒化されて窒素リッチ層118が形成されている。下部電極112の表面に窒素リッチ層118が形成されることにより,下部電極112の上面の酸化が効果的に抑制される。特に,DRAMにおいては,キャパシタの容量が大きくなるため,その効果が大きい。またキャパシタ内部のリーク電流も減る。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトランジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】素子分離絶縁膜上に引き出したワード線がシリサイド層形成時に断線するのを防止する。

【解決手段】メモリセルトランジスタを形成する領域の外側では、広い範囲にわたり素子分離絶縁膜2aが形成されている。素子分離絶縁膜2aの表面に、ワード線WLと直交する方向に溝状の凹部2bを複数本形成する。この上部にワード線WLを形成すると、凹部2b内にワード線WLを構成する第2導電膜である多結晶シリコン膜が埋め込まれる。ワード線WLを形成後に、ワード線上部にシリサイド層を形成する。このとき、シリサイド反応に必要なシリコンは凹部2b内から不足分が供給できるので、断線の発生を防止できる。

(もっと読む)

半導体装置

【課題】素子特性の劣化を可及的に防止することのできる半導体装置を提供する。

【解決手段】半導体基板51と、半導体基板上に設けられたゲート絶縁膜53と、ゲート絶縁膜上に設けられた第1ゲート電極54aと、第1ゲート電極上に設けられ金属および酸素を含む電極間絶縁膜55と、電極間絶縁膜上に設けられた第2ゲート電極54bと、第1および第2ゲート電極の両側の半導体基板に設けられたソース/ドレイン領域58a、58bと、を備え、電極間絶縁膜55は、リン、砒素、アンチモン、ビスマスのうちから選択された少なくとも1つの添加元素を含み、その含有量が0.1at%以上3at%以下である。

(もっと読む)

Pチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法

【課題】書き換え電圧を低くできるようにしたPチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法を提供する。

【解決手段】シリコン基板1に設けられたN型ウェル領域2と、N型ウェル領域2内で互いに離れた状態で設けられた第1のP型拡散領域(ソース)及び第2のP型拡散領域(ドレイン)と、第2のP型拡散領域上に設けられたトンネル絶縁膜14bと、N型ウェル領域2のうちの第1のP型拡散領域と第2のP型拡散領域とに挟まれた領域(即ち、チャネルとなる領域)上に設けられたゲート絶縁膜14aと、ゲート絶縁膜14a上からトンネル絶縁膜14b上にかけて連続して設けられた浮遊ゲート電極15と、を備え、第2のP型拡散領域はトンネル絶縁膜14bの直下の全領域に配置されている。

(もっと読む)

41 - 60 / 259

[ Back to top ]