Fターム[5F083PR15]の内容

Fターム[5F083PR15]の下位に属するFターム

RTN (63)

Fターム[5F083PR15]に分類される特許

141 - 160 / 259

半導体装置およびその作製方法

【課題】不揮発性メモリトランジスタの電荷保持特性を向上させる。

【解決手段】半導体基板と導電膜の間には、トンネル絶縁膜として機能する第1絶縁膜、電荷蓄積層、第2絶縁膜が形成されている。電荷蓄積層は2層の窒化シリコン膜でなる。下層の窒化シリコン膜は、窒素ソースガスにNH3を用いてCVD法で形成され、N−H結合を上層よりも多く含む。上層の第2窒化シリコン膜は、窒素ソースガスにN2を用いてCVD法で形成され、Si−H結合を下層よりも多く含む。

(もっと読む)

非揮発性メモリ素子及び製造方法

【課題】データ保有時間、動作速度及び信頼性を一層改善できる非揮発性メモリ素子及び製造方法を提供する。

【解決手段】半導体基板上に金属シリケート層を含むトンネル層を形成する工程と、前記金属シリケート層上に電荷トラップ層を形成する工程と、前記電荷トラップ層上に電荷ブロック層を形成する工程と、前記電荷ブロック層上にゲート層を形成する工程とを含んで非揮発性メモリ素子製造方法を構成する。

(もっと読む)

半導体装置の製造方法

【課題】プラグまたは局所配線による接続で低い接続抵抗と十分に小さい拡散層リーク電流を実現し、更に深さが異なる接続孔や開口断面の断面の形状や大きさが異なる接続孔または局所配線穴を用いる場合でも、十分に小さい拡散層リーク電流と低い接続抵抗を実現する製造方法を提供する。

【解決手段】基体上の絶縁膜に開口した、表面がシリコンを主成分とする層が底部に露出している第1の開口部(接続孔または局所配線穴)の群と、表面が第1の金属珪化物を主成分とする層が底部に露出している第2の開口部の群と、表面が第1の金属を主成分とする層が底部に露出している第3の開口部の群のうちの、少なくとも2群の各開口部の底部に、第2の金属珪化物を主成分とする層また第2の金属を主成分とする層を、化学気相成長法によって同時に形成する。

【効果】従来以上に高集積、高性能の半導体装置が実現される。

(もっと読む)

半導体装置

【課題】一方は高速動作が可能で駆動電圧の低い薄膜トランジスタ、他方は電圧に対して高耐圧で信頼性の高い薄膜トランジスタの両方を有する半導体装置を提供することを目的とする。従って、低消費電力かつ高信頼性を付与された半導体装置を提供することを目的とする。

【解決手段】絶縁表面を有する同一基板上に半導体層の膜厚の異なる複数種の薄膜トランジスタを有する。高速動作を求められる薄膜トランジスタの半導体層のチャネル形成領域を、電圧に対して高い耐圧性を求められる薄膜トランジスタの半導体層のチャネル形成領域より薄膜化し、チャネル形成領域の膜厚を薄くする。また、ゲート絶縁層においても、高速動作を求められる薄膜トランジスタは、電圧に対して高い耐圧性を求められる薄膜トランジスタより膜厚が薄くてもよい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】バーズ・ビークの形成が抑制されて素子特性のばらつきが抑制された信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板201と、半導体基板201表面部のチャネル領域202上に形成された第1の絶縁膜204と、第1の絶縁膜204上に形成された電荷蓄積層205と、電荷蓄積層205上に形成された第2の絶縁膜206と、第2の絶縁膜206上に形成された制御ゲート電極207と、電荷蓄積層205の底面、表面及び側面に形成されたSi−N結合を含む第3の絶縁膜208と、を備える

(もっと読む)

強誘電体メモリ装置の製造方法および強誘電体メモリ装置

【課題】コンタクトプラグと下部電極との間の抵抗上昇を抑えるとともに、強誘電体キャパシタを構成する各層の結晶配向を良好に制御することができる強誘電体メモリ装置の製造方法と、これによって得られる強誘電体メモリ装置を提供する。

【解決手段】基板の上方に下地層を形成し、下地層上に第1電極、強誘電体層、第2電極を積層する強誘電体メモリ装置の製造方法である。下地層の形成は、プラグ20を含む層間絶縁膜上に、自己配向性を有する導電材料からなる第1導電層を形成する工程と、第1導電層をCMP法で平坦化処理し、平坦化第1導電層41とする工程と、平坦化第1導電層41の表面に対してアンモニアプラズマ処理を施す工程と、アンモニアプラズマ処理を施した平坦化第1導電層41上にチタン層を形成する工程と、チタン層を窒素雰囲気中で熱処理して窒化チタン層に変化させ、第2導電層43とする工程とを含む。

(もっと読む)

絶縁膜積層体、絶縁膜積層体の製造方法、半導体装置及び半導体装置の製造方法

【課題】ボロン漏れの抑制とリーク電流増加の抑制とを同時に実現可能な、絶縁膜及びこの絶縁膜を備えた半導体装置と、絶縁膜の製造方法及び半導体装置の製造方法を提供する。

【解決手段】微結晶組織からなるハフニウム含有窒化シリコン酸化物層3aと、非晶質組織からなるハフニウム含有窒化シリコン酸化物層3bとが半導体基板2上に積層されてなる積層膜からなり、積層膜の窒素濃度が15原子%以上40原子%以下の範囲であることを特徴とする半導体装置用の絶縁膜積層体3を採用する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】浮遊電極間での干渉効果を抑え、電極間絶縁膜に流れるリーク電流を低減し、さらに素子の劣化を防ぐことが可能な不揮発性半導体記憶装置を提供すること。

【解決手段】不揮発性半導体記憶装置は、基板の主表面に形成された第1絶縁層2とその上に形成された第1導電層3と、第1絶縁層のゲート幅方向の両側面及び、第1導電層のゲート幅方向の両側面の少なくとも一部を埋め込んで上面が第1導電層の上面と底面の間の高さに位置するように形成された素子分離用の絶縁層7と、第1導電層及び素子分離用の絶縁層の上に形成されたシリコン酸化膜81とシリコン酸窒化膜82とシリコン酸化膜83とからなる3層絶縁膜を含んだ第2絶縁層8と、その上に形成された第2導電層9とを備え、シリコン酸窒化膜に含まれる水素原子及び塩素原子の濃度がそれぞれ1.0×1019atoms/cm3以下で且つ中間絶縁膜に含まれる酸素原子の割合が総原子数の10%以上である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】薄膜化しても書き込み/消去を繰り返したときの耐性(エンデュランス特性)が悪化しないトンネル絶縁膜を有する半導体記憶装置を提供することを可能にする。

【解決手段】半導体基板2と、半導体基板上に形成され、第1シリコン酸窒化層8b、シリコン窒化層8b、および第2シリコン酸窒化層8cの積層構造を有するシリコン酸窒化膜8と、シリコン酸窒化膜上に形成されたシリコンリッチなシリコン酸化膜10とを備えた第1絶縁膜6と、第1絶縁膜上に形成された電荷蓄積層12と、電荷蓄積層上に形成された第2絶縁膜14と、第2絶縁膜上に形成された制御ゲート16と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜を形成する際の界面欠陥の生成を抑制するとともに、生成された欠陥を低減させることを可能にする。

【解決手段】半導体基板の表面を窒化する第1窒化ガスと、半導体基板と実質的に反応しない第1希釈ガスとを含み、第1希釈ガスの分圧と第1窒化ガスの分圧の和と、第1窒化ガスの分圧との比が5以上でかつ全圧が40Torr以下である第1雰囲気中に半導体基板を置き、半導体基板の表面に窒化膜を形成する工程と、表面に窒化膜が形成された半導体基板を、酸素原子の結合エネルギーが1eV〜4eVの範囲の酸化ガスと、半導体基板と実質的に反応しない第2希釈ガスとを含む第2雰囲気中に置き、半導体基板と窒化膜との間に第1酸窒化層を形成するとともに窒化膜の表面に第2酸窒化層を形成する工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率絶縁膜を備えていても、素子特性の劣化を防止することができる半導体装置およびその製造方法を提供することを可能にする。

【解決手段】半導体基板1と、半導体基板に離間して形成されたソース領域8aおよびドレイン領域8bと、ソース領域とドレイン領域との間の半導体基板上に形成された第1絶縁膜3と、第1絶縁膜上に形成された電荷蓄積膜4と、電荷蓄積膜上に形成された高誘電率材料で形成された第2絶縁膜5bと、第2絶縁膜上に形成された制御ゲート電極6と、三配位の窒素結合を有しかつ窒素の第二近接原子の少なくとも1つが窒素であるシリコン窒化層5a、5cと、を備え、電荷蓄積膜と前記制御ゲート電極との少なくとも一方がシリコンを含み、前記シリコン窒化層は、第2絶縁膜と、電荷蓄積膜および制御ゲート電極のうちのシリコンを含む方との界面に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置を形成するためのウエハ表面の窒化にあたり、基板主面と平行な面方向及び交差する面方向の何れについても同様な窒化速度を得る。

【解決手段】窒化処理チャンバー22内に複数のウエハ23を収容する。プラズマ生成チャンバー21内に反応ガスとしてN2ガス及びNH3ガスを供給し、プラズマ24を発生させる。また、窒化処理チャンバー22の下流で真空ポンプによる排気を行い、プラズマ生成チャンバー21内で生成された窒素ラジカルを窒化処理チャンバー22内に流す。これにより、ウエハ表面に窒素ラジカルを供給して窒化処理を行う。

(もっと読む)

非揮発性メモリ素子及びその製造方法

【課題】高誘電体膜の電気的な特性を向上させる事ができる非揮発性メモリ素子及びその製造方法を提供する。

【解決手段】フローティングゲート104とコントロールゲート122間誘電体120として、酸化膜108,116の間に高誘電絶縁膜112を含む高誘電体膜を形成し、高誘電絶縁膜の上部及び下部、またはフローティングゲートの上部及びコントロールゲートの下部に窒素含有絶縁膜106,110,114,118を形成することにより、酸化膜と高誘電絶縁膜との間、または酸化膜とフローティングゲートまたはコントロールゲートとの間の界面反応を抑制し、高誘電体膜の誘電率、漏洩電流、絶縁破壊電圧及び電荷保存特性などの電気的な特性を向上させ、高性能及び高信頼性の高誘電体膜を製造することができる。

(もっと読む)

不揮発性半導体メモリ装置およびその製造方法

【課題】プログラム電圧を下げることを可能にするとともにストレス誘起リーク電流を低減することを可能にする。

【解決手段】半導体基板1と、半導体基板に離間して形成されたソース領域8aおよびドレイン領域8bと、ソース領域とドレイン領域との間の半導体基板上に形成され、電子の捕獲サイトを有する第1の絶縁層3b1、捕獲サイトを有しない第2の絶縁層3a、および捕獲サイトを有する第3の絶縁層3b2の積層構造を備え、電子の捕獲サイトは、第1乃至第3の絶縁層の伝導帯準位エネルギーよりも低く、かつシリコンの伝導帯エネルギーよりも高い位置にある第1の絶縁膜3と、第1の絶縁膜上に形成された浮遊ゲート電極4と、浮遊ゲート電極上に形成された第2の絶縁膜5と、第2の絶縁膜上に形成された制御ゲート電極6と、を有するメモリ素子を備えている。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】強誘電体層の結晶配向をより均一にすることが可能な強誘電体メモリ装置の製造方法を提供すること。

【解決手段】下部電極12を形成する下部電極形成工程と、有機金属原料ガスと酸素ガスとの反応により、下部電極12上に第1強誘電体層33を形成する第1強誘電体層形成工程と、有機金属原料ガスと酸素ガスとの反応により、第1強誘電体層33上に第2強誘電体層34を形成する第2強誘電体層形成工程とを備え、第1強誘電体層形成工程における酸素ガス量が、有機金属原料ガスを反応させるために必要な酸素量よりも少なく、第2強誘電体層形成工程における酸素ガス量が、有機金属原料ガスを反応させるために必要な酸素量以上であり、下部電極形成工程が、下部電極12上に下部電極12を構成材料の酸化物で構成される電極酸化物膜32を成膜する電極酸化物膜成膜工程を有する。

(もっと読む)

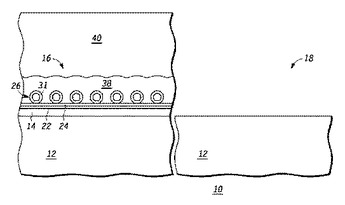

選択領域からナノクラスターを除去する方法

半導体素子を製造する方法は、不揮発性メモリ用の第1部分(16)と第1部分(16)を除く第2部分(18)とを有する半導体層(12)を備えた基板(12)を提供することを含む。半導体層上には第1の誘電体層(14)が形成される。第1の誘電体層上でプラズマ窒化が行なわれる。第1部分上には第1の複数のナノクラスター(20)が、第2部分上には第2の複数のナノクラスター(28)が形成される。第2の複数のナノクラスターは除去され、半導体層上に第2の誘電体層(38)が形成され、第2の誘電体層上に導電層(40)が形成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 バーズビーク酸化に関する問題を効果的に解決することが可能な半導体装置を提供する。

【解決手段】 半導体基板1上に形成されたトンネル絶縁膜2aと、トンネル絶縁膜上に形成された浮遊ゲート電極3と、浮遊ゲート電極上に形成された電極間絶縁膜6と、電極間絶縁膜上に形成された制御ゲート電極7と、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ浮遊ゲート電極のチャネル幅方向に平行な一対の側面の下端近傍に形成された一対の酸化膜8aと、トンネル絶縁膜と浮遊ゲート電極との間に形成され、且つ一対の酸化膜の間に形成された窒化膜2cとを備える。

(もっと読む)

半導体装置及びその作製方法

【課題】ゲート絶縁膜の膜厚が薄くなった部分、即ち、段差部による半導体素子特性への影響を低減し、半導体素子の信頼性を向上させることを目的とする。また、そのような半導体素子を有する半導体装置を実現するための作製方法を提供する。

【解決手段】半導体層と、半導体層の端部を覆うゲート電極と、当該半導体層及びゲート電極を絶縁する絶縁層を有し、半導体層の端部及びゲート電極が重なる領域を絶縁する絶縁層の膜厚が、半導体層の中央部を覆う絶縁層の膜厚より厚い半導体装置である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】2層ゲート構造の不揮発性半導体メモリ素子を有する半導体記憶装置においてトンネル酸化膜のエッチングおよび後酸化工程でのバーズビークの形成を抑制する。

【解決手段】半導体基板S上に第1の絶縁膜11を介して多結晶シリコン層13を形成した後、これを選択的に除去して電荷蓄積層14と第一ゲート絶縁膜12とをそれぞれ形成するとともに、素子領域を囲む素子分離溝TRを半導体基板Sに形成し、素子分離溝TRの側面に側壁酸化膜50を形成した後、側壁酸化膜50の表面のうち半導体基板S側とは逆の表面を窒化する。

(もっと読む)

不揮発性半導体メモリ

【課題】セル間干渉によるメモリセルの閾値電圧の変動を抑制できる。

【解決手段】本発明の例に関わる不揮発性半導体メモリは、表面に素子領域と素子分離領域を有する半導体基板1と、素子領域表面に形成されるゲート絶縁膜2と、ゲート絶縁膜2上に形成される浮遊ゲート電極3Aと、素子分離領域に形成される素子分離絶縁層6と、浮遊ゲート電極3A上及び素子分離絶縁層6上に形成される多層構造のゲート間絶縁膜4と、ゲート間絶縁膜4A上に形成される制御ゲート電極5Aとを具備し、ゲート間絶縁膜4Aの最下層となる絶縁膜は、素子分離絶縁層6上において、浮遊ゲート電極3A上よりも薄いことを備える。

(もっと読む)

141 - 160 / 259

[ Back to top ]