Fターム[5F083ZA04]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090)

Fターム[5F083ZA04]の下位に属するFターム

ゲート構造が異なるもの (317)

ソース/ドレイン構造が異なるもの (250)

ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA04]に分類される特許

21 - 40 / 120

半導体装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線にビット線制御トランジスタを直列に挿入し、そのゲートの最低電位は十分な負の値となるようにする。ビット線制御トランジスタのゲートは電池等に接続するビット線制御回路に接続される。ビット線の最低電位はワード線の最低電位よりも高くなるようにする。外部からの電源が切れた際には、ビット線はビット線制御トランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。あるいは外部電源遮断時にワード線の電位を十分な負の電位とできるような回路を設けてもよい。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

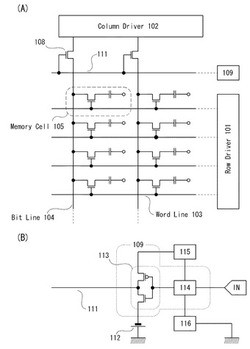

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは、ビット線をキャパシタとセルトランジスタの間に形成するため、構造が複雑であったり、回路の特性を犠牲にしたりする必要があり、集積化の面で大きな障害となっている。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極をセルトランジスタのドレインに接続する。また、セルトランジスタのソースは、ソース線に接続される。この結果、例えば、スタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線は、半導体基板上に形成された不純物領域や、ワード線に平行な配線を用いることができるので、構造が単純となる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置及びその製造方法

【課題】セキュリティを高めるための半導体装置を提供する。

【解決手段】第1トランジスタ4a、および第1トランジスタ4aに接続される第1キャパシタ4bを有する第1メモリセル4を含む第1メモリセルアレイ2と、第1トランジスタ4aよりもオフ電流が高い第2トランジスタ5a、および第2トランジスタ5aに接続される第2キャパシタ5bを有する第2メモリセル5を含む第2メモリセルアレイ3と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量コンタクトプラグと半導体基板の活性領域との間の重ねマージンを十分に確保して、低抵抗且つ接続信頼性の高い半導体装置を提供する。

【解決手段】埋め込みゲート電極19A及びキャップ絶縁膜20Aと、活性領域1Aの上面に設けられたビットコンタクト27A及びビット線27と、半導体基板1上に設けられた絶縁層32,40と、第1容量コンタクトプラグ39Aと、を備え、第1容量コンタクトプラグ39Aは、柱状部39aとこの柱状部39aの下方に設けられた板状部39bとを有し、板状部39bの底面と、素子分離領域及びキャップ絶縁膜20Aによって区画された活性領域1Aの表面1a,1cとが全面で接触するように設けられていることを特徴とする半導体装置を選択する。

(もっと読む)

不揮発性半導体記憶装置

【課題】 トランジスタの接合耐圧と表面耐圧の劣化を抑制し、信頼性の高い不揮発性半導体記憶装置を提供する。

【解決手段】 トランジスタTr.2は、ソース高濃度領域9を有するソース拡散層、メモリセルのゲート絶縁膜より厚いゲート絶縁膜16を有するゲート電極、ドレイン高濃度領域9とドレイン高濃度領域を囲むドレイン低濃度領域23を有するドレイン拡散層22を備え、ドレイン拡散層22は、ゲート絶縁膜16の底面より低い第1の窪みを有し、ドレイン低濃度領域23は、第1の窪みより低い第2の窪み“c”を有し、ドレイン高濃度領域9に接合されるコンタクト10を介してビット線に接続され、ソース高濃度領域に接合されるコンタクトを介してセンスアンプに接続される。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

21 - 40 / 120

[ Back to top ]