Fターム[5F083ZA20]の内容

Fターム[5F083ZA20]に分類される特許

121 - 140 / 345

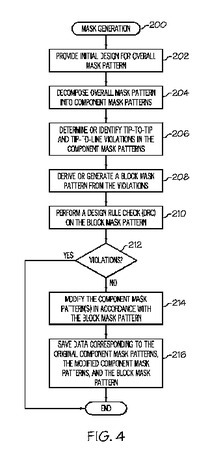

設計規則違反を低減するために多重露光及び遮断マスクの手法を用いる半導体デバイス製造

【解決手段】

半導体デバイス(400)を製造する方法は、半導体材質(402)の層及び半導体材質(402)の層の上の絶縁材質(404)の層を備える基板上に、ハードマスク材質(408)の層が絶縁材質(404)の層の上になるように、ハードマスク材質(408)の層を形成することによって開始する。多重露光フォトリソグラフィ手順が実行されて、ハードマスク材質(408)の層の上にフォトレジスト特徴部の結合されたパターンが作製され、またフォトレジスト特徴部の結合されたパターンを用いてハードマスク材質内に凹部線パターンが作製される。方法は、凹部線パターン(422)の指定された区画をフォトレジスト特徴部の遮断パターン(442)で覆い、そして溝(452)のパターンを絶縁材質(404)内に形成することによって継続し、ここで溝(452)のパターンは、フォトレジスト特徴部の遮断パターン(442)及びハードマスク材質(408)によって規定される。その後、電気伝導材質(472)が溝(452)内に堆積させられて、半導体デバイスのための導電線がもたらされる。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極の基板からの抜け落ちを防止する。

【解決手段】半導体装置は、基板80と、基板80に設けられた1又は複数のビアホール91と、1又は複数のビアホール91内にそれぞれ設けられた貫通電極TSVとをそれぞれ有する複数のコアチップと、貫通電極TSVを通じて各コアチップと電気的に接続するインターフェースチップとを備え、ビアホール91は、両端部の径r1,r3に比べて中央部r2の径が大きいボーイング形状部分91aを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置にメモリセルアレイ及び制御回路を設け、メモリセルアレイには、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体を設け、この積層体に積層方向に延びる貫通ホールを形成し、その内部にシリコンピラーを埋設し、電極膜とシリコンピラーとの間に電荷蓄積膜を設ける。これにより、電極膜とシリコンピラーとの交差部分毎にメモリセルが形成される。そして、制御回路は、フォーマット時に、全てのメモリセルに値「0」を書き込み、全てのメモリセルに対して値「0」を消去する動作を行い、積層体の最上段に形成されたメモリセルに記憶された値を読み出し、値「0」が読み出されたメモリセルについては、消去動作が不良であったと判定し、以後不使用とする。

(もっと読む)

半導体装置の駆動方法

【課題】電荷蓄積層での電子の蓄積または放出が十分でない場合に、不揮発性メモリ素子に保持された記憶状態の正誤を判定し、誤ったデータを読み出すことによる不良を低減する。

【解決手段】メモリセル領域104と、テスト領域105と、を含む半導体記憶回路103と、制御回路と、を有し、制御回路は、メモリセルへのデータの書き込み、第1の領域105Aへの第1の記憶状態の書き込み、または第2の領域105Bへの第2の記憶状態の書き込みを行うための第1の動作を行い、第1の領域及び第2の領域からの第1の記憶状態または第2の記憶状態の読み出しを行うための第2の動作を行い、メモリセルからのデータの読み出しを行うための第3の動作を行い、第2の動作において、第1の領域からの読み出しが第1の記憶状態であるか、または第2の領域からの読み出しが第2の記憶状態であるかに応じて、第3の動作の正誤を判定する。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積の増大を抑制しつつ、不良ブロックの非選択処理が可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリマット10〜60を含むメモリアレイをコの字型に配置し、メモリアレイが配置されていない空き領域にロジック回路92およびアナログ回路91を配置している。これにより、アナログ回路91およびロジック回路92などの周辺回路と電源パッド101およびデータパッド100などのパッド帯との間で電源電圧および信号のやりとりが容易となる。また、アナログ回路91については電源パッド101に近くなるため、電源配線抵抗による電圧降下を抑制でき、かつ電源パッド101付近でチャージポンプ用電源配線102と周辺回路用電源配線103とを分離することが可能となる。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】破壊されたダイオードを確実に検出することが可能な不揮発性半導体記憶装置とその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、ダイオードと抵抗変化素子により構成された複数のメモリセルが行及び列に配置されたメモリセルアレイを有している。メモリセルに対して書き込み動作、消去動作、読み出し動作のうちの1つを実行する少なくとも前又は後にダイオードがテストされる(S2)。

(もっと読む)

半導体装置及び半導体装置の評価方法

【課題】大規模なSRAMセルの特性を高精度に測定する半導体装置及びそれを用いた評価方法を提供する。

【解決手段】m行n列のマトリクス状に配列されるSRAMセルを有する評価セルC11〜Cnmと、SRAMセルのSNM特性を測定する際にSRAMのラッチノードへ入力電圧を供給し、或いは出力電圧を検出する第1の主入出力線V0等と、評価セルを選択するための行選択信号供給用の行選択線X1〜Xmと、列選択信号供給用の列選択線Y1〜Ynと、入力される行選択信号と列選択信号に応じてSRAMセルの選択/非選択を表す選択信号を出力する選択回路10と、を備え、選択信号供給回路に入力される選択制御信号等により行選択信号と列選択信号を生成し、評価セル各々に設けられた第1のトランジスタT1〜第6のトランジスタT6を切り替え、SRAMセルの測定評価を行う。

(もっと読む)

半導体集積回路装置

【課題】メモリマクロを含む半導体集積回路装置の遅延故障を確実に検出できないという問題があった。

【解決手段】メモリマクロを備える半導体集積回路装置1であり、スキャンモード制御信号(SMC)に応じて、入力データ信号の値とスキャンテスト値とのいずれかを、動作クロックに従って保持する入力データ保持部22−0〜22−kと、テストモード制御信号(TEN)に応じて、入力データ保持部22−0〜22−kが保持する値とメモリセル部が記憶するデータ値とのいずれかを、複数の入力データ保持部が動作する位相とは異なる位相に従って保持する出力データ保持部41−0〜41−kと、を備える。入力データ保持部22−0〜22−kと、出力データ保持部41−0〜41−kとは、入力データ保持部22−0を先端として交互に直列に接続され、複数の出力データ保持部の一つが保持する値は、スキャンテスト値として後段の入力データ保持部へ伝送される。

(もっと読む)

抵抗メモリ素子の抵抗測定方法及び抵抗測定システム

【課題】抵抗メモリ素子の抵抗測定方法及び抵抗測定システムを提供すること。

【解決手段】抵抗メモリ素子の抵抗測定方法及び抵抗測定システムにおいて、前記抵抗メモリ素子の抵抗測定のために、まず、データ書き込みパルスを印加した後、抵抗読み取りパルスを印加する。前記抵抗読み取りパルスを印加した時のパルス波形から前記抵抗メモリ素子のセルを通して、降下する微少電圧と、これを使い、抵抗メモリ素子の抵抗を測定する。前記方法によると、抵抗メモリ素子のセルにデータを記録した直後の抵抗メモリ素子の抵抗を正確に測定することができる。

(もっと読む)

インサイチュでのメモリのアニール

メモリデバイスを有するシステムにおいて、あるイベントがシステム操作中に検出される。メモリデバイスは、そのイベントの検出に応じて、メモリデバイスの使用に起因する劣化を反転させるために加熱される。別のシステムにおいて、メモリデバイスは、そのシステムの別のメモリデバイス内でのデータアクセス操作と同時に使用に起因する劣化を回復させるために加熱される。第1および第2のメモリデバイスと連結されたメモリコントローラを有する別のシステムにおいては、データは、メンテナンス操作が第1のメモリデバイス内において必要であると決定することに応じて、第1のメモリデバイスから第2のメモリデバイスに退避される。 (もっと読む)

半導体記憶素子の製造方法

【課題】金属ナノ結晶からなる離散的フローティングゲートを、移流集積法により形成する半導体記憶素子の製造方法を提供する。

【解決手段】製造方法は、シリコン基板1と、シリコン基板1上に形成されたトンネル絶縁膜に対向するように配置された第2の基板21との間に、金属ナノ粒子が分散された粒子分散液22を充填する充填工程と、トンネル絶縁膜の表面に沿った方向に、第2の基板21をシリコン基板1に対して相対的に移動させることにより、トンネル絶縁膜の表面における第2の基板21から露出した領域に形成される粒子分散液22のメニスカス領域23において、粒子分散液22の溶媒を蒸発させることにより、トンネル絶縁膜上に金属ナノ粒子を離散的に配置する。

(もっと読む)

半導体集積回路評価方法、半導体集積回路、及び半導体集積回路評価装置

【課題】大規模な半導体集積回路における不良トランジスタの検出と、不良トランジスタの特性の測定とを高速で行うことができる、半導体集積回路評価方法を提供する

【解決手段】評価セルアレイ11,12中のトランジスタTrの閾値Vthが、閾値Vthの正規分布曲線に対して、5σ以内の分布から外れたものを、複数のセンスアンプSA_A,SA_Bを用いて判定(閾値Vth判定)する。そして、閾値Vthが5σ以内の分布から外れたトランジスタTrに対して、トランジスタ特性の測定を行う。そして、上述の閾値Vth判定を行う際には、複数のセンスアンプSA_A,SA_B間のオフセット差により閾値Vthの判定結果にバラツキが生じることを避けるため、複数のセンスアンプSA_A,SA_Bのオフセット差に応じた基準電流REFを設定し、同一の入力に対して複数のセンスアンプの判定結果を一致させる。

(もっと読む)

抵抗変化メモリのテスト装置、方法および抵抗変化メモリ装置

【課題】任意のテストサイクルにおけるサイクル時間を局所的に自由に調整する。

【解決手段】一定周期で信号変化する第1のライトイネーブル信号と、ワード線の活性化/非活性化制御とビット線の活性化/非活性化制御との間の限界時間の確認を行う時間部分で信号変化する第2のライトイネーブル信号とを入力し、入力された第1および第2のライトイネーブル信号に基づいて、複数のコア制御信号が信号変化する時間間隔が局所的に第1のライトイネーブル信号の周期よりも短い複数のコア制御信号を発生し、発生された複数のコア制御信号を用いて抵抗変化メモリの動作確認を行う。

(もっと読む)

強誘電体膜の評価方法及びそれを用いた液体噴射ヘッドの製造方法

【課題】亀裂の原因を判別することができる強誘電体膜の評価方法、及びこれを用いた、製造工程にすぐにフィードバックをかけることができる液体噴射ヘッドの製造方法を提供する。

【解決手段】強誘電体膜の評価方法は、一対の電極間に形成した強誘電体膜に電圧を印加して、強誘電体膜にリークを生じさせるリーク発生工程と、発生したリークの発生数を測定し、発生数に基づいて強誘電体膜の評価を行う評価工程とを備える。液体噴射ヘッドの製造方法は、圧電素子形成工程後、この強誘電体膜の評価方法を行い、強誘電体膜の評価が良い場合には圧力発生室形成工程を行う。

(もっと読む)

位置識別マーク、および半導体集積回路

【課題】メタル配線層や絶縁層を剥離した場合においても、半導体基板上におけるメモリセル等の物理的な位置を容易に確認できる、位置識別マークを提供する。

【解決手段】本発明の位置識別マークは、拡散層で形成される直線状の基板電位供給用パターン11の側面部(辺側)に、凹凸形状を設けて形成される。そして、基板電位供給用パターン11の一方の側(図1で上側)に、Y(column)方向の個数(左側から何個目の64kブロックかを示す個数)、もう一方の側(図1で下側)に、X(Row)方向の個数(下側から何個目の64kブロックかを示す個数)を示す位置識別マークが形成される。この位置識別マークは、1〜64の間の数値を示すように形成される。図1に示す例では、1,5,10の単位で、幅W・長さLを変えた凸状のパターンa,b,c等を配置する。

(もっと読む)

強誘電体膜を有するデバイスの製造方法及び熱処理装置

【課題】強誘電体膜の配向率を改善し、強誘電体膜を有するデバイスの不良品発生率を小さくすること。

【解決手段】

基板上に強誘電体材料膜を形成する第1の工程と、前記強誘電体材料膜を形成した前記基板を熱処理炉内に配置し、前記熱処理炉内に熱処理雰囲気ガスを第1の流量で供給すると共に、前記第1の流量に対応する第2の流量で前記熱処理炉内を排気しながら、前記強誘電体材料膜を加熱して強誘電体膜を形成する第2の工程とを有すること。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置、その製造方法、その書き込み方法、その読み出し方法、記録媒体並びに半導体記憶装置

【課題】 電荷捕獲量の調節を容易且つ確実に行い、情報ばけ等の不都合の発生を防止して所望の多値情報を記憶する。

【解決手段】 ソース領域3−ドレイン領域4間のチャネル領域Cとゲート電極6との間に、ゲート酸化膜11、シリコン窒化膜12、シリコン酸化膜13、シリコン窒化膜14、シリコン酸化膜15、シリコン窒化膜16及びシリコン酸化膜17が順次積層されてなる電荷捕獲膜5が配されて半導体記憶装置が構成される。ここで、各窒化膜12,14,16とその下層の各酸化膜11,13,15,17との間に存するトラップに電荷を蓄積することで、4値("00","01","10","11")の情報が記憶される。

(もっと読む)

半導体装置

【課題】半導体チップがパッケージに実装された状態でのヒューズ専用端子を不所望に増加させることなく、最終テスト工程での電気ヒューズ溶断を実現する。

【解決手段】第1パッド(P1)、第2パッド(P3)、第3パッド(P2)を半導体チップに設ける。上記第1パッドと上記第3パッドとの間には、所定電圧が印加されることでプログラミング可能な第1ヒューズ素子を有する第1ヒューズ部(WFM)を設ける。上記第2パッドと上記第3パッドとの間には、所定電圧が印加されることでプログラミング可能な第2ヒューズ素子を有する第2ヒューズ部(PFM)を設ける。上記第2パッドに結合された第1端子(T3)と、上記第3パッドに結合された第2端子(T2)をパッケージに設ける。上記第1端子は、上記第2端子とは電気的に独立しており、上記第1端子を介して、上記第2ヒューズ部にヒューズ溶断のための電圧を印加することができる。

(もっと読む)

121 - 140 / 345

[ Back to top ]