Fターム[5F083ZA20]の内容

Fターム[5F083ZA20]に分類される特許

61 - 80 / 345

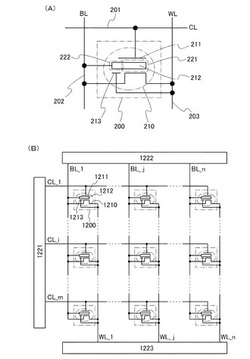

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

記憶装置及びその製造方法

【課題】高集積化が可能な記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられ、複数の微小導電体が隙間を介して集合したナノマテリアル集合層と、前記ナノマテリアル集合層上に設けられ、導電性であり、前記微小導電体に接し、開口部が形成された保護層と、前記保護層上に設けられ、前記保護層に接した上部電極層と、を備える。

(もっと読む)

不揮発性半導体記憶装置の動作方法

【課題】制御部を増加せずにブロックサイズを小さくできる不揮発性半導体記憶装置の動作方法を提供する。

【解決手段】メモリストリングを有するメモリ部と、メモリ部を制御する制御部と、を備える不揮発性半導体記憶装置110の動作方法である。メモリストリングは、直列に接続された複数のトランジスタを含み、複数のトランジスタのうちの一部である第1グループGR1と、第1グループの隣りに接続された第1調整用トランジスタTr−AJと、調整用トランジスタの第1グループとは反対側に接続されたトランジスタを含む第2グループGR2と、を有する。制御部は、第1グループのトランジスタの閾値の書き換えを行ったのち、第1調整用トランジスタに、閾値の書き換えによって生じた第2グループのトランジスタの閾値の相対的な変動分を調整する第1調整用閾値を設定する制御を行う。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体装置の製造方法

【課題】基板に電圧を印加して基板にダメージを及ぼすことなく、当該基板における、大型基板において特に顕在化する複雑な態様の反りの発生部位及び発生状態を容易且つ正確に特定する。そして、大型基板でも確実なチャッキングに供することを可能とする。

【解決手段】センサ部2は、搭載面1aの中央部分に設けられた第1のセンサ群11と、第1のセンサ群11を囲む第2のセンサ群12と、第2のセンサ群12を囲む第3のセンサ群13とを有する。第1のセンサ群11は、基板面の中央部分に対応して設けられた1つの静電容量センサ10aから、第2のセンサ群12は、第1のセンサ群11を同心状に囲む複数の静電容量センサ10aから、第3のセンサ群13は、第2のセンサ群12を同心状に囲み、搭載面1aの周縁の近くに設けられた複数の静電容量センサ10aを有する。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体装置

【課題】パーコレーションリークを抑制可能な構造を有する半導体装置を提供する。

【解決手段】ソース領域18、ドレイン領域18及びチャネル領域を有する半導体領域と、チャネル領域上に形成された第1のトンネル絶縁膜12と、第1のトンネル絶縁膜上に形成され、エネルギー障壁を有する障壁層13と、障壁層上に形成された第2のトンネル絶縁膜14と、第2のトンネル絶縁膜上に形成され、SiY(SiO2)X(Si3N4)1-X (ただし、0≦X≦1、Y>0)で表される絶縁膜を具備する電荷蓄積部15と、電荷蓄積部上に形成され、エネルギー障壁の高さを制御する制御電極17とを備え、X及びYは、[2×2X/(4−2X)+(4−4X)/(4−2X)]×[Y/(Y+7−4X)]≧0.016 なる関係を満たし、障壁層は、クーロンブロッケイド条件を満たす導電性微粒子を含んだ微粒子層で形成されている。

(もっと読む)

シリコン酸化膜の形成方法、シリコン窒化膜の形成方法、シリコン酸窒化膜の形成方法

【課題】ポリシリコン上において高品質な絶縁膜を形成できる絶縁膜の形成方法を提供する

【解決手段】シリコン酸化膜の形成方法は、基板上にポリシリコン膜を堆積する工程と、

前記ポリシリコン膜の表面を、酸素を含むガスとKrガスを主体とする不活性ガスとよりなる混合ガスにマイクロ波によりプラズマを励起することで形成される原子状酸素O*に曝すことにより、前記ポリシリコン膜の表面にシリコン酸化膜を形成する工程とよりなる。

(もっと読む)

半導体メモリ装置およびその検査方法

【課題】オフ抵抗が極めて高いトランジスタをスイッチング素子として有するメモリセルを構成するに際し、信頼性を高める検査方法および構成を提供する。

【解決手段】メモリセルのトランジスタのしきい値Vthが許容される範囲内にあるか否かを判定することにより、データ保持特性が十分でないメモリセルを排除する。そのためにトランジスタのゲートの電位を適切な電位VGMに保持し、また、トランジスタのドレインの電位をVGM以上の電位にする。この状態でメモリセルに書き込むことにより、トランジスタのソースの電位はしきい値Vthを含む式、(VGM−Vth)で表現される。この電位と他の参照電位との大小を比較することによりしきい値Vthが許容される範囲内にあるか否かを判定できる。

(もっと読む)

積層チップパッケージおよびその製造方法

【課題】簡単な構成で、複数の積層チップパッケージを積層し互いに電気的に接続することを可能にし、所望の数の半導体チップを含むパッケージを低コストで実現する。

【解決手段】積層チップパッケージ1Sは、本体2を備え、本体2は、主要部分2Mと、主要部分2Mの上面、下面に配置された複数の第1の端子4、第2の端子5を有している。主要部分2Mは、2つの階層部分10S1,10S2と、これらを貫通する複数の貫通電極Tを含んでいる。複数の貫通電極Tは、複数の端子4,5に電気的に接続されている。各階層部分は、第1の面と第2の面を有する半導体チップと、複数の表面電極を含んでいる。階層部分10S1,10S2は、第2の面同士が対向するように接合されている。端子4は階層部分10S1の表面電極を用いて構成され、端子5は階層部分10S2の表面電極を用いて構成されている。

(もっと読む)

半導体記憶装置の評価方法

【課題】半導体記憶装置のトンネル絶縁膜の電荷分布を評価することが可能な半導体記憶装置の評価方法を提供する。

【解決手段】半導体記憶装置の評価方法は、浮遊ゲート型の半導体記憶装置の評価方法である。時間の対数の変化に対する前記半導体記憶装置のメモリセルの閾値電圧Vtの変化率に、ε*Cr*2k/Tox/qを乗じる。なお、εはトンネル絶縁膜の誘電率であり、Crは前記メモリセルのカップリング比であり、Toxは前記メモリセルのトンネル酸化膜の膜厚であり、kは電荷がデトラップする時の存在確率の減衰率でありk=(2mE/(h/2π)2)0.5と表され、mは電子の質量、 Eは前記トンネル絶縁膜のトラップのエネルギー準位、hはプランク定数、πは円周率である。これにより、前記メモリセルのトンネル絶縁膜中の電子濃度分布を求める。

(もっと読む)

半導体記憶装置

【課題】消去回数の増加を抑制し、書き込み速度の向上及びメモリセルの劣化を防止することが可能な半導体記憶装置を提供すること。

【解決手段】読み出しレベルに応じてデータを保持可能なセルMCが形成されたセルアレイ1と、前記セルMCに書き込まれた回数N(N:0以上の整数)をカウントし、その回数に応じて書込電圧Vpgm及び読出電圧Vcgrを前記セルに転送する制御部9と、前記書込電圧を用いてデータを書み込み、前記読出電圧を発生し、データを読み出す電圧発生回路とを具備し、書込要求があると、前記読出電圧を発生させ、前記データを読み出し、読み出された閾値電圧より高い閾値電圧に遷移させる前記書き込み電圧を前記電圧発生回路に発生させ、前記セルへの前記回数N回目(≧2)の書き込み要求が規定値に達していると、前記制御部は前記セルが保持する前記データを消去させる。

(もっと読む)

半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを長期間にわたり保存する半導体メモリ装置の駆動方法を提供する。

【解決手段】書き込みトランジスタのドレインと素子トランジスタのゲート、および、容量素子の一方の電極を接続したメモリセルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に接続し、キャパシタの他方の電極を読み出しワード線に接続する。そして、容量素子に蓄えられた電荷量を、読み出しワード線の電位を変化させることにより確認し、基準以上に電荷量が減少している場合にはメモリセルのリフレッシュをおこなう。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

半導体装置、および、その製造方法、電子機器

【課題】製造効率の向上、コストダウン、信頼性の向上、小型化を容易に実現させる。

【解決手段】各配線111h,211hにおいて、第1半導体チップ100および第2半導体チップ200の側端部にて露出した側面を、導電層401で被覆される。これにより、導電層401によって両配線111h,211hの間が電気的に接続させる。

(もっと読む)

半導体装置

【課題】リーク電流が発生しにくく、低消費電力化に好適な半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板12内に埋め込まれてX方向に並列して延在する複数のビット線BLと、X方向と交差するY方向に延在するワード線と、ビット線BLと前記第2配線との交点に設けられたメモリセルMと、複数のビット線BLのうち最外列のビット線BLの外側に設けられ、X方向に延在してビット線BLと並走するダミービット線DBLとを含み、ダミービット線DBLが、半導体基板12に供給される電位と同じ電位が供給されるダミービット線(第1ダミー配線)DBL<0>、DBL<1>、DBL<2>を含むことを特徴とする。

(もっと読む)

不揮発性半導体メモリのスクリーニング方法および書き込み装置

【課題】不揮発性半導体メモリのスクリーニングを、製造工程の生産性に影響を与えることなく、より確実に行えるようにする。

【解決手段】不揮発性半導体メモリの製造工程において、検査の結果良品と判定した後、1以上のフローティングゲートにデータを書き込む第1工程と、製造完了後、良品確認工程において、第1工程においてデータが書き込まれた全てのフローティングゲートから書き込んだデータが読み出せる場合には当該不揮発性半導体メモリを良品と判定する第2工程と、からなる。

(もっと読む)

61 - 80 / 345

[ Back to top ]