Fターム[5F083ZA20]の内容

Fターム[5F083ZA20]に分類される特許

81 - 100 / 345

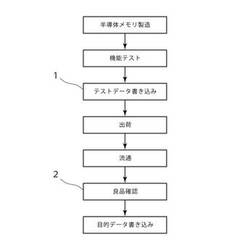

不揮発性半導体メモリのスクリーニング方法および書き込み装置

【課題】不揮発性半導体メモリのスクリーニングを、製造工程の生産性に影響を与えることなく、より確実に行えるようにする。

【解決手段】不揮発性半導体メモリの製造工程において、検査の結果良品と判定した後、1以上のフローティングゲートにデータを書き込む第1工程と、製造完了後、良品確認工程において、第1工程においてデータが書き込まれた全てのフローティングゲートから書き込んだデータが読み出せる場合には当該不揮発性半導体メモリを良品と判定する第2工程と、からなる。

(もっと読む)

相変化メモリコーディング

【課題】取り付け工程に係る半田付け及び高温環境での熱事象を通じても、データを保持することができる相変化メモリデバイスの提供。

【解決手段】一部のセルとメモリに第一抵抗状態、及び他部のセルとメモリに第二抵抗状態を誘導することにより、データセットを表わすために、プレコーディング(pre−coded)することができる。前記データセットがコーディングされ、基板に取り付けられた後に、前記第一及び前記第二抵抗状態を感知することにより、前記データセットを読み取り、前記第一抵抗状態を第三抵抗状態に変化させ、前記第二抵抗状態を第四抵抗状態に変化させる。半田接合と他の熱サイクルプロセスの後、前記第一及び前記第二抵抗状態は、感知マージン(sensing margin)を維持する。より高速とより低い電力を使用すると、前記第三及び前記第四抵抗状態は、転移(transition)を引き起こす能力がある。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁層、電荷蓄積層、及びトンネル絶縁層のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、情報の書込みと消去を繰り返しても閾値電圧の変動が抑制された不揮発性記憶素子を提供する。

【解決手段】基板と、ソース電極と、ドレイン電極と、チャネル層と、電荷蓄積層と、ゲート電極と、前記チャネル層及び前記電荷蓄積層の間に設けられたトンネル絶縁層と、前記電荷蓄積層及び前記ゲート電極の間に設けられた、中間絶縁層と、を備え、前記中間絶縁層、前記電荷蓄積層、及び前記トンネル絶縁層が酸化ガリウムを含み、前記チャネル層が有機半導体層である不揮発性記憶素子である。

(もっと読む)

半導体記憶装置及びその回路の電位測定方法

【課題】大規模な半導体記憶装置における不良トランジスタの検出と、不良トランジスタの特性の測定とを高速で行うことができる、半導体記憶装置を提供する。

【解決手段】メモリ素子が縦横にマトリックス状に配列されたメモリセルアレイと、接地ノードあるいは電源ノードに接続する枝配線を有する半導体記憶装置において、電源ノードあるいは接地ノードに接続する少なくとも1つの枝配線の複数箇所に電圧測定点を接続したモニター用スイッチを有し、クロック信号に同期して前記モニター用スイッチのゲートを順に開くスイッチ選択信号発生回路を有し、前記スイッチ選択信号発生回路で選択されてゲートが開かれたモニター用スイッチを介して前記電圧測定点の電位を測定する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体記憶装置の製造方法及び半導体記憶装置

【課題】メモリセルアレイの保持内容に起因するリーク電流による誤読み出しを抑制可能な半導体記憶装置を製造する。

【解決手段】接地電位制御要否判定部3が、設計対象のメモリセルアレイの保持内容から、メモリセルのトランジスタの接地電位の制御の要否を判定し、接地電位の制御が必要と判定された場合、接地電位制御回路生成部4が、読み出し動作時に非選択となるトランジスタの接地電位を引き上げる接地電位制御回路を生成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作速度を向上させる。

【解決手段】不揮発性半導体記憶装置は、複数の第1の配線、第1の配線に交差する複数の第2の配線、並びに第1及び第2の配線の各交差部に配置された電気的書き換え可能な抵抗値をデータとして不揮発に記憶する可変抵抗素子からなる複数のメモリセルを有するメモリセルアレイを有する。電圧印加手段は、メモリセルに対するデータの書き込み又はフォーミング時に、第1の配線及び第2の配線を介してメモリセルに所定の電圧を印加する。検出手段は、メモリセルに対する所定の電圧の印加時にメモリセルの抵抗状態の変化を検出して検出情報を出力する。出力手段は、検出手段から出力された検出情報の少なくとも一部を外部に出力する。

(もっと読む)

プロセス評価用半導体集積回路

【課題】 微妙なプロセスコントロールのための判断材料となる情報を短時間のうちに採取することができるプロセス評価用半導体集積回路を提供する。

【解決手段】 プロセス評価用半導体集積回路としてのSRAMは、メモリセルに電源電圧を供給する給電系統と、メモリセル以外の回路に電源電圧を供給する給電系統とが分離されており、メモリセルに供給する電源電圧を他の回路に対する電源電圧と独立に制御可能な構成となっている。メモリセルに対する電源電圧を段階的に下げつつ、各メモリセルに対するアクセスを試み、動作不良を検出することにより、メモリセル間のトランジスタの電気的特性の微妙な変化を判定することができる。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】チャネル領域を従来よりも拡大することが可能な半導体装置を提供する。

【解決手段】埋め込みゲート用の溝部9,10のうち、活性領域6に形成される第1の溝部9よりも素子分離領域5に形成される第2の溝部10の深さを深くすることによって、第2の溝部10の底面の間から活性領域6の一部が突き出した第1のフィン部12aと、埋め込みゲート用の溝部9,10の少なくとも上面開口部よりも下部側において、第1の溝部9よりも第2の溝部10の第1の方向における幅を大きくすることによって、第2の溝部10の両側面の間から第1のフィン部12aに連続して活性領域6の一部が突き出した一対の第2のフィン部と12bとを形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】補償容量素子のキャパシタ構造に起因したリーク電流の増加を抑制するとともに、立体構造のキャパシタ構造を採用して、占有面積を削減した半導体装置を提供する。

【解決手段】メモリセル領域に形成されたクラウン型のキャパシタ21aと、周辺回路領域に形成されたコンケイブ型の補償容量素子10と、を有することを特徴とする半導体装置20を提供する。また、第1層間絶縁膜上にパッド47a,47bを形成する工程と、パッド47a,47b上に有底筒形状の下部電極66a,66bを形成する工程と、メモリセル領域の下部電極66aの内壁面及び外壁面と、周辺回路領域の下部電極66bの内壁面のみを誘電体膜67a,67bで覆う工程と、誘電体膜上に上部電極69a,69bを形成する工程と、を有することを特徴とする半導体装置20の製造方法を提供する。

(もっと読む)

記憶素子及び記憶装置

【課題】情報の記録等の動作を安定して行うことができ、熱に対しても安定した構成の記憶素子を提供する。

【解決手段】第1の電極2と第2の電極6との間に、記憶層4及びイオン源層3が挟まれて構成され、イオン源層3に、Cu,Ag,Znから選ばれるいずれかの金属元素と、Te,S,Seから選ばれるいずれかの元素とが含まれ、記憶層4が、タンタル酸化物、ニオブ酸化物、アルミニウム酸化物、ハフニウム酸化物、ジルコニウム酸化物のいずれか、或いはそれらの混合材料から成り、第1の電極2及び第2の電極6に、イオン源層3側の電極が正、記憶層4側の電極が負になるように電圧を印加すると、記憶層4にイオン化した金属元素が移動して電流パスを形成し、記憶層4の抵抗値が低くなる記憶素子10を構成する。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減する。

【解決手段】内部回路(LK#2)の内部ノードに対応して対応の内部ノードの信号をラッチする複数のラッチ回路(F1−F7)をテストパス(302)に配置する。内部回路のMISトランジスタは、ラッチ回路のMISトランジスタよりスタンバイ状態時にゲートトンネル電流が低減される状態に設定される。

(もっと読む)

半導体用配線

【課題】500℃酸化処理でも導電性を失わず、仕事関数がTiN以上であって、しかも貴金属よりも安価な配線材料を提供する。

【解決手段】NiTi混合膜であって、Ti/(Ni+Ti)で表されるTi含有量が60−80at.%なる組成比である配線材料を用い、この配線材料を500℃以上の高温酸化プロセスによりNiとTiO2とを含む混合膜に変換する。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の動作方法

【課題】チップ面積の増大を抑制しつつ、安定的に動作するスプリットゲート型不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体メモリのベリファイステップを以下の手順で実行する。(a)通常読み出し動作のワードゲート電圧よりも低いベリファイ電圧を、ワードゲートに供給する。(b)通常読み出し動作のコントロールゲート電圧を、コントロールゲートに供給する。(c)そのベリファイ電圧とそのコントロールゲート電圧とに応じて流れる電流が、通常読み出し動作のときの参照電流に一致するか否かを判定する。TwinMONOSセルの消去ベリファイ時に、ワードゲートの電圧を低くすることで、コントロールゲートの負電圧を利用せずに消去ベリファイを可能にする。

(もっと読む)

記憶装置、半導体装置

【課題】データの書き込み不良を抑えつつ、面積を小さく抑えることができる不揮発性の記憶装置、または当該不揮発性の記憶装置を用いた半導体装置の提供を目的の一とする。

【解決手段】不揮発性の記憶素子を有する第1の記憶部と、上記第1の記憶部へのデータの書き込みが正確に行われたかどうかを検証するベリファイ動作において、上記データを一時的に保存するための第2の記憶部(データバッファ)とを有する。そして、第2の記憶部が、記憶素子と、当該記憶素子における電荷の保持を制御するための、オフ電流またはリーク電流が極めて小さい絶縁ゲート電界効果型トランジスタとを有する。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの情報の書き込みは、書き込み用トランジスタをオン状態とすることにより、書き込み用トランジスタのソース電極(またはドレイン電極)と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタとして、しきい値電圧を正に制御したトランジスタを用いることで、読み出し電位を正の電位とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】所定の動作の信頼性を向上する。

【解決手段】不揮発性半導体記憶装置は、第1ワード線WL0に接続された第1メモリセルと、前記第1ワード線に隣接する第2ワード線WL1に接続され、前記第1メモリセルと幅が異なる第2メモリセルと、を具備する。前記第1ワード線に第1電圧が印加され、前記第2ワード線に前記第1メモリセルの幅と前記第2メモリセルの幅との差に基づき補正された前記第1電圧と異なる第2電圧が印加される。

(もっと読む)

81 - 100 / 345

[ Back to top ]