Fターム[5F083ZA30]の内容

Fターム[5F083ZA30]に分類される特許

41 - 60 / 136

記憶素子とその製造方法および半導体記憶装置

【課題】抵抗変化層に接触する下部電極の部分の全域に均一に電界を集中させることで、特性ばらつきをなくすことを可能にする記憶素子とその製造方法および半導体記憶装置を提供する。

【解決手段】第1電極21と、第1電極21に対向した位置に形成された第2電極23と、第1電極21と前記第2電極23との間に挟まれて形成された抵抗変化層22とを有し、第1電極21は、筒状体でかつ前記抵抗変化層22側より抵抗変化層22とは反対側の方が厚く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを備える半導体装置において、不揮発性メモリを構成するメモリセルの加工精度を向上することができる技術を提供する。

【解決手段】ポリシリコン膜PF1とダミーゲート電極DMY1を覆うようにポリシリコン膜PF2を形成する。このとき、ポリシリコン膜PF2は、段差DIFおよびギャップ溝GAPの形状を反映して形成される。特に、ギャップ溝GAPを覆うポリシリコン膜PF2には凹部CONが形成される。続いて、ポリシリコン膜PF2上に反射防止膜BARCを形成する。このとき、流動性の高い反射防止膜BARCは、段差DIFの高い領域から低い領域に流出するが、凹部CONに充分な反射防止膜BARCが蓄積されているので、流出する反射防止膜BARCを補充するように凹部CONから反射防止膜BARCが供給される。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】集積度が高く、配線の密着性を向上した高信頼性の不揮発性記憶装置及びその製造方法を提供する。

【解決手段】第1の方向に延在する下側電極130と、下側電極130の上方に位置し、第1の方向と交差する第2の方向に延在する上側電極230と、下側電極130と上側電極230との間に設けられた金属酸化物や相変化材料を用いた記憶部300と、を備える。下側電極130及び上側電極230の少なくともいずれかは、順テーパの側壁を有する第1の電極110、210と、絶縁層150、250を介して第1の電極110と実質的に同じ平面内で隣接し、逆テーパの側壁を有する第2の電極120、220と、を有する。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】配線間の記憶部の加工不良を低減した高歩留まりの不揮発性記憶装置の製造方法を提供する。

【解決手段】不揮発性記憶装置は、第1電極と、第2電極と、第1電極と第2電極との間に設けられ、抵抗が変化する第1記憶層を有する第1記憶部と、を有する。第1電極となる第1電極膜110fと、第1記憶部となる第1記憶部膜130fと、を積層し、これらを第1方向に延在する帯状に加工し、犠牲層181を埋め込む。その上に、第2電極となる第2電極膜140fを形成し、その上に犠牲層よりもエッチング速度が遅いマスク層150を形成し、第2電極膜140fを第2方向に延在する帯状に加工し、第1記憶部膜130fの犠牲層181から露出した部分を除去して第1記憶部膜130fを柱状に加工し、その後犠牲層181を除去して第1記憶部膜130fを露出させて第1記憶部膜130fを除去する。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】配線間の記憶部の加工不良を低減した高歩留まりの不揮発性記憶装置及びその製造方法を提供する。

【解決手段】不揮発性記憶装置は、第1電極と、第2電極と、第1電極と第2電極との間に設けられ、抵抗が変化する第1記憶層を有する第1記憶部と、を有する。第1電極となる第1電極膜110fと、第1記憶部となる第1記憶部膜130fと、を積層し、これらを第1方向に延在する帯状に加工し、所定密度の層581を埋め込む。その上に、第2電極となる第2電極膜140fを形成し、その上に所定密度の層よりも密度が高いマスク層150を形成し、第2電極膜140fを第2方向に延在する帯状に加工し、第1記憶部膜130fの犠牲層581から露出した部分を除去して第1記憶部膜130fを柱状に加工し、その後犠牲層581を除去して第1記憶部膜130fを露出させて第1記憶部膜130fを除去する。

(もっと読む)

半導体記憶装置

【課題】配線間の抵抗値を低減させる、クロスポイント型メモリセルを積層した多層構造の半導体記憶装置を提供する。

【解決手段】半導体基板1と、互いに交差する第1の配線WL及び第2の配線BL並びにこれら第1及び第2の配線の交差部で両配線間に接続されたメモリセルMCを有する1または複数のセルアレイ層MAと、セルアレイ層MAよりも下層の第1配線層M1に形成された第3の配線11と、セルアレイ層MAよりも上層の第2配線層M2に形成された第4の配線12と、第3の配線11及び第4の配線14を接続する積層方向に延びるコンタクト141〜144とを有する。第1配線層M1と第2配線層M2の間には、冗長配線層が形成される。冗長配線層には冗長配線131〜133が形成され、第3の配線11と冗長配線131〜133との間及び第4の配線12と冗長配線131〜133との間は、複数のコンタクト141〜144により接続される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高オン/オン比のダイオードを用い安定して動作する一括加工型積層OTPメモリの不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1導電型の半導体からなる第1導電膜31と、第1導電31膜に積層された第1絶縁膜21と、を有する要素積層体ML1を複数積層した積層構造体MLと、積層構造体MLを積層方向に貫通し、第2導電型の導電領域を有する半導体ピラー25と、半導体ピラー25と第1導電膜31との間に設けられた第2絶縁膜22と、を備える。半導体ピラー25は、第1導電膜31のそれぞれに対向する第1領域41と、積層方向において第1領域41どうしの間に設けられ、第1領域41とは抵抗が異なる第2領域42と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】リソグラフィ工程におけるアライメントマークや重ね合わせ検査マークの計測が確実に、精度良くでき、また、マークにとって不要な構成を有さず、半導体装置の製造プロセスの過程で異物が発生することを抑制して製造歩留が低下することを防止した半導体装置の製造方法および半導体装置を提供する。

【解決手段】マーク構造体100はシリコン基板101上に形成されたゲート酸化膜102と、ゲート酸化膜102上に形成されたゲート配線層103と、ゲート配線層103上に形成された絶縁膜104と、絶縁膜104、ゲート配線層103、ゲート酸化膜102の側面に接するように形成されたサイドウォール105とで構成され、層間絶縁膜107の上部からマーク構造体100の上部にかけては、不透明なビット線層113が、ドープトポリシリコン層1131と、タングステンシリサイド層1132のポリサイドとして構成されている。

(もっと読む)

半導体装置

【課題】非接触でデータの送受信が可能な安価な半導体装置及びその作製方法の提供する。

【解決手段】基板32に、メモリセルの有機化合物層20bに流れる電流を制御する素子であるTFT、ビット線である第1の電極層18a〜18c、ソース線17a〜17c、第2の電極層21、第1の電極層18a〜18cと第2の電極層21の間に有機化合物を含む積層(第1層(バッファ層20a)と第2層(有機化合物層20b)の積層)を設けている。有機化合物層20bは、導電性を有する有機化合物材料からなる層を単層または積層構造で設ける。導電性を有する有機化合物材料の具体例としては、キャリア輸送性を有する材料を用いることができる。集積回路部の接続電極28、電極29上にアンテナ30を形成する。

(もっと読む)

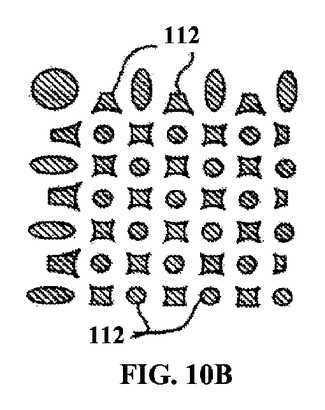

柱状構造のためのレジストフィーチャおよび除去可能スペーサピッチを倍増するパターニング法

半導体装置を製作する方法が、基板上に少なくとも1つの層を形成することと、少なくとも1つの層の上に画像形成性材料よりなる少なくとも2つの離間されたフィーチャを形成することと、少なくとも2つのフィーチャ上に側壁スペーサを形成することと、第1のフィーチャ上の第1の側壁スペーサと第2のフィーチャ上の第2の側壁スペーサとの間の空間をフィラーフィーチャで充填することと、を含む。この方法はまた、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャを互いに離間した状態で残すように、側壁スペーサを選択的に除去することと、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャをマスクとして使用して少なくとも1つの層をエッチングすることと、を含む。  (もっと読む)

(もっと読む)

メモリモジュールおよびそのレイアウト方法

【課題】 LR−DIMM方式のVLPタイプのLR−DIMMの新規の配線方法を提案する。

【解決手段】 複数のDRAMと、データを入力する2つのコネクタと、該2つのコネクタに入力されたデータをリドライブして前記複数のDRAMへ供給するバッファデバイスとが基板上に搭載されており、

前記バッファデバイスは前記2つのコネクタが両側に置かれる前記基板の中央付近に配置され、各コネクタからのデータを逆側に配置されたDRAMへ供給する。

(もっと読む)

半導体記憶装置

【課題】メモリセル面積を拡大させることなく、メモリセルにおける単位面積あたりの容量値を増やした半導体記憶装置を実現する。

【解決手段】メモリセル100は、トランジスタ101と、メモリ素子104と、第1の容量102と、第2の容量103と、を有する。第1の容量102は、トランジスタ101を構成する半導体膜108、ゲート絶縁膜114およびゲート電極109で構成され、トランジスタ101と同時に形成される。第2の容量103は、メモリ素子104を構成する電極107ならびに電極107上に形成した絶縁膜113および電極111から構成される。また、第2の容量103は、第1の容量102の直上に形成する。このように、メモリ素子104と並列に接続する、第1の容量102および第2の容量103を形成する。

(もっと読む)

低減された層間剥離特性を示す炭素系メモリ素子およびその形成方法

可逆的に抵抗を切り換える金属−絶縁物−金属(MIM)スタックを形成する方法が提供される。この方法は、縮退ドープされた半導体材料を含む第1の導電層を形成することと、第1の導電層上に炭素系可逆抵抗スイッチング材料を形成することと、を含む。また、他の態様も提供される。  (もっと読む)

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】不揮発性記憶素子と、容量素子若しくは抵抗素子とを有するシステムICの製造方法を提供する。

【解決手段】半導体基板の主面の素子分離領域5上に下部電極10cが設けられ、かつ下部電極10c上にONO膜11,12,13からなる誘電体膜を介在して上部電極19cが設けられた容量素子Cを有する半導体集積回路装置であって、半導体基板の主面の素子分離領域5と下部電極10cとの間に耐酸化性膜8、及び下部電極10cと上部電極19cとの間に耐酸化性膜12を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル間の短絡を防ぐことで、リーク電流を低減する、抵抗変化型不揮発性メモリセルを備えた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1の絶縁層11上に設けられ、かつ第1の方向に延在する第1の配線層13と、第1の配線層13上に柱状に設けられ、かつ直列に接続された非オーミック素子18と可変抵抗素子14とを含む不揮発性メモリセルMCと、メモリセルMC上に設けられ、かつ面内方向に単一の層で構成されたバリア層21と、バリア層21上に設けられ、かつ面内方向に単一の層で構成された導電層30と、第1の絶縁層11上に設けられ、かつメモリセルMC、バリア層21及び導電層30の側面を覆う第2の絶縁層20と、導電層30上に設けられ、かつ第2の方向に延在する第2の配線層22とを含む。

(もっと読む)

相変化膜の形成方法及び装置、これを利用した相変化メモリ素子の製造方法

【課題】相変化膜の形成方法及び装置、これを利用した相変化メモリ素子の製造方法を提供する。

【解決手段】本発明は、相変化膜の形成方法及び装置、これを利用した相変化メモリ素子の製造方法に関し、チャンバにソースを供給し、そして前記チャンバから前記ソースをパージし、前記ソースの供給及びパージによって前記チャンバの圧力を変動させることを特徴とする。本発明によると、所望の組成と厚さによる組成分布により、優れた相変化膜を形成することができるようされる。

(もっと読む)

半導体メモリ装置の製造方法

【課題】ON/OFF比の向上を図り、さらに低温プロセスでの製造を可能にした2端子構造の半導体メモリ装置の製造方法を提供する。

【解決手段】Si基板2上に順次SiC層3及びSi層11を積層する工程と、1段階の所定温度による熱酸化処理で、Si層11をSiO2層5に変えると共に、SiC層3のSi層11に接する界面をSiOx層4に変える工程を有する。熱酸化の温度は800℃〜950℃の範囲に設定する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】占有面積を縮小化した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、第1メタル27、第1メタル27と交差する第2メタル36、第1メタル27及び第2メタル36の交差部でそれらの間に接続されたメモリセルMCを有する単位セルアレイMATを備える。周辺領域Ar2において、所定位置からカラム方向の(4m−3)番目(mは正の整数)及び(4m−2)番目に位置する第1メタル27は、そのロウ方向の一端側にコンタクト接続部27bを有する。周辺領域において、所定位置からカラム方向の(4m−1)番目及び4m番目に位置する第1メタル27は、そのロウ方向の他端側にコンタクト接続部27aを有する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

記憶素子及び記憶装置

【課題】圧電素子を用いずに印加された圧力を記憶することができる記憶素子及び記憶装置を提供する。

【解決手段】複数の記憶素子が縦横に並べて配置されている。各記憶素子には、抵抗変化素子を備えた抵抗変化部1、及び印加された圧力に応じて流れる電流が変化する電流変化部2が設けられている。電流変化部2には、定電圧が供給される。抵抗変化部1と電流変化部2との間にはビット線BLが接続され、抵抗変化部1の他端にはトランジスタ3のソース・ドレインの一方が接続されている。トランジスタ3の他方のソース・ドレインは信号線SLに接続され、トランジスタ3のゲートはワード線WLに接続されている。

(もっと読む)

41 - 60 / 136

[ Back to top ]