Fターム[5F083ZA30]の内容

Fターム[5F083ZA30]に分類される特許

21 - 40 / 136

不揮発性記憶装置およびその製造方法

【課題】金属配線上にダイオード等の選択素子を有し、選択素子と相変化メモリ等の記憶素子とを共に積層することにより、高性能化、高信頼化を実現し、製造コストを低減する半導体記憶装置とその製造方法を提供する。

【解決手段】第1、第2、第3ポリシリコン膜119,120,121によるダイオードDIODの上に、バッファ層122、相変化材料層123が形成され、層間膜127bより熱伝導率の高いダイオードDIODの一部分を加工せずに配線上に延在させて残すことにより、ダイオードDIODで発生する熱の散逸を大きくする。また、ダイオードDIODの一部をエッチストッパとして利用することで、積層化時のコンタクト開口を一括で行うことを可能とする。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイ全体の消費電力を削減することが可能であり、且つ高集積化の可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ワード線1と、ワード線1と交差するように配置されたビット線2と、ワード線1とビット線2との各交差部に配置された絶縁膜3と、ワード線1の間及びビット線2の間を埋め込む層間絶縁膜と、ビット線1に接続され、低抵抗状態と高抵抗状態との間で遷移する抵抗変化材4とを備える。ワード線1、ビット線2、及び絶縁膜3はワード線1とビット線2との各交差部において電界効果トランジスタを構成する。電界効果トランジスタ及び抵抗変化材4はメモリセルを構成する。ビット線2は、絶縁膜を介してワード線1と対向する第1面と、この第1面とは反対側の第2面とを有する。抵抗変化材4は、第2面と接するように配置され、且つその一部が層間絶縁膜と接触している。

(もっと読む)

三次元メモリアレイ積層構造体

【課題】 改善された三次元メモリ(例えば、RRAM)アーキテクチャを提供すること。

【解決手段】 メモリデバイスが、平面基板と、平面基板の上方の複数の水平な導電性平面と、複数の水平な導電性平面と交互に配置される複数の水平な絶縁層とを備える。複数の導電性平面および絶縁層と直角である垂直な導電性列のアレイが、複数の導電性平面および絶縁層における開口部を通過する。メモリデバイスは、複数のプログラム可能なメモリ素子を備え、それぞれのメモリ素子が、水平な導電性平面の1つをそれぞれの垂直な導電性列に連結する。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

半導体メモリ装置およびその製造方法

【課題】 耐酸化性能に優れたシリコン窒化膜によってReRAMセルの側壁全面を覆うことによって、製造工程での可変抵抗膜等の酸化を抑制し、ReRAMセルの状態の安定性およびデータ保持性が高い半導体メモリ装置およびその製造方法を提供することを目的とする。

【解決手段】 ReRAMセルは、例えば、導電性材料からなる第1電極11、多結晶シリコンからなるダイオード12、導電性材料からなる第2電極13、遷移金属酸化膜からなる可変抵抗膜14、および導電性材料からなる第3電極15から構成されるものとする。また、ReRAMセルの側壁全面に、シリコン窒化膜を主成分とする側壁絶縁膜20が形成されており、更にその外側にはシリコン酸化膜を主成分とするセル間絶縁膜21が形成されている。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

抵抗変化型メモリ

【課題】抵抗変化型メモリの動作特性を向上する。

【解決手段】本発明の一態様に関わる抵抗変化型メモリは、複数のブロックBKが設けられるメモリセルアレイと、複数のブロック内に設けられる複数の抵抗変化型記憶素子と、複数のブロック内に設けられ、抵抗変化型記憶素子に接続される第1及び第2の配線BL,WLと、前記複数のブロックにおいて動作の対象となる選択ブロック及び前記選択ブロックを除く複数の非選択ブロックの状態をそれぞれ制御する制御回路と、を具備し、

制御回路は、選択ブロックを動作させている期間中に、非選択ブロック内の第1及び第2の配線BL,WLに電位VUXを供給する。

(もっと読む)

半導体記憶装置

【課題】抵抗変化メモリセルに充分な電流を流すことができる半導体記憶装置を提供する。

【解決手段】互いに交差するように形成されたワード線WLj及びビット線BLiと、これら配線の各交差部に配置され、ダイオードDIと可変抵抗素子VRとを直列接続してなるメモリセルMCを含むメモリセルアレイとを備える。ダイオードDIは、n+型層D3とp+型層D1とを有する。n+型層D3の少なくとも一部がシリコン−カーバイド混合物(Si1−xCx(0<x<1))で構成され、p+型層D1がシリコン(Si)で構成されている。

(もっと読む)

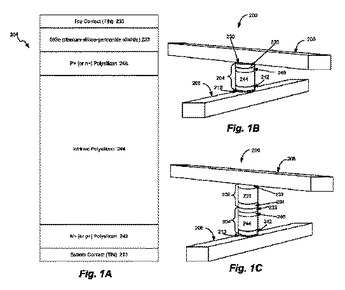

低コンタクト抵抗を有する3次元ポリシリコンダイオードおよびその形成方法

半導体p−i−nダイオードおよび半導体p−i−nダイオードを形成する方法を開示する。一形態において、一の導電型(p+またはn+の一方)を有するようにドープされた領域と、p−i−nダイオードへの電気コンタクトの間に、SiGe領域が形成される。SiGe領域は、コンタクト抵抗を低減する働きをすることができ、順バイアス電流を増加させることができる。ドープされた領域は、ドープされた領域がSiGe領域とダイオードの真性領域との間に存在するように、SiGe領域の下方を伸びている。p−i−nダイオードは、シリコンから形成することができる。SiGe領域の下方のドープされた領域は、付加されたSiGe領域によって逆バイアス電流が増加することを防止する働きをすることができる。一実施形態では、メモリアレイ内の上向きのp−i−nダイオードの順バイアス電流が、下向きのp−i−nダイオードの順バイアス電流に実質的に一致するように、SiGeは形成される。これらのダイオードが3Dメモリアレイの読み出し/書き込み材料に用いられた場合に、より良いスイッチング結果を達成することができる。  (もっと読む)

(もっと読む)

半導体集積回路およびその動作方法

【課題】スタンバイ時の保持データ量の変化に対応すること。

【解決手段】半導体集積回路は、ロジック回路logicと、複数のSRAMモジュール2、3を具備する。複数のSRAMモジュールは、ロジック回路と独立に電源制御が可能とされ、複数のSRAMモジュールの間で独立した電源制御が可能とされる。具体的には、各SRAMモジュールの電位制御回路の一方の端子arvssと他方の端子vssmはセルアレーcell_arrayとローカル電源線vssmに接続される。一方のSRAMモジュール2と他方のSRAMモジュール3とのローカル電源線vssmは、共有ローカル電源線vssm22によって共有されている。一方と他方のSRAMモジュール2、3の一方と他方の電源スイッチPWSW22、PWSW23とは、共有ローカル電源線vssm22に共通に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】拡散層と拡散層に接続されるコンタクトとの接触抵抗を低減した半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置の製造方法は半導体基板にピラー部を設ける工程と、前記ピラー部の基端部近傍に第1の不純物拡散領域を形成する工程と、ピラー部の側面を被覆する第1の絶縁膜を形成するとともに、第1の絶縁膜を介してピラー部の側面に対向する電極層を形成する工程と、ピラー部及び第1の絶縁膜の周囲を埋める第2の絶縁膜を形成する工程と、第1の層間膜を除去して前記ピラー部の先端面を露出させる工程と、ピラー部の先端部に第2の不純物拡散領域を形成する工程と、第1の絶縁膜をエッチングして前記ピラー部の先端部の側面を露出させる工程と、ピラー部の先端面及びピラー部の先端部の側面を覆うようにコンタクトプラグを形成する工程と、を具備してなる。

(もっと読む)

抵抗変化メモリ

【課題】可変抵抗素子の抵抗値ばらつきに起因する誤動作を抑制する抵抗変化メモリを提供する。

【解決手段】抵抗変化メモリは、第1の電極14、抵抗変化膜15、及び第2の電極16が積層された積層構造からなり、かつ記憶データに基づいて低抵抗状態又は高抵抗状態を取り得る可変抵抗素子17と、可変抵抗素子17の側面に設けられた絶縁膜19と、絶縁膜19の側面に設けられた導電膜からなり、かつ可変抵抗素子17に並列接続された固定抵抗素子20とを含む。

(もっと読む)

位置識別マーク、および半導体集積回路

【課題】メタル配線層や絶縁層を剥離した場合においても、半導体基板上におけるメモリセル等の物理的な位置を容易に確認できる、位置識別マークを提供する。

【解決手段】本発明の位置識別マークは、拡散層で形成される直線状の基板電位供給用パターン11の側面部(辺側)に、凹凸形状を設けて形成される。そして、基板電位供給用パターン11の一方の側(図1で上側)に、Y(column)方向の個数(左側から何個目の64kブロックかを示す個数)、もう一方の側(図1で下側)に、X(Row)方向の個数(下側から何個目の64kブロックかを示す個数)を示す位置識別マークが形成される。この位置識別マークは、1〜64の間の数値を示すように形成される。図1に示す例では、1,5,10の単位で、幅W・長さLを変えた凸状のパターンa,b,c等を配置する。

(もっと読む)

抵抗変化型不揮発性メモリ素子、および、抵抗変化型不揮発性メモリ素子の製造方法

【課題】高集積化および低消費電力化可能な抵抗変化型不揮発性メモリ素子を提供する。

【解決手段】メモリ素子10は、基板1上に少なくとも電極2aおよび電極2bが配置されており、電極2aおよび電極2bの間に、MgOなどの無機酸化物ナノワイヤにp型半導体であるシェル層が形成されたナノワイヤ構造体3が形成されている。無機酸化物にp型酸化物半導体であるシェル層が形成されているため、製造されたナノワイヤ構造体3の表面が酸化され難くなる。p型半導体であるシェル層を構成する無機酸化物としては、NiO、CoO、CuO、Ta2O5,HfO2などである。

(もっと読む)

不揮発性半導体記憶装置

【課題】消費電力を低減させ且つ誤動作を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】可変抵抗層63は、炭素C、及び元素群Aから選ばれる少なくともいずれか1種類以上の元素を含む第1化合物631と、化合物群G2から選ばれる少なくともいずれか1種類以上の第2化合物632とを含む混合体にて構成されている。可変抵抗層63中での第1化合物631の濃度は、30vol.%以上であり且つ70vol.%以下である。元素群G1は、水素、ボロン、窒素、シリコン、及びチタンを含む。化合物群G2は、酸化シリコン、酸窒化シリコン、窒化シリコン、窒化炭素、窒化ホウ素、窒化アルミニウム、アルミニウム酸化物、炭化珪素を含む。

(もっと読む)

犠牲材を使用してダマシンダイオードを作る方法

半導体デバイスを作る方法は、下位層の上にシード材を備える第1の層を形成することと、シード材とは異なる犠牲材を備える第2の層を第1の層の上に形成することと、第1の層および第2の層を複数の分離したフィーチャとなるようにパターニングすることと、複数の分離したフィーチャの間に絶縁充填材を形成することと、絶縁充填材の中に複数の開口部を形成して、複数の開口部の中でシード材を露出させるため、分離したフィーチャから犠牲材を除去することと、複数の開口部の中で露出されたシード材の上に半導体材を成長させることと、を含む。  (もっと読む)

(もっと読む)

密封型半導体記録媒体及び密封型半導体記録装置

【課題】 密封型半導体記録媒体及び密封型半導体記録装置に関し、無線により電力を給電するとともに、相互干渉なしに無線でデータ通信を高速に行うことが可能な密封された高信頼性の半導体メモリを低コストで提供する。

【解決手段】 少なくとも1枚の半導体基板に最大辺が20mm以下のサイズの複数の読出専用メモリブロックを互いに電源配線を共有しない状態で設け、前記各読出専用メモリブロックに電力受給用コイルとデータ通信用コイルを備えるとともに、前記各読出専用メモリブロックに互いに異なったデータを書き込む。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作電圧が低い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置の抵抗可変素子を作製する際に、タングステンからなる導電膜31上にチタンシリコン窒化物からなる非晶質膜32を堆積させ、その上にチタン窒化物からなる多結晶導電膜33を堆積させることにより、下部電極25を形成する。次に、ニッケル酸化物からなる抵抗可変膜26を堆積させ、その後加熱処理を行い、多結晶導電膜33の結晶を成長させると共に、多結晶導電膜33に含まれるチタンと抵抗可変膜26に含まれる酸素とを反応させる。これにより、多結晶導電膜33の結晶粒が不均一に成長して突起34が形成されると共に、酸化膜35が形成されることにより、抵抗可変膜26の下層部分26aに酸素欠損が生成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】消費電力の増大に対して有利な半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルをそれぞれ備え、半導体基板35上に複数積層される三次元構造の複数のメモリセルアレイ10と、半導体基板35中に設けられる第1導電型の第1ウェル43と、第1ウェル43中において第1ウェル43の底面よりも浅い位置に底面を有し、半導体基板35中に埋め込み配置される素子分離絶縁膜STIと、第1ウェル43中において第1ウェル43の底面よりも浅い位置に底面を有し(DP<DN)、素子分離絶縁膜STIの少なくとも一部の底面に沿って設けられ、第2導電型の不純物によって形成される第2ウェル44と、第1ウェルと電気的に接続されるコンタクト配線CLとを具備する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】製造工程による抵抗変化層の特性劣化を改善する抵抗変化層を用いた不揮発性記憶装置を提供する。

【解決手段】基板11上に形成された下層配線15と、下層配線15上の少なくとも一部に形成された抵抗変化層16と、下層配線15と抵抗変化層16とを含む基板11上に形成された層間絶縁層17と、層間絶縁層17を貫通して抵抗変化層16に接続するように形成されたコンタクトホール26と、抵抗変化層16に接続し、コンタクトホール26内に形成された埋め込み電極19と、層間絶縁層17上に埋め込み電極19と接続し、下層配線15に対して交差する上層配線20とを備え、抵抗変化層16は少なくとも酸素不足型の遷移金属酸化物を含み、かつコンタクトホール26が接続する領域の抵抗変化層16の表層部分がコンタクトホール26と接続する領域以外の抵抗変化層16の表層部分に比べて凹んだ形状になっている。

(もっと読む)

21 - 40 / 136

[ Back to top ]