Fターム[5F092AA12]の内容

Fターム[5F092AA12]に分類される特許

101 - 120 / 181

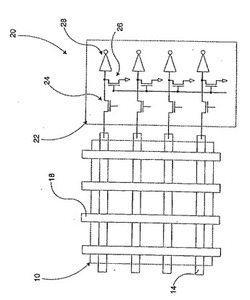

電気的にプログラム可能な抵抗特性を有するクロスポイントメモリ

【課題】外部影響(特に電気的パルス)により電気的抵抗が変化する特性を有する材料を用いた不揮発性メモリの大容量化を可能としたクロスポイントメモリデバイスを提供すること。

【解決手段】下部電極と上部電極とのクロスポイントに対応するビット領域は、互いに交差するように配列された下部電極と上部電極との間に配置されたアクティブ層の一部である。アクティブ層は、電気信号に応答して変化する抵抗性を有し得る材料である。下部電極と上部電極との間を通る電気信号は、ビット領域を通過する。ビット領域では、電気信号に応答して抵抗率を変化させる。

(もっと読む)

マイクロ発振素子および検出素子

【課題】電子回路に用いられるマイクロ波発振素子およびマイクロ波検出素子を高効率化、小型化する。

【解決手段】マイクロ波発生素子は磁化固着層4と、電流を狭窄する機能とスピン偏極電流によりマイクロ波を発振させる機能を有する領域を複数個有する層5と、電流を狭窄する機能とスピン偏極電流によりマイクロ波を発振させる機能を有する領域の磁化の向きを空間的に非一様にする機能を有する層6とを備えており、積層方向に電流を流すことにより空間的に非一様な磁化の向きを有する領域にスピン偏極電流が流れるため、電流狭窄構造薄膜中の磁化に対してスピントランスファートルクが働き、マイクロ波を発振する。

(もっと読む)

磁気ヘッド製造方法

【課題】 本発明は、磁気記録再生装置の磁気ヘッドに関し、より詳細にはギャップ長の精度を下げることなく、コア幅の微細化を達成できる磁気ヘッド製造方法に関する。

【解決手段】 本発明の磁気ヘッド製造方法は、磁気抵抗効果膜の上にリフトオフ層とエッチング耐性層を成膜するリフトオフ層成膜手順と、リフトオフ層とエッチング耐性層とを所望のマスクパターンに形成するマスクパターン形成手順と、磁気抵抗効果膜をエッチングして磁気抵抗効果素子を形成する磁気抵抗効果素子形成手順と、磁気抵抗効果素子の上に絶縁層と磁区制御層とを成膜する磁区制御層成膜手順と、成膜後にリフトオフにより磁気抵抗効果素子の上面を露出するリフトオフ手順とで構成する。

(もっと読む)

リードヘッド、磁気ヘッドおよび磁気記憶装置

【課題】リード素子が小型化した場合でもリードヘッドの特性を劣化させることなく、磁気記憶媒体の記録密度の増大に好適に対応することができるリードヘッド、磁気ヘッドおよび磁気記憶装置を提供する。

【解決手段】フリー層を備えるリード素子10と、前記フリー層を磁区制御する磁区制御層20a、20bとを備え、前記磁区制御層20a、20bは、Fe、Co、Niの少なくとも一種を含む軟磁性材からなり、該磁区制御層20a、20bのコア幅方向の長さa、ハイト方向の長さbの比a/bが5以上、磁区制御層20a、20bのハイト方向の長さbが100nm以下に設けられていることを特徴とする。

(もっと読む)

強磁性物質のドメイン構造および多重状態を用いた磁気記憶素子

【課題】磁気情報の記録される強磁性半導体層(magnetic Semiconductors、MS)自体をセンサー層として同時に利用することにより、磁気記録素子の構造を簡単にして工程を短縮し、生産単価を節減するばかりか、さらに多重ドメイン状態を利用した巨大な平面ホール効果(Planar Hall Effect)または磁気抵抗(Magnetoresistance)を測定して多重状態の情報を記録することができる記憶素子を提供する。

【解決手段】基板110と、前記基板110上に形成され、多重ドメイン状態を用いて多重の状態を平面ホール効果または磁気抵抗値を通じて貯蔵しセンシングする強磁性半導体層120と、前記強磁性半導体層上に形成された絶縁膜130と、前記絶縁膜上に形成された第1電流ライン140と、前記第1電流ライン上に形成された絶縁膜150と、前記絶縁膜上に形成された第2電流ライン160と、を含む。

(もっと読む)

CPP磁気リード・ヘッド及びその製造方法

【課題】特性に優れたCPPリード・ヘッドを得る。

【解決手段】本発明の一実施形態において、CPPリード・ヘッド11は、磁気抵抗センサ112の両側にハードバイアス膜115を有する。ハードバイアス膜115は、積層された下層硬磁性層151と上層硬磁性層152とを有する。上層硬磁性層152の飽和磁束密度及び残留磁束密度は、下層硬磁性層151よりも大きい。下層硬磁性層151の保磁力は上層硬磁性層152の保磁力よりも大きい。上部シールド113、自由層215と重なる平坦部を有し、その平坦部の幅は自由層215よりも大きい。磁気特性の異なる硬磁性層でハードバイアス膜を形成することで、シールド間隔を小さくすると共に、シールドを平坦化することができる。

(もっと読む)

磁気トンネル素子、これを利用した半導体装置およびその製造方法

【課題】スピン平行/反平行状態の2値に加えて、リセット/セット状態の書き込みを可能とするMTJ素子を提供する。

【解決手段】磁気トンネル素子は、一対の強磁性層と、前記強磁性層の間に挟まれるトンネルバリア層とを含み、第1の抵抗状態と、前記第1の抵抗状態よりも高抵抗の第2の抵抗状態の間を遷移する第1機能と、前記第1の抵抗状態より低抵抗の第3の抵抗状態と、前記第2の抵抗状態よりも高抵抗の第4の抵抗状態の間を遷移する第2機能と、を有する。

(もっと読む)

半導体磁気抵抗素子およびその設計方法

【課題】磁気抵抗素子の長さ方向、すなわち電極間方向と直交する方向の半導体動作層の幅Wを小さくしても、従来の大きな幅Wと同程度の高い磁気抵抗変化率を実現すること。

【解決手段】基板上に形成された薄膜状半導体動作層と、半導体動作層上の少なくとも2つの端部に配置された入出力電極と、入出力電極間の半導体動作層上で、入出力電極間に延在する半導体層の延在方向と直角方向に延在する形で、半導体層の延在方向に一定間隔をおいて、配置された複数の短絡電極とを有する半導体磁気抵抗素子において、入出力電極間に延在する半導体層の延在方向と直角方向の半導体動作層の幅が60μm以下、短絡電極の、半導体層の延在方向の長さが5μm以下、半導体動作層の幅をW、一定間隔の複数の短絡電極間の距離をLとしたとき、LとWの比であるL/Wが0.3以下とする。ここで、L/Wが0.1以上、短絡電極の長さが2μm以上であることが好ましい。

(もっと読む)

薄膜磁性体記憶装置

【課題】簡易な回路構成で書込データレベルに応じたデータ書込電流を供給可能な薄膜磁性体記憶装置の構成を提供する。

【解決手段】各メモリセル列において、ビット線BLは、一端側に相当するノードNaおよび他端側に相当するノードNbにおいて、駆動スイッチをそれぞれ介してデータバスDBaおよびDBbと接続され、中間ノードNmにおいて、駆動スイッチを介して逆相データバス/WDBと接続される。選択列のビット線において、選択メモリセルと中間ノードとの位置関係に応じて、中間ノードの駆動スイッチと、一端側および他端側の一方の駆動スイッチとがオンすることによって、データ書込電流が流される。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】 小面積で低消費電力の読み出し回路を有する磁気ランダムアクセスメモリを提供する。

【解決手段】 第1、第2MR素子MRM、MRRは、低、高抵抗状態の定常状態を取り得る。第1MOSFETQn1は、一端を第1MR素子と接続され、ゲート端子に第1電位を印加される。第2MOSFETQn2は、一端を第2MR素子と接続される。センスアンプSAは、第1、第2MOSFETの各他端を流れる電流の差を増幅する。定電流回路Iは、低抵抗状態の第1MR素子を流れる電流と、高抵抗状態の第1MR素子を流れる電流との間の値を有する参照電流を出力する。第3MOSFETQn3は、一端において参照電流を供給され、一端をゲート端子と接続される。第1抵抗素子MRP1は、第3MOSFETの他端と接続され、第2MR素子と実質的に同じ抵抗値を有する。第2MOSFETのゲート端子には、第3MOSFETのゲート端子と同じ電位が印加される。

(もっと読む)

半導体装置

【課題】FeRAMと特定のセンサとが混載された新規な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置1000は、半導体基板10と、前記半導体基板10に形成されたトランジスタ14と、前記トランジスタ14を覆う層間絶縁層16と、前記層間絶縁層16の上方に形成された強誘電体キャパシタ30であって、第1電極34と、強誘電体層36と、第2電極38とを有する強誘電体キャパシタ30と、前記強誘電体キャパシタ30を覆う、前記層間絶縁層16とは別の層間絶縁層40と、前記半導体基板10の上方に形成されたセンサであって、圧力センサ、焦電センサまたは磁気センサのいずれかであるセンサ100と、を含む。

(もっと読む)

横方向のスピン移動を用いた低ノイズ磁気センサ

本発明は、ピン層である第1の磁化が固定された磁気層(410)と、外部磁場がない場合、前記ピン層の磁化に対して実質的に垂直な磁化を有し、磁気脱共役のために第1の分離層(420)によって前記ピン層から分離されている高感度層であるフリー磁化磁気層(430)とを備える磁気抵抗センサに関する。前記センサは、横方向のスピン移動を制御する役割を果たし、前記分離層の反対側で前記高感度層の横に位置する横結合層(440)を更に備える。 (もっと読む)

磁気抵抗ラム

【課題】ワードラインとP−Nダイオードとの間にMTJ(Magnetic Tunnel Junction)を結合して2つ以上のデータを記憶させ、構造が簡単でセルサイズが小さい磁気抵抗ラム(MRAM)用セルを具現する。

【解決手段】半導体基板にドーピングされたN+領域と、前記N+領域のライン上にドーピングされたP型の不純物領域でなるP−Nダイオード、前記P型の不純物領域の上に積層されたバリヤー導電層、前記バリヤー導電層の上部に積層されたMTJ(Magnetic Tunnel Junction)、及び前記MTJの上部に積層されたワードライン、を備えるMRAMセルを含み、前記ワードラインに印加される電圧の大きさに従って前記MTJに流れる電流を制御し、前記MRAMセルにデータを書き込み、読み出すことを特徴とする。

【選択図】図3  (もっと読む)

(もっと読む)

磁気抵抗素子及びその製造方法

【課題】 磁性層同士のショートを防ぐ。

【解決手段】 磁気抵抗素子10は、磁化の方向が固定された第1の固定層14と、第1の非磁性層15とが順に積層された第1の積層体と、第1の積層体上に設けられ、かつ磁化の方向が変化する自由層16と、第2の非磁性層17と、磁化の方向が固定された第2の固定層18とが順に積層された第2の積層体と、第2の積層体の側面に接しかつ第2の積層体を囲むように設けられ、かつ絶縁体からなる側壁20とを具備する。そして、第1の積層体は、その側面がほぼ垂直である。第2の積層体は、上に向かって細くなるテーパー形状を有する。

(もっと読む)

データストレージデバイスおよびデータストレージ方法

各データ担持ナノワイヤが、そのナノワイヤの全長に沿って複数の交差するナノワイヤを有して、磁壁ピン留めサイトを構成する交差接合部を形成する。データは、交差するナノワイヤとの整列と反整列の間で交番する磁界の作用の下で磁区を動かすことによって、各データ担持ナノワイヤを通って送られる。データは、上向きキラリティ横磁壁および下向きキラリティ横磁壁が、0および1を符号化するのに使用されて、磁壁のキラリティに符号化される。データは、事前定義されたキラリティの磁壁を有する磁区を核形成することができる適切な核形成磁界発生器を使用して、各ナノワイヤの中にクロック制御されて入れられる。データは、このキラリティを検知する適切な磁界センサを使用して、各ナノワイヤからクロック制御されて出される。  (もっと読む)

(もっと読む)

磁気抵抗効果素子、磁気ランダムアクセスメモリ、電子カード及び電子装置

【課題】メモリセルを微細化してもビット情報の高い熱擾乱耐性を保ち、大容量化を実現する。

【解決手段】磁気抵抗効果素子は、スピン偏極したスピン偏極電子を磁性体に流すことで情報が記録される磁気抵抗効果素子であって、磁性材料からなり、膜面に対して垂直方向に向く第1の磁化を有する固定層12と、磁性材料からなり、膜面に対して垂直方向に向く第2の磁化を有し、スピン偏極電子の作用により第2の磁化の方向が反転可能な記録層11と、固定層と記録層との間に設けられ、固定層に対向する第1の面と記録層に対向する第2の面とを有する非磁性層TBと、非磁性層の第1の面と固定層との間に設けられ、Fe、Co、Niのうち1つ以上の元素を含む第1の磁性金属層18と、非磁性層の第2の面と記録層との間に設けられ、Fe、Co、Niのうち1つ以上の元素を含む第2の磁性金属層19とを具備し、第2の磁性金属層の膜厚は、第1の磁性金属層の膜厚より薄い。

(もっと読む)

磁気記憶装置

【課題】比較的簡素な構成で一対の電流配線を要することなく効率良く確実な磁化反転を可能とし、装置の更なる微小化を可能とする信頼性の高い磁気記憶装置を実現する。

【解決手段】少なくとも磁化反転層4の両側面、ここでは絶縁層3、磁化反転層4及びキャリア注入層5からなる積層体の両側面に、絶縁層6及び非磁性金属層、ここではRu層7を介して、一対の磁化制御層8を設ける。キャリア注入層5は、SrTiO3から、磁化制御層8はGdFeCo,GdDyFeCo,GdNdFeCo等の希土類遷移金属合金から形成する。

(もっと読む)

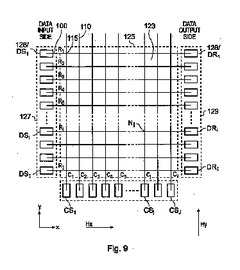

スピントルクMRAMセルアレイ、スピントルクMRAM装置およびスピントルクMRAMセルアレイのプログラミング方法

【課題】スピントルクMRAMセルアレイ中に引き回される配線が占める領域を小さくしたスピントルクMRAMセルアレイ、スピントルクMRAM装置およびスピントルクMRAMセルアレイのプログラミング方法を提供する。

【解決手段】スピントルクMRAMセルアレイ405は、スピントルクMRAMセル100(以下「MRAMセル100」という。)を横方向と縦方向に配列したものである。ビット線305は、各縦方向に沿って配置され、各MRAMセル100に接続される。ソース選択線330は、ビット線305に対して直交し、且つ、横方向に配列されたMRAMセル100を2行1組にした対に対応して配置され、この対を構成しているMRAMセル100と接続される。MRAMセル100には、第1ステップで第1論理レベル(0)が書き込まれ、第2ステップで第2論理レベル(1)が書き込まれる。

(もっと読む)

MRAMデバイスおよびその形成方法

【課題】より高いスピン角運動量の移動効率が得られるMRAMデバイスを提供する。

【解決手段】MTJ構造100は、ワード線とビット線との交差点においてそれらの間に配置されている。MTJ構造100は、基体1の上に、反強磁性層2、ピンド層3、非磁性層4、リファレンス層5、トンネルバリア層6、フリー層7、非磁性層8、ドライブ層9、非磁性層10、ピンド層11、反強磁性層12が順に積層されたものである。フリー層7は、トンネルバリア層6の側から順に、第1強磁性層76、第1非磁性導電層75、第2強磁性層74、第2非磁性導電層72、第3強磁性層70を備える。第2強磁性層74は、第1強磁性層76と強磁性的に交換結合すると共に、第3強磁性層70と反強磁性的に交換結合している。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセルの微細化を図る。

【解決手段】半導体記憶装置は、第1及び第2の部分13a、13bを有し、第1及び第2の部分は第1の方向に第1のスペースS1を有する第1の抵抗変化素子MTJと、第1の抵抗変化素子と第1の方向に距離Fを有して配置され、第3及び第4の部分13a’、13b’を有し、第3及び第4の部分は第1の方向に第2のスペースS2を有し、第1及び第2のスペースは距離より短い第2の抵抗変化素子MTJ’とを具備する。

(もっと読む)

101 - 120 / 181

[ Back to top ]